Fターム[5J056BB04]の内容

Fターム[5J056BB04]に分類される特許

1 - 6 / 6

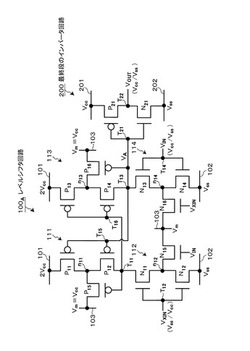

レベルシフタ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、走査回路の最終段のインバータ回路の入力電圧の振幅を増大させることが可能なレベルシフタ回路を提供する。

【解決手段】第1固定電源側の2つのトランジスタ回路が第1導電型のトランジスタから成り、第2固定電源側の2つのトランジスタ回路が第2導電型のトランジスタから成るとともに、第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成るレベルシフタ回路において、一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、エンファシスの有無により消費電流が変動する問題があった。

【解決手段】本発明の半導体装置は、抵抗値を、エンファシスモードにおいて第1の抵抗値とし、非エンファシスモードにおいて第1の抵抗値よりも小さな第2の抵抗値とする可変抵抗30と、出力インピーダンスを、エンファシスモードにおいて第3の抵抗値とし、非エンファシスモードにおいて前記第3の抵抗値よりも大きな第4の抵抗値とする第1の駆動部10と、出力インピーダンスを、エンファシスモードにおいて第5の抵抗値とし、非エンファシスモードにおいて第5の抵抗値よりも大きな第6の抵抗値とする第2の駆動部11と、入力信号に応じて第1、第2の駆動部の導通状態を制御すると共に、エンファシスモードと非エンファシスモードとにおいて第1、第2の駆動部の出力インピーダンスと可変抵抗の抵抗値を切り換える制御部と、を有する。

(もっと読む)

レベル変換バススイッチ

【課題】レベル変換時の信号の立ち上がりを速くすることのできるレベル変換バススイッチを提供する。

【解決手段】実施形態のレベル変換バススイッチは、低電圧レベル信号が伝送される低電圧レベル信号線と高電圧レベル信号が伝送される高電圧レベル信号線との間に、低電圧レベルの制御信号により導通が制御されるMOSトランジスタ型のスイッチ1が接続され、高電圧レベル信号線と高電圧電源線VccBとの間に、プルアップ抵抗2が接続される。このレベル変換バススイッチでは、加速回路3が、高電圧レベル信号の立ち上がりをプルアップ抵抗2による立ち上がりよりも速くし、加速期間制御回路4が、加速回路3の作動期間を制御する。

(もっと読む)

ドライバ回路

【課題】高速なデータパターンの時のみ周波数特性を改善して、所望の振幅を得ることが可能な送信側ドライバ回路を提供する。

【解決手段】第1のプルアップ抵抗回路P41、第3のプルアップ抵抗回路P43、第1のプルダウン抵抗回路N41、第3のプルダウン抵抗回路N43の抵抗値を第1の制御信号(SDATAP、SDATAM、DEMPHPP、DEMPHMN、DEMPHPN、DEMPHMP)に応じて変化させ、第2のプルアップ抵抗回路P42、第4のプルアップ抵抗回路P44、第2のプルダウン抵抗回路N42、第4のプルダウン抵抗回路N44の抵抗値を第2の制御信号(EMPHPP、EMPHPMN、EMPHPN、EMPHMP)に応じて変化させる

(もっと読む)

インバータ素子及びその動作方法

【課題】本発明は、インバータ素子及びその動作方法を提供することを目的とする。

【解決手段】電源節点と接地部との間に接続された少なくとも1つの第1トランジスタが与えられ、該少なくとも1つの第1トランジスタは、第1ゲート及び第1ターミナルを備え、第1ゲート及び第1ターミナルは、昇圧節点で昇圧電圧を調節するために内部的に容量結合され、第1ターミナルは、第1トランジスタの第1ソース及び第1ドレインのいずれか一つである。

(もっと読む)

電子デバイス及び集積回路

本発明のCMOS回路(CC)を有する電子デバイスは、第1及び第2のPMOSトランジスタ(P1,P2)と第1及び第2のNMOSトランジスタ(N1,N2)とを有する第1のドライバ回路(10)を備える。本電子デバイスは、更に、第3及び第4のPMOSトランジスタ(P3,P4)と第3及び第4のNMOSトランジスタ(N3,N4)とを有する第2のドライバ回路(20)を備える。第2のドライバ回路(20)は、第1のドライバ回路(10)に対してコンプリメンタリであり、第1のドライバ回路(10)とは逆方向にスイッチングする。第2及び第4のPMOSトランジスタ(P2,P4)のゲートは、第1のバイアス電圧(REFp)に結合され、第2及び第4のNMOSトランジスタ(N2,N4)のゲートは、第2のバイアス電圧(REFn)に結合される。第1のコンデンサ(C3)は、第4のPMOSトランジスタ(P4)のゲート−ドレイン間に結合され、第2のコンデンサ(C4)は、第4のNMOSトランジスタ(N4)のゲート−ソース間に結合される。  (もっと読む)

(もっと読む)

1 - 6 / 6

[ Back to top ]