Fターム[5J056CC27]の内容

Fターム[5J056CC27]に分類される特許

1 - 8 / 8

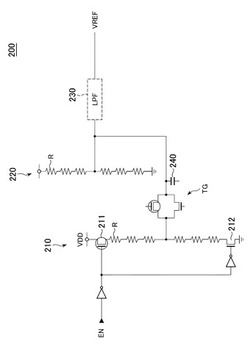

半導体装置

【課題】キャリブレーション回路に用いる基準電位生成回路を改良する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ110と、基準電位VREFを生成する基準電位生成回路200と、キャリブレーション端子ZQに現れる電位と基準電位VREFとを比較する比較回路151と、比較回路151による比較の結果に基づいてレプリカバッファ110の出力インピーダンスを変化させるコントロール回路140とを備える。基準電位生成回路200は、イネーブル信号ENに応答して活性化される電位発生部210と、イネーブル信号ENに関わらず活性化される電位発生部220とを含み、電位発生部210の出力ノードと電位発生部220の出力ノードが比較回路151に共通接続されている。これにより、イネーブル信号ENが活性化する前に正しく基準電位VREFを出力することができる。

(もっと読む)

クロック供給回路

【課題】動作条件が厳しい場合でも、クロックゲーティング信号を含む経路のタイミング違反の発生を防ぐことができるクロック供給回路を提供する。

【解決手段】クロック供給回路1は、クロックツリー13からのクロック信号に基づく信号を複数のインバータ回路32a及び32bによって遅延させ、複数のインバータ回路32a及び32bによる遅延量に基づいてタイミング違反を推定するモニタ回路17を有する。さらに、クロック供給回路1は、モニタ回路17の推定結果に基づいて、組合せ回路16により生成されたクロックゲーティング信号を制御するOR回路18と、OR回路18の出力信号に基づいて、クロック信号を供給又はクロック信号の供給を停止するクロックゲーティング回路12とを有する。

(もっと読む)

プリエンファシス回路

【課題】 簡単な構成でプリエンファシス信号を生成することが可能なプリエンファシス回路を実現する。

【解決手段】 信号の変化点で振幅を大きくするプリエンファシス回路において、差動入力信号を差動電流出力に変換する第1のトランスコンダクタンスアンプと、ハイパスフィルタ回路と、このハイパスフィルタ回路を介した前記差動入力信号を差動電流出力に変換する第2のトランスコンダクタンスアンプと、2つの前記差動電流出力をそれぞれ加算して電圧変換する第1及び第2の抵抗とを設ける。

(もっと読む)

論理レベル出力集積回路

【課題】ワイヤード接続されたとしても安定した論理レベルを出力端子から出力できるようにする。

【解決手段】抵抗R4およびR5が、出力回路13(A)のトランジスタM2のドレイン−ソース間と、出力回路13(B)のトランジスタM3のドレイン−ソースを通じて流れる電流の通電経路に直列に接続して構成されている。抵抗R4およびR5の抵抗値が、出力回路13(A)のトランジスタM2がオンしている間において出力回路13(B)のトランジスタM3がオンしたときのオン抵抗値よりも1桁〜2桁高い値に設定されている。

(もっと読む)

半導体集積回路の配置配線方法及び半導体集積回路の配置配線支援プログラム

【課題】クロックゲート回路の多重化及び統合によって非同期信号パスにおける故障検出率が低下せず且つ故障検出論理に変更を生じさせない半導体集積回路の配置配線方法を提供する。

【解決手段】クロックツリー経路に複数のクロックゲート回路を配置したとき、クロックゲート回路が出力するクロック信号のスキューを許容範囲に収めるためにクロックゲート回路の多重化又は統合を行うかを判定する。統合を行うときは、前記統合によって廃止するクロックゲート回路(CGC2)に代えて、当該クロックゲート回路のクロックイネーブル信号(CEN)の入力端子を故障検出経路まで接続する回路要素(3)を配置する。前記多重化を行うときは、多重化によって追加するクロックゲート回路に新たなスキャンラッチを割り当てて接続する。

(もっと読む)

ドライバ回路

【課題】 高速シリアル通信システムにおいて用いられる、消費電力を低減することが可能な送信側ドライバ回路を提供する。

【解決手段】 差動信号を伝送する一対の伝送線路に接続された第1及び第2の各出力端子を備え、外部から入力されたデータ信号を差動信号に変換し第1及び第2の各出力端子に出力するドライバ回路において、第1の出力端子は、第1のプルアップ抵抗回路を介して所定の電源電圧に接続されると共に、第1のプルダウン抵抗回路を介して接地電圧に接続され、第2の出力端子は、第2のプルアップ抵抗回路を介して電源電圧に接続されると共に、第2のプルダウン抵抗回路を介して接地電圧に接続され、第1及び第2の各プルアップ抵抗回路、並びに第1及び第2の各プルダウン抵抗回路は、データ信号に応じて抵抗値がそれぞれ変化する。

(もっと読む)

インピーダンス調整回路及び集積回路装置

【課題】 チップ内のバラツキに起因するインピーダンスの調整精度の低下を抑制できるインピーダンス調整回路及びこれを搭載した集積回路装置を提供する。

【解決手段】 NMOS用インピーダンス調整回路において、外部の基準抵抗及びNMOSアレイによる分圧電位Vinと参照電位VREFnとを比較する比較回路を設け、NMOSアレイがこの比較結果に基づいて出力バッファ回路のインピーダンスをシミュレートするようにする。比較回路14には差動回路D1乃至D3を設け、2入力のナンドゲートNAND21乃至NAND23及び3入力のナンドゲートNAND24が、差動回路D1乃至D3の出力値の多数決をとって比較回路14から出力するようにする。

(もっと読む)

バス線上のデジタル信号のデューティサイクルへの妨害の影響を低減するドライバ回路

デジタル通信線(14)に結合された出力端子を有し、デジタル通信線における電位のデジタル信号への変化およびデジタル信号レベルからの変化を駆動するためのドライバ回路(12)を含む電子回路である。前記ドライバ回路(12)は、デジタルレベルへの変化中およびデジタルレベルからの変化中に、次第に増加するドライブ強度および次第に減少するドライブ強度をそれぞれ選択する選択信号を発生する制御回路(120)と、前記選択信号を受信するために前記制御回路に結合された電流制御入力および前記デジタル通信線に結合された電流供給出力端子を有する可制御電流供給回路(122,124)と、前記デジタル通信線に結合された入力端子および前記制御回路に結合された出力端子を有し、デジタル通信線における電位が要求範囲に到達したか否かを検出するよう構成された検出回路(126)とを具える。前記制御回路(120)は、前記検出器が前記デジタルレベルへの変化中に前記電位が要求範囲に達したことを示したときに選択されたドライブ強度についての情報を記憶し、前記デジタルレベルからの変化時に第1ステップとして、ドライブ強度を最後に記憶されたドライブ強度に戻すように構成されている。  (もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]