Fターム[5J056EE06]の内容

Fターム[5J056EE06]に分類される特許

801 - 803 / 803

複合型補正バッファの設計

【課題】複合型インピーダンス補正バッファ回路を提供する。

【解決手段】本発明の一実施例によって、回路を開示する。該回路は、その一部が目標インピーダンスを供給するために使用される複数のドライバスライスと、複数のドライバスライスの一部を選ぶためのデジタル整合論理と、プルアップとプルダウンとを整合させるようバイアス電圧を作るアナログ整合回路とを有する。

(もっと読む)

(もっと読む)

電力低下及び過電圧トレランスを有するバスホールド回路

CMOS構成要素のバスホールド回路であって、DC電流を引き込まず且つ過電圧の許容性がある、バスホールド回路が説明される。入力電圧が前記バスホールドの供給電圧よりも大きい時には、該入力から漏れ電流が引き込まれない。フィードバックインバータが、前記バスホールド回路内においてVin論理をラッチするために用いられる。Vinがローである時には、前記バスホールド回路は、第1のスイッチをターンオンさせ、該第1のスイッチが、PMOSスイッチのゲートをローに駆動して、該PMOSスイッチをオンに切り替える。前記PMOSスイッチは、フィードバック・インバータの電力接続をVccに接続する。前記ゲートは、ローのままとなり、Vinが増加する時に、前記PMOSスイッチをオンに切り替えたままに保持する。前記第1のスイッチがターンオフさせられるが、前記PMOSのゲートは、VinがVccを越えるまでローのままとなる。その時点において、比較器は、前記PMOSのゲートを、PMOSスイッチをオフに切るVinに駆動する。アービタ回路が、前記PMOSスイッチと、前記比較器内及びアービタ回路内における他のPMOS構成要素とのNウェルをバイアスさせるために、Vcc及びVinのうちのより高いものを選択する。このバイアス動作は、Nウェルが決して順方向バイアスされないことを保証し、それによって、Vinからの漏れを防止する。

(もっと読む)

(もっと読む)

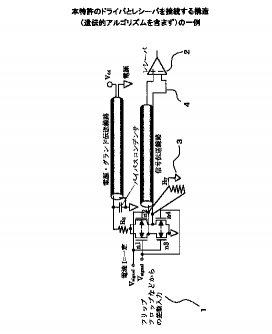

高速信号伝送システム

【課題】本発明は、2GHz以上の高速なLSIチップと接続され、該LSIチップと信号のやり取りをするチップ外線路に数十GHz帯ディジタル高速信号を通すことである。

【解決手段】本発明の高速信号伝送システムは、トランジスタキャリアのポンプアップ、ポンプダウンを自動的に行うデバイス構造、受信情報をフィードバックし、送信側で波形調整する遺伝的アルゴリズム回路の挿入、トランジスタから出て行く配線の伝送線路化、回路のコモン電源を排除した構成を作る。上記チップ外線路の送端または終端側の一方で基準電位を確認するため電源またはグランドへの接続を有するが、該基準電位を確認した送端または終端側の反対側の終端または送端では電源またはグランドへの接続を有さない。

(もっと読む)

801 - 803 / 803

[ Back to top ]