国際特許分類[G06F12/10]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | アドレシングまたはアロケーション;リロケーション (4,708) | 階層構造のメモリ・システム,例.仮想メモリ・システム,におけるもの (2,277) | アドレス変換 (338)

国際特許分類[G06F12/10]に分類される特許

1 - 10 / 338

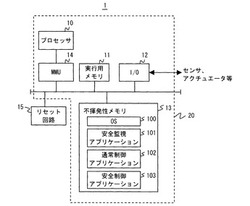

情報処理装置およびメモリ管理装置の動作確認方法

【課題】仮想アドレスを物理アドレスに変換するメモリ管理装置が正常に動作しているか否かを確認可能とする。

【解決手段】情報処理装置1は、メモリ11と、メモリ11の物理アドレス又はそれに対応する仮想アドレスを指定することで、メモリ11の物理アドレスに対してデータの読み出し又は書き込みを行うためのシステムプログラムと、システムプログラムを実行するプロセッサ10と、プロセッサ10からのメモリ11に対する仮想アドレスを指定した読み出し及び書き込みにおいて、仮想アドレスを物理アドレスに変換するメモリ管理装置14を備える。プロセッサ10は、システムプログラムによって、物理アドレスを指定してデータの書き込みを実施した後、その物理アドレスに対応する仮想アドレスを指定してデータの読み出しを実施して、書き込んだデータと、読み出したデータが一致するか否かを判定する。

(もっと読む)

アドレス変換装置、アドレス変換装置の制御方法及び演算処理装置

【課題】プロセス(コンテキスト)の切り替え時にエントリを無効化せずとも、アドレス変換に係る検索を適切なエントリだけを対象として行えるアドレス変換装置を提供する。

【解決手段】アクセス要求したプロセスのコンテキストとエントリのコンテキストとが一致すると判定された場合にオンとされるマッチフラグ36をエントリ毎に設け、アクセス要求で指定された仮想アドレスVAを物理アドレスPAに変換する場合に、マッチフラグ36がオンであるエントリだけを対象としてアドレス変換に用いるエントリを検索する。アクセス要求したプロセスのコンテキストに対応するものでないエントリのマッチフラグ36はオフされるので、プロセス(コンテキスト)の切り替え時にエントリを無効化しなくとも、アクセス要求したプロセスのコンテキストに対応するエントリだけを対象とした検索が可能となる。

(もっと読む)

複数のデータ・エレメントの収集及び分散

【課題】複数のデータ・エレメントの収集及び分散におけるオーバーヘッドを低減するプロセッサを提供する。

【解決手段】効率的なデータ転送処理は、単一の命令が複数のデータ・エレメントに対する第1の記憶域と第2の記憶域との間の転送処理を指定し、プロセッサ装置140,160によりデコードする段階、前記プロセッサ内の演算実行部による実行のために単一の命令を発行する段階、単一の命令の実行中に例外の発生を検出する段階、及び該例外に応答して、該例外を分配する前に、未解決のトラップ又は割り込みを例外ハンドラに分配する段階、により達成されうる。

(もっと読む)

アドレス変換装置、アドレス変換装置の制御方法及び演算処理装置

【課題】エントリのヒット率の低下を抑制できるようにする。

【解決手段】仮想アドレスと物理アドレスとの対応関係を示すアドレス情報がそれぞれ記憶される複数のCAM回路を有するCAM部と、新たなアドレス情報を記憶させる場合に書込みポインタが示しているCAM回路にアドレス情報の書込みを指示する書込み制御部とを有するマイクロTLBにおいて、書込みポインタが示しているCAM回路に記憶されているアドレス情報が、アドレス変換に使用されたことが示されている場合には書込みポインタをインクリメントするようにして、アドレス情報の使用が示されたCAM回路に新たなアドレス情報が書込まれることを回避して最近使用されているアドレス情報を保持し、ヒット率の低下を抑制する。

(もっと読む)

情報処理装置

【課題】ネットワーク透過な単一レベル記憶を実現すること。

【解決手段】本発明の一つの実施形態によれば、情報処理装置は、第1メモリと、第2メモリと、仮想アドレス空間の少なくとも一部の仮想アドレスと前記第1メモリの物理アドレスとの対応関係を管理する変換情報を参照して、前記第1メモリにアクセスする制御部と、を備える。前記仮想アドレス空間には、他の情報処理装置に格納されたデータも割り当てられる。前記制御部は、アクセス対象データが前記他の情報処理装置に格納され手いる状態でページフォールトが発生した場合、前記他の情報処理装置に格納された前記アクセス対象データを前記第1メモリに格納するとともに、前記アクセス対象データに対応する仮想アドレスと前記第1メモリの物理アドレスの対応関係を前記変換情報に登録する。

(もっと読む)

アドレス変換装置、演算処理装置及び演算処理装置の制御方法

【課題】ページテーブル検索での不要なメモリアクセスの発生を抑制することができるアドレス変換装置を提供する。

【解決手段】仮想アドレスと物理アドレスの組をページサイズ毎に保持しアドレス変換を行うアドレス変換バッファ(TLB)と、ページテーブルから読み出された新たな仮想アドレスと物理アドレスとの組がTLBに登録された場合、TLBから追い出された仮想アドレスとそれに対応するページサイズとの組を保持する記憶部と、ベースアドレスをページサイズ毎に保持するベースレジスタと、メモリアクセス要求に含まれる変換対象の仮想アドレスに基づきTLBを検索し、検索ミスが発生した場合、記憶部及びベースレジスタが保持する情報から生成したポインタアドレスに基づいて主記憶を検索し変換対象の仮想アドレスを物理アドレスに変換するようにして、不要なメモリアクセスの発生を抑制する。

(もっと読む)

演算処理装置及び演算処理装置の制御方法

【課題】使用頻度の高い論理アドレス空間が頻繁に入れ替わることを防止する演算処理装置を提供することを課題とする。

【解決手段】アドレス変換対を記憶するバッファ領域を有する記憶装置に接続される演算処理装置において、複数の論理アドレスレジスタのうち使用履歴が最も古い論理アドレスレジスタの番号を保持するLRUレジスタと、記憶装置に対するアクセス要求に含まれる論理アドレスが、下限論理アドレスレジスタが保持する下限論理アドレスから上限論理アドレスレジスタが保持する上限論理アドレスまでの論理アドレス空間の範囲に入っていない場合、LRUレジスタが保持する論理アドレスレジスタの番号を読み出す読み出し部(S502)と、読み出された番号の論理アドレスレジスタを無効にし、アクセス要求に含まれる論理アドレスに対応する論理アドレス空間を、無効にした論理アドレスレジスタに設定する設定部(S410)を有する。

(もっと読む)

アドレス変換方法及び装置

【課題】メモリの中の異なるページの間の境界クロシングの原因となるアドレスを識別し、プロセッサ内でのアドレス変換性能を改善する。

【解決手段】プロセッサは、第1及び第2のメモリページの間のページ境界をクロスするメモリ領域へのアクセスを認識するように構成される回路を備える。回路は、また、第1及び第2のメモリページと関連するアドレス変換情報をリンクするように構成される。このように、同一のメモリ領域へのその後のアクセスに応答して、第1及び第2のメモリページと関連するアドレス変換情報は、1つのアドレス変換に基づいて検索可能である。

(もっと読む)

排他制御装置、方法及びプログラム

【課題】コア同士がキャッシュメモリを用いて通信を行っている場合に、コア間の通信速度の低下を防ぐこと。

【解決手段】排他制御装置は、プロセスによってコア間の通信に用いられるメインメモリの論理アドレスを物理ページ番号に変換し、プロセスと物理ページ番号とを対応付けてキャッシュ禁止テーブルに格納するキャッシュ禁止領域指定部と、物理ページ番号に対応するキャッシュラインを計算し、キャッシュラインを使用する物理ブロック番号をキャッシュ禁止テーブルに格納するキャッシュライン計算部と、キャッシュ禁止テーブルに格納された物理ページ番号が、キャッシュ禁止テーブルにおいて物理ページ番号に対応付けられたプロセス以外のプロセスに対するプロセス管理情報のページテーブルエントリに存在する場合には、キャッシュを禁止するためのフラグを当該エントリに設定するキャッシュ禁止部を有する。

(もっと読む)

画像形成装置および画像形成プログラム

【課題】 画像形成装置において、ファイルアクセスに非OS管理領域を使用することに起因するプロセッサーの負荷を軽減する。

【解決手段】 画像形成装置において、拡張I/O処理部34は、RAM内の非OS管理領域における、ユーザープロセス12からの指令により物理アドレスで指定された領域を使用して、ファイルシステム31上のファイルへのファイルアクセスを行う。

(もっと読む)

1 - 10 / 338

[ Back to top ]