国際特許分類[G06F13/32]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ,入力/出力装置または中央処理ユニットの間の情報または他の信号の相互接続または転送 (29,400) | 相互接続または転送のための接続要求 (2,939) | 入力/出力バスに対するアクセスのためのもの (715) | 割込みおよびバーストモード転送の組合わせを用いるもの (13)

国際特許分類[G06F13/32]の下位に属する分類

優先制御によるもの (3)

国際特許分類[G06F13/32]に分類される特許

1 - 10 / 10

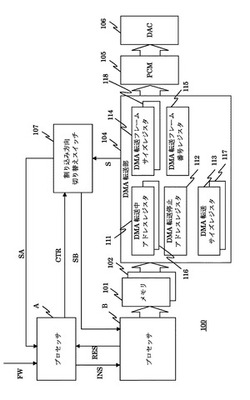

オーディオ再生装置及びオーディオ再生方法

【課題】DMA転送を用いるオーディオ再生装置に対して、消費電力を抑制すると共に、通常再生と特殊再生の切り替え時に誤再生を回避する。

【解決手段】DMA転送部104は、DMA転送フレーム番号レジスタ115、DMA転送フレームサイズレジスタ114、DMA転送中アドレスレジスタ111、DMA転送停止アドレスレジスタ112を備える。プロセッサAにより電源のオン/オフが制御されるプロセッサBは、DMA転送中に、通常再生とは異なる特殊再生が要求されたときに、メモリ101に格納されたフレームのうちの、該フレームの転送が完了すると、メモリ101に格納されたデコード後データの転送を停止する停止フレームの終端アドレスをDMA転送停止アドレスレジスタ112に設定する。

(もっと読む)

情報処理装置

【課題】大容量データをATAコマンドで不揮発性メモリに対して送受信している際に、大容量データの送受信を一つのATAコマンド処理に占有されないよう、別のATAコマンドを受け付けて時分割処理を可能とする。

【解決手段】CPU101は、転送するデータサイズが大容量データと判断した場合、フラグ105をセットする。データ転送中に別のATAコマンドが発行され、フラグがセットされている場合には、ATAコマンド割り込み装置110に、割り込ませる別のATAコマンドを設定し、割り込み装置110は、ブロック単位の転送の終了を検出すると、データ転送を中断させた後、別のATAコマンドを起動する。

(もっと読む)

データ転送装置およびデータ転送方法

【課題】上位装置の記憶部にデータの転送が終了した毎にデータ転送が完了した旨を上位装置の制御部へ通知する。

【解決手段】データを転送する転送先アドレスおよび転送データ数を定義した転送設定情報を複数記憶する転送リスト5と、転送リスト5に設定されたそれぞれの転送設定情報に従って入力データを上位装置の記憶部に転送するとともに該転送が完了するとその旨を上位装置へ通知(48)する転送データ制御部4と、その通知の要否を記憶する割込みモードレジスタ41とを設け、転送データ制御部4は、割込みモードレジスタ41に通知要が記憶されているとき、転送リスト5に設定された転送設定情報毎に、入力データの転送が完了した旨を上位装置へ通知する。

(もっと読む)

半導体集積回路

【課題】複数の割り込み要因に対する処理での重複処理の矛盾を解消する際の負担を軽減する。

【解決手段】外部メモリ7へデータ転送が完了し、高優先度のデータ転送完了割り込みが発生する。受信中断の間に所定パケット数のデータ転送が未完了の場合、低優先度のタイマ割り込みが生成される。割り込みに応答した外部メモリのデータ処理前にカウンタ114から転送パケット数が取得される。受信再開後に、カウンタは転送再開パケット数を格納する。タイマ割り込み発生18Cに応答したカウンタからの転送パケット数の取得18Dの後、データ転送完了割り込み18Eが生じる。取得転送パケット数に従って、タイマ割り込みの発生18Cに応答する処理18I(図18(A))もしくはデータ転送完了割り込みの発生18Eに応答する処理18G(図18(B))のいずれかの実行が省略される。

(もっと読む)

DMAコントローラ、情報処理装置、及びDMA管理方法

【課題】冗長な情報がバスを伝送することでバスの転送効率が低下してしまうこと。

【解決手段】DMAコントローラ5は、個々に実行されるDMA転送間の関連性に応じたDMA転送のグループ化に準じて、個々のDMA転送に対応する個々の個別情報をグループ化して管理する転送情報管理部13と、転送情報管理部13が管理する個別情報に基づいて、DMA転送のグループ単位でDMA転送の完了を示す割込みを生成する割込み発生部14と、を備える。グループ単位でDMA転送の完了をCPUに通知することで、冗長な割込みがバスを伝送することを抑制することができる。

(もっと読む)

I2Cバス制御回路

【課題】従来のI2Cバス制御回路は送信データの設定タイミングを割込み信号によって実現しており、連続した複数のデータの送信時間はI2Cバスのクロックに依存するだけでなくコントローラの割込み処理のオーバーヘッドをも含み、通信時間に無駄があった。

【解決手段】従来のI2Cバス制御回路に連続送信機能を追加し、連続送信後に割込みを発生することで割込み処理回数を削減して、通信時間を短縮する。

(もっと読む)

データ転送装置

【課題】データ転送処理が始まってから、バスを使用する優先度の高い他の処理による割り込みが発生した場合、その優先度の高い他の処理を可能な限り早く実行させることが可能なデータ転送装置を提供することである。

【解決手段】本発明のデータ転送装置は、要求元からのデータ転送要求に基づいて、転送元記憶領域のデータを転送先記憶領域に転送する。そして、装置に内蔵された一次記憶領域と、上記転送元記憶領域と上記一次記憶領域との間に設けられた第1アライナと、上記一次記憶領域と上記転送先記憶領域との間に設けられた第2アライナを備える。上記第1アライナは、上記一次記憶領域の先頭位置以降に転送元記憶領域のデータを連続して格納するようにシフト処理を行い、上記第2アライナは、上記データ転送要求で指定された転送先記憶領域の先頭位置以降に上記一次記憶領域のデータを格納するようにシフト処理を行う。

(もっと読む)

シリアル割込み復帰回路

【課題】 外部からのシリアルデータにより周辺機器を停止状態から復帰させるシステムにおいて、無駄な電力の消費を削減するとともにCPUのパフォーマンスに関係なく高速受信を行えるシリアル割込み復帰回路を提供する。

【解決手段】 受信シフトレジスタ102と、受信制御回路101と、復帰要求設定レジスタ107と、比較回路109と、割込み発生回路114と、受信割込み復帰制御回路106と、クロック制御回路105とを備えることにより、受信待受け、受信動作、復帰要求データ比較動作の際にCPU116を停止することができ、無駄なCPU動作を削減し、無駄な電力の消費を低減させることができる。また、CPU動作と関係なく受信動作を行うことができるので、CPUのパフォーマンスに関係なく高速受信を安定して行える。

(もっと読む)

マルチプロセッサ・システム並びに画像処理装置、撮像装置

【課題】 アーリー・バースト・ターミネーション(バースト転送中断)後のバースト再開動作を簡便な回路で実現するとともに、ソフトウエア的なタイムアウトを防ぐ。

【解決手段】 CPUバス・スレーブ部がCPUバスI/F部、データ転送制御部、バースト長保持手段、バーストカウント手段を具備するとともに、バースト中断検出手段並びにマスタID保持手段をさらに具備する。また、バースト中断検出手段から出力されるバースト中断信号と、CPUバスI/F部から出力される起動信号並びにコマンド信号をさらに具備し、前記バースト中断信号がアサートされている期間は、前記起動信号のアサート並びにコマンド信号の更新を抑止することにより、CPUバス・スレーブ部の各部をバースト転送中断前の状態に保持する。さらに、バースト中断中にCPUからのリードアクセスがあった場合、所定のデータ値を返すことによって、CPUに対してリトライを通知する。

(もっと読む)

ホストコントローラ

【構成】 USBホストであるレコーダは、周辺機器であるカメラから要求信号をインタラプト転送方式で受け付ける。そして、要求信号を受け付けたとき、カメラからバルク転送方式で動画像データの転送を要求するコマンドを取得し、取得されたコマンドに従う動画像データをバルク転送方式でフレーム毎にカメラに返信する。

【効果】 ホスト機器によって管理されている動画コンテンツに周辺機器の操作でアクセスできる。

(もっと読む)

1 - 10 / 10

[ Back to top ]