国際特許分類[H03K21/12]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | パルス計数器または周波数分割器の細部 (119) | 出力回路 (10) | 並列読出し回路をもつもの (3)

国際特許分類[H03K21/12]に分類される特許

1 - 3 / 3

カウンタ回路、及びその方法

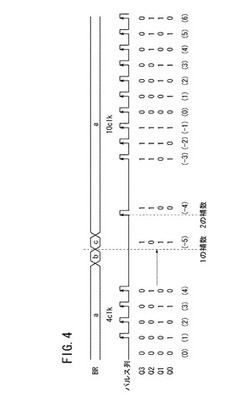

【課題】デジタル論理回路で扱い易く、回路の実装面積を小さくすることができるカウンタ回路、及びその方法を提供する。

【解決手段】カウンタ回路であって、複数のフリップフロップ回路と、自身に入力される入力信号、ロー信号、及びハイ信号のうち、何れか1つを選択して出力する複数のスイッチ回路とを交互に接続する。第1のパルス列と第2のパルス列のパルス数をカウントする期間の場合は、前記入力信号を出力するようにスイッチ回路を制御する。第1のパルスから第2のパルスに切り替わる場合は、ロー信号を出力してからハイ信号を出力するようにスイッチ回路を制御することで、現在のカウント値を1の補数に変換させる。第2のパルス列をカウントする期間に入ると、1パルスをカウンタ回路に入力させることで、2の補数に変換してから第2のパルス列のパルス数をカウントする。

(もっと読む)

分周回路及び分周方法

【課題】複数段の1/2分周器により分周された各信号において、全ての分周信号同士が同期し、かつクロック信号の同一のエッジに同期した分周信号を出力することが可能な分周回路及び分周方法を提供する。

【解決手段】第1の同期回路群は、分周器群と第1の同期回路群との間に設けられ、分周器群からの各分周信号を入力とし、その出力が第1の同期回路群のラッチ回路の各入力端子に接続されたN段のラッチ回路からなり、第1段目から第M段目のラッチ回路のクロック入力端子にはクロック信号が入力され、クロック信号に同期した信号を出力し、第(M+1)段目から第N段目までのラッチ回路のクロック入力端子には第M段目のラッチ回路の出力信号が入力され、M段目のラッチ回路の出力に同期した信号を出力する第2の同期回路群を有する。

(もっと読む)

電気カウンタ回路

電気カウンタ回路(30,40,80)は、複数のクロック信号(21−24,121−125,131−134)を発生するクロック発生器(1,54,111,120,130)と、デジタル信号(DS)の第1の特徴信号部分(LE)が現れる第1の瞬時にクロック信号(21−24,121−125,131−134)をサンプリングするサンプリング装置(32,81)と、を具えている。さらに、電気カウンタ回路(30,40,80)は、第1の瞬時と、第1の瞬時以降の第2の瞬時との間の時間を算出する計算装置(33)を具えている。この算出は、第1の瞬時におけるクロック信号(21−24,121−125,131−134)に基づき、かつ第2の瞬時におけるクロック信号(21−24,121−125,131−134)に基づく。クロック信号(21−24,121−125,131−134)は、各々同じサイクル持続時間(T)を有し、各々互いに位相シフトされる。  (もっと読む)

(もっと読む)

1 - 3 / 3

[ Back to top ]