国際特許分類[H03K3/286]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電気的パルスの発生回路;単安定回路,双安定回路,多安定回路 (1,702) | パルスの発生に用いられる回路形式または手段によって特徴づけられた発生器 (1,478) | 能動素子として内部または外部正帰還をもつバイポーラトランジスタを用いるもの (51) | 変成器以外の手段を帰還に用いるもの (50) | 一方のトランジスタの入力が他方のトランジスタの出力から得られる少なくとも2個のトランジスタを用いるもの,例.マルチバイブレータ (50) | 双安定 (19)

国際特許分類[H03K3/286]の下位に属する分類

帰還回路中に付加トランジスタを用いるもの

入力回路中に付加トランジスタを用いるもの

マスタースレーブ形のもの (7)

ヒステリシスをもつ双安定,例.シュミットトリガ (4)

国際特許分類[H03K3/286]に分類される特許

1 - 8 / 8

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

ラッチ回路

【課題】ラッチ回路において出力論理が確定するまでの遅延時間を短縮する技術を提供する。

【解決手段】一対のデータ入力端子間の電圧に基づいて正電源端子に接続された第1抵抗からの電流と正電源端子に接続された第2抵抗からの電流とを制御する第1差動ペアと、第1差動ペアによる制御の結果に基づいて第1抵抗からの電流と第2抵抗からの電流とを制御する第2差動ペアと、一対のクロック入力端子間の電圧に基づいて第1差動ペア及び第2差動ペアのいずれかにバイアス電流を流す第3差動ペアと、正負の電圧を含む所定範囲に対し、一対のラッチ出力端子間の電圧が所定範囲内にある場合のバイアス電流が一対のラッチ出力端子間の電圧が所定範囲外にある場合のバイアス電流より大きくなるように、バイアス電流を発生するバイアス電流発生部とを備えるラッチ回路である。

(もっと読む)

フリップフロップ回路及びそれを備えたプリスケーラ回路

【課題】従来のプリスケーラ回路は、高速動作において精度の高い分周ができないという問題があった。

【解決手段】本発明にかかるプリスケーラ回路は、外部入力信号に応じた中間信号を生成するマスター側ラッチ回路と、中間信号に応じた出力信号を生成するスレーブ側ラッチ回路と、切替制御信号に基づいて自己の出力信号又は固定信号を選択して制御信号として出力する制御信号切替回路と、を備えたFF回路4と、FF4の出力信号に応じた出力信号をFF回路4に対して出力するFF回路3と、を備える。さらに、マスター側ラッチ回路は、入力信号に基づいてオンオフ制御される第1の差動回路と、第1の差動回路の共通ソースと、一方のドレインとの間に設けられ、制御信号に基づいてオンオフ制御される第2の差動回路と、第1及び第2の差動回路に基づいて生成された中間信号を保持する第3の差動回路と、を備える。

(もっと読む)

ラッチ回路を有する信号処理装置

【課題】 ラッチ回路がノイズによって誤動作することがある。

【解決手段】

信号処理装置は、セットパルス発生回路3と、リセットパルス発生回路5と、ラッチ回路4との他に補正セットパルス形成回路30を有する。補正セット信号形成回路30は、セットパルスからリセットパルスまでの時間幅にほぼ対応する補正セット信号を形成してラッチ回路4に送る。ラッチ回路4はノイズによってリセットされても補正セット信号によって再びセットされる。

(もっと読む)

PLL周波数シンセサイザ、半導体集積回路および通信装置

【課題】 消費電力を低減することが可能な、動作の安定性が高いPLL周波数シンセサイザ、半導体集積回路および通信装置を提供する。

【解決手段】 可変分周器は、複数段のD−FF21,22,23,・・・で構成される。D−FF21において、スイッチ回路SW1〜SW5がオフ状態のとき、トランジスタTr1,Tr3によってバイアス電流I1,I3が流れる。スイッチ回路SW1〜SW5がオン状態のとき、トランジスタTr1〜Tr4によってバイアス電流I1〜I4が流れる。また、Q端子36およびQX端子37から出力される信号の電圧振幅は、常に(Ibias×RL)/2となる。したがって、可変分周器の消費電力を低減することが可能になる。

(もっと読む)

半導体集積回路

【課題】前段のフリップフロップ回路の電流調整なしに、その出力信号の振幅の減衰を容易に抑えることができ、次段のフリップフロップ回路の誤動作を確実に回避することができる半導体集積回路を提供する。

【解決手段】フリップフロップ回路251のマスター部とスレーブ部の回路構成が同一で、前段のフリップフロップ回路251に例えば後段のフリップフロップ回路として多くのフリップフロップ回路が接続される場合でも、レベルシフト用のバッファ回路252の電流を調整するだけで、前段のフリップフロップ回路251からの出力信号の振幅を増大することにより、その出力信号に対して、後段のフリップフロップ回路における寄生容量等の影響による振幅低減を補う。

(もっと読む)

ラッチを有する装置

トラッキングモードにおいてデータ信号をトラッキングするトラッキング回路4及び決定モードにおいて前記データ信号について決定する決定回路5を持つラッチ1−3を有する装置101−105は、前記トラッキングモードにおいて決定回路5を準備することにより利用可能な時間をより効率的に使用することができる。これに加えて、決定回路5は、ディスエーブル/イネーブル状態間で切り換えられるべきでなく、イネーブルに保たれるべきである。トラッキング回路4は、前記トラッキングモードにおいて、前記データ信号から得られた信号値を決定回路5に供給し、決定回路5は、前記決定モードにおいて前記信号値を増幅する。トラッキング回路5は、ダイオード21、22を有し、前記データ信号値における減少された電圧振幅がラッチ1−3の適切な動作に対して十分であることを可能にする。このような減少された電圧振幅は、ラッチ1−3がより高速で機能することを可能にする。ダイオード21、22のカソード間に存在する寄生キャパシタは、前記信号値を記憶するキャパシタンスを形成し、決定回路5が準備されることを可能にする。  (もっと読む)

(もっと読む)

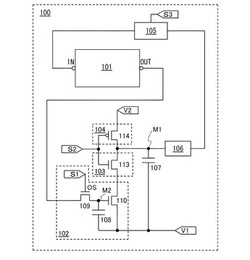

フリップ・フロップ回路の構造

本発明はフリップ・フロップを形成するよう組み合わせられた四つの差動増幅器(1、2、3、4)を使用したフリップ・フロップ回路の構造を提供する。本発明によれば、差動増幅器(1、2、3、4)の両共通エミッタノード (E1、E2) は供給電位部に対して一対のスイッチ (S1、S2) を介して接続されており、微分クロック入力信号により制御入力部 (CN、CP)において駆動される。本フリップ・フロップ回路はきわめて少量の供給電圧により動作することが可能であり、好ましくは周波数分割器または変換レジスタの構成に適用される。  (もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]