国際特許分類[H03L7/097]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896) | 2つの周波数電圧変換器の出力電圧を比較する比較器を用いるもの (2)

国際特許分類[H03L7/097]に分類される特許

1 - 2 / 2

PLL周波数シンセサイザ

【課題】デジタル制御発振器の周波数を安定して制御する。

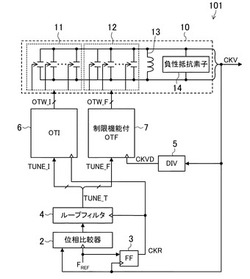

【解決手段】PLL周波数シンセサイザ(101)は、基準クロック信号とPLL周波数シンセサイザの出力信号との位相差を検出する位相比較器(2)と、位相差に応じた整数値および小数値の和からなる制御値を出力するループフィルタ(4)と、第1のクロック信号に同期して、整数値に相当する第1のデジタル制御信号を出力する周波数制御部(6)と、第1のクロック信号よりも高い周波数の第2のクロック信号に同期して、平均値として小数値を表す第2のデジタル制御信号を出力する周波数制御部(7)であって、当該PLL周波数シンセサイザがロック状態にあるとき、第2のデジタル制御信号の取り得る値の範囲をロック時の範囲に制限する周波数制御部と、第1および第2のデジタル制御信号によるそれぞれの周波数制御の組み合わせに応じた周波数で発振するデジタル制御発振器(10)とを備えている。

(もっと読む)

周波数差補償器

【課題】 二つの電圧制御型発振器のそれぞれの発振波形を位相は同期せずに周波数のみを等しくするような周波数差補償器を提供する。

【解決手段】 入力制御端子から得る制御電圧Vcntに応じた周波数fで発振する発振器01と、発振周波数fに依存した直流電圧値Vfを出力する周波数変換器02と、一定周波数frで発振する発振器03と、周波数frに依存した直流電圧値Vfrを出力する周波数変換器04と、周波数変換器02及び周波数変換器04の各出力値の差分に基づき出力値Vcmpを出力する比較器05と、出力値Vcmpに基づいて発振周波数Vfが発振周波数Vfrと等しくなるように入力制御端子へ制御電圧Vcntを出力する制御器06から構成される周波数差補償器とした。

(もっと読む)

1 - 2 / 2

[ Back to top ]