電源回路

【目的】 減電時の出力トランジスタに供給すべきベース電流を適正値に制御して出力トランジスタの飽和を防止する。

【構成】 基準電圧(Vref)と出力側からの帰還電圧(Vn)とを比較し、両者の差電圧に応じた電流を発生する増幅器(差動増幅器2)と、この増幅器が発生した電流がベース電流として供給され、そのベース電流に応じた電流を流す出力トランジスタ(4)と、この出力トランジスタに直列に接続されて安定化出力を発生するとともに前記増幅器に対する前記帰還電圧を発生する負荷抵抗とを備えた電源回路であって、前記出力トランジスタに加えられる電圧の低下を検出し、その電圧低下に応じた電流を前記出力トランジスタから取り出して前記出力トランジスタの前記ベース電流を調整する飽和防止回路(50)を備えたものである。

【構成】 基準電圧(Vref)と出力側からの帰還電圧(Vn)とを比較し、両者の差電圧に応じた電流を発生する増幅器(差動増幅器2)と、この増幅器が発生した電流がベース電流として供給され、そのベース電流に応じた電流を流す出力トランジスタ(4)と、この出力トランジスタに直列に接続されて安定化出力を発生するとともに前記増幅器に対する前記帰還電圧を発生する負荷抵抗とを備えた電源回路であって、前記出力トランジスタに加えられる電圧の低下を検出し、その電圧低下に応じた電流を前記出力トランジスタから取り出して前記出力トランジスタの前記ベース電流を調整する飽和防止回路(50)を備えたものである。

【発明の詳細な説明】

【0001】

【産業上の利用分野】本発明は、基準電圧を増幅手段で増幅して取り出すマルチ電源用IC等に用いられる電源回路に関する。

【0002】

【従来の技術】一般に、CDプレーヤのピックアップのトラッキングサーボやフォーカスサーボ等、高い精度が要求される制御を行う各種の制御回路には、制御動作の信頼性を高めるために電圧変動が極めて小さい電源が必要であり、この電源には、電圧出力の安定化を図った電源回路が不可欠である。

【0003】図5は、この電源回路の原理的な構成を示している。即ち、この電源回路には、電圧比較手段としての差動増幅器2とともに出力トランジスタ4を備えた安定化回路6が設置されており、この安定化回路6の差動増幅器2の正相入力端子(+)と接地点との間には電圧源8が接続され、正相入力端子(+)に基準電圧Vrefが加えられている。そして、出力トランジスタ4のコレクタ側に負荷とともに分圧回路を成す抵抗10、12が直列に接続されており、これら出力トランジスタ4及び抵抗10、12の直列回路は、電源端子14を通して電源電圧Vccが加えられる電源ライン15と接地点との間に直列に接続されている。抵抗10、12の分圧点に現れる電圧Vnは帰還回路16を通して差動増幅器2の逆相入力端子(−)に加えられている。

【0004】このような安定化回路6を備えた電源回路では、基準電圧Vrefと電圧Vnとが差動増幅器2によって比較され、両者の差電圧に応じた電流が出力トランジスタ4のベースから差動増幅器2側に引き込まれる。即ち、この出力トランジスタ4のベース電流は、基準電圧Vrefを基準にして電圧Vnの偏差に応じた電流値となる。したがって、出力トランジスタ4には、差動増幅器2の比較出力としてのベース電流によってコレクタ電流が制御され、このコレクタ電流と抵抗10、12とによって得られる安定化出力としての出力電圧Voが出力端子18から取り出される。

【0005】ところで、このような安定化回路6では、電源電圧Vccが電池によって供給されている場合の電池の消耗、電池以外の直流電源で供給されている場合に急激な外部負荷の変動等の外乱によってその値が低下して、電源電圧Vccが出力電圧Voに近づく減電時には出力トランジスタ4が飽和状態に移行することになる。

【0006】図6は、この安定化回路における出力トランジスタ4の構成を示す。P形半導体で形成された基板20にはN形の高濃度領域からなる埋込み層22が形成され、この埋込み層22を覆ってN形のベース領域24が形成されている。このベース領域24はアイソレーション領域26によって他の領域と分離され、その表面層部分にはN形の高濃度領域を以てベース電極28が形成されているとともに、高濃度のP形導電領域からなるエミッタ領域30が形成され、このエミッタ領域30を包囲して高濃度のP形導電領域からなるコレクタ領域32が形成されている。したがって、この出力トランジスタ4は、正常動作時には、ベース領域24、エミッタ領域30及びコレクタ領域32を以て増幅動作が行われる。

【0007】ところが、電源電圧Vccの低下でエミッタ領域30側の電位が下がり、その電位とコレクタ領域32側の電位との間の電位差が小さくなると、エミッタ領域30をエミッタ、ベース領域24をベース、アイソレーション領域26即ち基板20をコレクタとする寄生トランジスタ34が生起し、この寄生トランジスタ34を通してエミッタ領域30から基板20側へ突入電流が流れることになる。この突入電流の大きさは、寄生トランジスタ34の規模、即ち、出力トランジスタ4の規模に応じたものとなる。この場合、出力トランジスタ4は大きな出力電流を予定しているため、そのエミッタ面積が大きく、大きいエミッタ面積を持つ寄生トランジスタ34に流れる突入電流もそのエミッタ面積に比例して極めて大きいものとなる。

【0008】このように出力トランジスタ4の飽和状態は飽和電流に加え、寄生トランジスタ34による突入電流が基板20側に流れ、基板20の過熱や基板電位を不安定なものにすることになる。このような減電時の飽和状態への突入は、安定化動作を毀損し、電源回路の持つべき本来の機能を損なうことになる。

【0009】従来、このような不都合を防止するため、図7に示す電源回路が提案されている。即ち、この電源回路では、安定化回路6の出力トランジスタ4の飽和状態への突入を防止するため、安定化回路6の前段に飽和防止回路36が設置されている。この飽和防止回路36には、差動増幅器2に対応する差動増幅器38が設置されているとともに、出力トランジスタ4に対応するトランジスタ40が設置され、抵抗10、12に対応する抵抗42、44、46が設置されている。また、差動増幅器38の正相入力端子(+)には、電圧源48が接続されて基準電圧Vrefが加えられ、また、その逆相入力端子(−)には抵抗44、46の接続点Pに発生する基準電圧Vpが帰還されている。そして、この基準電圧Vpは、基準電圧Vrefに対応して同値であって、安定化回路6の差動増幅器2の正相入力端子(+)に加えられている。

【0010】この電源回路において、抵抗42の抵抗値をRα、抵抗44の抵抗値をR1 、抵抗46の抵抗値をR2 、抵抗10の抵抗値をR1 ′、抵抗12の抵抗値をR2 ′とすると、R1 :R2 =R1 ′:R2 ′となるように各抵抗10、12、44、46の各抵抗値を整合させ、寄生トランジスタの影響が少ないトランジスタ40を出力トランジスタ4の飽和に先立って飽和するように抵抗42が挿入されている。即ち、その飽和に移行する基準電圧Vpは、電圧Vnより電圧Vref・Rα/R2 だけ低下させている。したがって、減電時、出力トランジスタ4の飽和に先立ってトランジスタ40が飽和状態に移行し、その結果、出力トランジスタ4の飽和状態への移行が阻止される。

【0011】そして、安定化動作によって、出力端子18に取り出される出力電圧Voは

【0012】

【数1】

【0013】となる。

【0014】ところが、このような電源回路では、トランジスタ40の飽和状態への移行によって出力トランジスタ4の飽和を防止できるが、トランジスタ40は飽和しており、基板への飽和電流はトランジスタ40の容量が小さいことにより低減できるが、製造工程のばらつき等による突入電流の増減が制御できないため、電源回路における消費電流が不安定となる。また、トランジスタ40の飽和電圧の増減が基準電圧Vpによって出力電圧Voに反映され、その結果、安定化が妨げられることになる。

【0015】そこで、本発明は、減電時、出力トランジスタに供給すべきベース電流を適正値に制御して出力トランジスタの飽和を防止した電源回路を提供することを目的とする。

【0016】

【課題を解決するための手段】本発明の電源回路は、基準電圧(Vref)と出力側からの帰還電圧(Vn)とを比較し、両者の差電圧に応じた電流を発生する増幅器(差動増幅器2)と、この増幅器が発生した電流がベース電流として供給され、そのベース電流に応じた電流を流す出力トランジスタ(4)と、この出力トランジスタに直列に接続されて安定化出力を発生するとともに前記増幅器に対する前記帰還電圧を発生する負荷抵抗(抵抗10、12)とを備えた電源回路であって、前記出力トランジスタに加えられる電圧の低下を検出し、その電圧低下に応じた電流を前記出力トランジスタから取り出して前記出力トランジスタの前記ベース電流を調整する飽和防止回路(50)を備えたことを特徴とする。

【0017】本発明の電源回路において、飽和防止回路(50)は、前記出力トランジスタに加えられる前記電圧の低下を検出する電圧検出回路(52、Tr502、抵抗504、定電流源506)と、この電圧検出回路が検出した電圧低下に応じて前記出力トランジスタに流れる電流を引き込むとともに、その電流に対応する電流を前記出力トランジスタのベース入力側から接地側に放流させる電流帰還回路(54)とを備えたことを特徴とする。

【0018】

【作用】本発明の電源回路では、出力トランジスタに流れる電流に応じて負荷抵抗に発生させた帰還電圧は、増幅器に帰還されて基準電圧と比較される。増幅器には、両者の差電圧に応じた電流が発生し、この電流が出力トランジスタのベース電流となる。したがって、基準電圧と帰還電圧との差電圧に応じたベース電流が出力トランジスタに流れ、このベース電流に応じた出力電流が負荷抵抗に流れて安定化出力を取り出すことができる。

【0019】そして、出力トランジスタに加えられる電圧が低下すると、その電圧低下に応じた電流が出力トランジスタ側から取り出され、その電流に応じて出力トランジスタのベース電流を抑制させる。この結果、出力トランジスタの飽和状態への移行を防止でき、減電時にも安定化動作が得られる。

【0020】また、飽和防止回路は、出力トランジスタに加えられる前記電圧の低下を検出する電圧検出回路と、この電圧検出回路が検出した電圧低下に応じて出力トランジスタに流れる電流を引き込むとともに、その電流に対応する電流を出力トランジスタのベース入力側から接地側に放流させる電流帰還回路とで構成すれば、電圧検出回路の電圧低下の検出に基づき、出力トランジスタに流れる電流が電流帰還回路を通して出力トランジスタのベース入力側に帰還され、そのベース入力側から接地側にベース電流の一部が放流されることにより、出力トランジスタの飽和状態への移行が阻止される。

【0021】

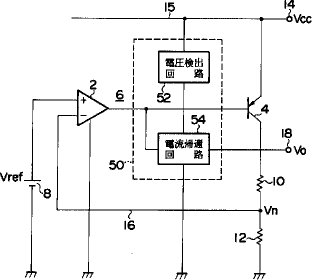

【実施例】以下、本発明の電源回路の一実施例を図面を参照して詳細に説明する。図1は、本発明の電源回路の一実施例を示している。この電源回路には、図5に示す電源回路と同様に、電圧比較手段としての差動増幅器2とともに出力トランジスタ4を備えた安定化回路6が設置され、安定化回路6の差動増幅器2の正相入力端子(+)と接地点との間には電圧源8が接続され、正相入力端子(+)に基準電圧Vrefが加えられている。また、出力トランジスタ4のコレクタ側に負荷抵抗を成すとともに出力を検出するための分圧回路を成す抵抗10、12が直列に接続されており、これら出力トランジスタ4及び抵抗10、12の直列回路は、電源端子14を通して電源電圧Vccに接続されている電源ライン15と接地点との間に直列に接続されている。抵抗10、12の分圧点に現れる電圧Vnは帰還回路16を通して差動増幅器2の逆相入力端子(−)に加えられている。

【0022】そして、この電源回路には、電源電圧Vccの電圧低下を検出し、その電圧低下に応じて出力トランジスタ4のベース電流を抑制することにより出力トランジスタ4の飽和状態への移行を防止する飽和防止回路50が設置されている。即ち、この飽和防止回路50には、電源電圧Vccの低下を検出する電圧検出回路52とともに、出力トランジスタ4に流れている電流をその電圧低下検出に基づいて引き込み、出力トランジスタ4のベース入力側に帰還し、出力トランジスタ4のベース電流を抑制する電流帰還回路54が設置されている。

【0023】このような構成によれば、電圧検出回路52は電源ライン15を通して電源電圧Vccの低下を検出し、その電圧低下を表す電流を出力し、この電流は検出出力として電流帰還回路54に加えられる。電流帰還回路54は、電圧検出回路52からの電流を受けて出力トランジスタ4のコレクタ側から電流を引き込み、その電流を出力トランジスタ4のベース入力側に帰還し、そのベース電流を抑制する。この結果、出力トランジスタ4のベース電流は、減電状態に応じて制御、即ち、抑制されることになり、出力トランジスタ4の飽和状態への移行を迅速かつ効果的に抑制することが可能になる。

【0024】そして、このような出力トランジスタ4の減電時の飽和防止は、何等安定化動作を損なうものではない。即ち、定常状態及び減電状態においても、差動増幅器2では基準電圧Vrefと抵抗10、12の分圧点で検出された電圧Vnとの比較が行われ、その差電圧に応じた電流が出力トランジスタ4のベース電流となり、差電圧に基づいて出力トランジスタ4の電流が制御されるからである。したがって、出力トランジスタ4の電流制御に基づき、出力端子18には安定化出力としての出力電圧Voが取り出されることになる。

【0025】次に、図2は、本発明の電源回路の具体的な回路構成例を示している。基準電圧Vrefと帰還電圧Vnとの電圧比較手段を成す差動増幅器2には、抵抗202、204を介してエミッタが共通化されたトランジスタ206、208を備えた差動回路が設置され、この差動回路と電源ライン15との間には差動対に動作電流を流すための定電流源210が接続され、また、トランジスタ206、208のコレクタ側と接地点との間にはトランジスタ212、214からなる能動負荷としてカレントミラー回路216が接続されている。この実施例では、接地端子218を通して接地された接地ライン220が接地点を成している。

【0026】各トランジスタ206、208のベースには、それぞれレベルシフト回路を成すトランジスタ222、224が設置され、トランジスタ222、224のエミッタと電源ライン15との間にはそれぞれ定電流源226、228が設置されており、各定電流源226、228からの定電流が各トランジスタ222、224のレベルシフト動作に寄与している。そして、トランジスタ222のベースは正相入力端子(+)、トランジスタ224のベースは逆相入力端子(−)となっており、トランジスタ222のベースと接地ライン220との間には電圧源8が接続されて基準電圧Vrefが加えられ、また、トランジスタ224のベースと接地ライン220との間には抵抗12に発生させた帰還電圧Vnが帰還回路16を通して帰還されている。

【0027】この差動回路の出力はトランジスタ208のコレクタ側から取り出されて出力回路225に加えられる。即ち、トランジスタ208のコレクタ側から取り出された出力はトランジスタ227のベースに加えられ、そのベース入力に応じた出力はそのエミッタから抵抗229を通してトランジスタ230のベースに加えられる。トランジスタ227、230はダーリントン接続されており、トランジスタ227に加えられるベース電流Iβを増幅した電流がトランジスタ230に引き込まれ、この電流が出力トランジスタ4のベース電流となる。この場合、出力トランジスタ4のベース・エミッタ間に接続されている抵抗232は、トランジスタ230の負荷抵抗であるとともに、出力トランジスタ4のバイアス電源を構成している。このような構成から、差動増幅器2の出力電流が出力トランジスタ4のベース電流となり、その電流増幅率に応じた電流が出力トランジスタ4を通して負荷抵抗である抵抗10、12に流れ、この結果、安定化出力としての出力電圧Voを発生させるとともに帰還電圧Vnを発生させるのである。したがって、差動増幅器2に対する帰還電圧Vnと基準電圧Vrefとの差電圧に応じて出力トランジスタ4のベース電流が制御されることにより、出力端子18には安定化出力としての出力電圧Voが取り出されることになる。

【0028】そして、この電源回路には、電源電圧Vccの減電時の出力トランジスタ4の飽和を防止するために飽和防止回路50が設置されている。即ち、電源ライン15と接地ライン220との間には、ベース・コレクタを共通にして実質的なダイオードを成すトランジスタ502、抵抗504及び定電流源506の直列回路が設置されており、この直列回路が電圧検出回路52を構成している。また、出力トランジスタ4のコレクタ側に分流回路を成すトランジスタ508のエミッタが接続され、このトランジスタ508のベースは抵抗504と定電流源506の接続点に接続されている。そして、トランジスタ508に流れる電流はトランジスタ510及び512からなるカレントミラー回路514を通して出力トランジスタ4のベース入力側回路をなすトランジスタ208と出力回路225のトランジスタ227とを結ぶベース入力ラインに帰還され、トランジスタ508に流れる電流をカレントミラー回路514を経て接地ライン220側に放流させるように構成されている。即ち、電流帰還回路54はトランジスタ508及びカレントミラー回路514で構成されている。

【0029】このような構成によれば、電源電圧Vccが所定の電圧に維持されている場合、電圧検出回路52のトランジスタ502及び抵抗504には、定電流源506に発生する定電流Iによって一定の電圧降下が生じ、定常時、トランジスタ508は遮断状態を維持する。このとき、差動増幅器2及び出力トランジスタ4による安定化動作により、出力端子18には安定化出力としての出力電圧Voが得られる。この定常状態における出力電圧Voは、

【0030】

【数2】

【0031】となり、図5に示した電源回路と同様の安定化動作が行われる。

【0032】また、電源電圧Vccが低下し、抵抗504の電圧降下が大きくなってトランジスタ508が導通すると、このトランジスタ508の導通によって出力トランジスタ4の電流はトランジスタ508を通してカレントミラー回路514側のトランジスタ510側に引き込まれる。トランジスタ510側に流れる電流は、カレントミラー効果によってトランジスタ512に流れ、トランジスタ227のベースに流れ込むべきベース電流Iβの一部がトランジスタ512に引き込まれて接地ライン220を通して接地点に放流することになる。

【0033】ここで、抵抗504の抵抗値をR3 、トランジスタ508のベース・エミッタ間電圧をVF 、トランジスタ502のベース・エミッタ間電圧をVF ′、定電流源506に流れる定電流をIとすると、 Vcc=Vo−VF +I・R3 +VF ′ ・・・(3)

が成立し、VF =VF ′とすると、式(3)は、 Vcc=Vo+I・R3 ・・・(4)

となり、出力電圧Voは、 Vo=Vcc+I・R3 ・・・(5)

となり、定電流Iと抵抗504の抵抗値R3 で設定できることが判る。

【0034】そして、このとき、カレントミラー回路514の電流吸込みにより、トランジスタ208、214のコレクタ側から引き出されるベース電流Iβは増大することになり、出力トランジスタ4のドライブ電流を増大させるような動作となるが、トランジスタ508、510、512で構成された電流帰還回路54の電流帰還動作により、ベース電流Iβが出力トランジスタ4を飽和させない適正な値に収束させることになり、制御系の安定化が図られることになる。したがって、このような飽和防止回路50の動作により、安定化動作を損なうことなく、減電時の出力トランジスタ4の飽和が防止でき、安定化出力を取り出すことができる。

【0035】次に、図3及び図4は、図2に示した電源回路における定電流源506の具体的な実施例を示す。即ち、定電流源506は、差動増幅器516の出力側にトランジスタ518のベースを接続するとともに、トランジスタ518のエミッタ側に抵抗520を接続し、差動増幅器516の正相入力端子(+)には電圧源522から基準電圧Vrefを加え、その逆相入力端子(−)には抵抗520に発生した電圧を帰還させることにより、抵抗520の抵抗値を抵抗504と同一の抵抗値R3 に設定し、この抵抗値R3 と基準電圧Vrefとで定まる定電流Iを取り出すようにしたものである。このような定電流回路を図2に示す電源回路の定電流源506に用いても、前記実施例と同様の動作を得ることができ、ばらつきの少ない入出力差を実現することができる。

【0036】また、図4に示すように、定電流源506は、ダイオード接続したトランジスタ524のベース・コレクタにトランジスタ526のベースを接続し、トランジスタ526のエミッタ側に抵抗528を接続してなるカレントミラー回路で構成してもよい。この場合、トランジスタ524に対してトランジスタ526の電流容量をn倍とし、抵抗528の抵抗値を抵抗504と同様の抵抗値R3 に設定すれば、前記実施例と同様の動作を得ることができ、ばらつきの少ない入出力差を実現することができる。

【0037】

【発明の効果】以上説明したように、本発明によれば、次の効果が得られる。

a.安定化動作を損なうことなく、減電に応じて出力トランジスタのベース入力側電流を制御して出力トランジスタの飽和を確実に防止でき、突入電流の発生を防止できる。

b.従来、出力トランジスタに飽和防止のために付加された回路と比較して、安定化回路を多重化しないため、回路の構成の簡略化を図ることができるとともに、出力トランジスタだけでなく前段側の回路の飽和状態への移行を阻止でき、動作の信頼性を高めることができる。

【図面の簡単な説明】

【図1】本発明の電源回路の一実施例を示す回路図である。

【図2】本発明の電源回路の具体的な回路構成例を示す回路図である。

【図3】図1の電源回路における定電流源の具体的な回路構成例を示す回路図である。

【図4】図1の電源回路における定電流源の他の具体的な回路構成例を示す回路図である。

【図5】従来の電源回路を示す回路図である。

【図6】図5に示した電源回路における出力トランジスタに対する寄生トランジスタの生起を示す図である。

【図7】出力トランジスタの飽和防止回路が付加された従来の電源回路を示す回路図である。

【符号の説明】

2 差動増幅器

4 出力トランジスタ

50 飽和防止回路

52 電圧検出回路

54 電流帰還回路

【0001】

【産業上の利用分野】本発明は、基準電圧を増幅手段で増幅して取り出すマルチ電源用IC等に用いられる電源回路に関する。

【0002】

【従来の技術】一般に、CDプレーヤのピックアップのトラッキングサーボやフォーカスサーボ等、高い精度が要求される制御を行う各種の制御回路には、制御動作の信頼性を高めるために電圧変動が極めて小さい電源が必要であり、この電源には、電圧出力の安定化を図った電源回路が不可欠である。

【0003】図5は、この電源回路の原理的な構成を示している。即ち、この電源回路には、電圧比較手段としての差動増幅器2とともに出力トランジスタ4を備えた安定化回路6が設置されており、この安定化回路6の差動増幅器2の正相入力端子(+)と接地点との間には電圧源8が接続され、正相入力端子(+)に基準電圧Vrefが加えられている。そして、出力トランジスタ4のコレクタ側に負荷とともに分圧回路を成す抵抗10、12が直列に接続されており、これら出力トランジスタ4及び抵抗10、12の直列回路は、電源端子14を通して電源電圧Vccが加えられる電源ライン15と接地点との間に直列に接続されている。抵抗10、12の分圧点に現れる電圧Vnは帰還回路16を通して差動増幅器2の逆相入力端子(−)に加えられている。

【0004】このような安定化回路6を備えた電源回路では、基準電圧Vrefと電圧Vnとが差動増幅器2によって比較され、両者の差電圧に応じた電流が出力トランジスタ4のベースから差動増幅器2側に引き込まれる。即ち、この出力トランジスタ4のベース電流は、基準電圧Vrefを基準にして電圧Vnの偏差に応じた電流値となる。したがって、出力トランジスタ4には、差動増幅器2の比較出力としてのベース電流によってコレクタ電流が制御され、このコレクタ電流と抵抗10、12とによって得られる安定化出力としての出力電圧Voが出力端子18から取り出される。

【0005】ところで、このような安定化回路6では、電源電圧Vccが電池によって供給されている場合の電池の消耗、電池以外の直流電源で供給されている場合に急激な外部負荷の変動等の外乱によってその値が低下して、電源電圧Vccが出力電圧Voに近づく減電時には出力トランジスタ4が飽和状態に移行することになる。

【0006】図6は、この安定化回路における出力トランジスタ4の構成を示す。P形半導体で形成された基板20にはN形の高濃度領域からなる埋込み層22が形成され、この埋込み層22を覆ってN形のベース領域24が形成されている。このベース領域24はアイソレーション領域26によって他の領域と分離され、その表面層部分にはN形の高濃度領域を以てベース電極28が形成されているとともに、高濃度のP形導電領域からなるエミッタ領域30が形成され、このエミッタ領域30を包囲して高濃度のP形導電領域からなるコレクタ領域32が形成されている。したがって、この出力トランジスタ4は、正常動作時には、ベース領域24、エミッタ領域30及びコレクタ領域32を以て増幅動作が行われる。

【0007】ところが、電源電圧Vccの低下でエミッタ領域30側の電位が下がり、その電位とコレクタ領域32側の電位との間の電位差が小さくなると、エミッタ領域30をエミッタ、ベース領域24をベース、アイソレーション領域26即ち基板20をコレクタとする寄生トランジスタ34が生起し、この寄生トランジスタ34を通してエミッタ領域30から基板20側へ突入電流が流れることになる。この突入電流の大きさは、寄生トランジスタ34の規模、即ち、出力トランジスタ4の規模に応じたものとなる。この場合、出力トランジスタ4は大きな出力電流を予定しているため、そのエミッタ面積が大きく、大きいエミッタ面積を持つ寄生トランジスタ34に流れる突入電流もそのエミッタ面積に比例して極めて大きいものとなる。

【0008】このように出力トランジスタ4の飽和状態は飽和電流に加え、寄生トランジスタ34による突入電流が基板20側に流れ、基板20の過熱や基板電位を不安定なものにすることになる。このような減電時の飽和状態への突入は、安定化動作を毀損し、電源回路の持つべき本来の機能を損なうことになる。

【0009】従来、このような不都合を防止するため、図7に示す電源回路が提案されている。即ち、この電源回路では、安定化回路6の出力トランジスタ4の飽和状態への突入を防止するため、安定化回路6の前段に飽和防止回路36が設置されている。この飽和防止回路36には、差動増幅器2に対応する差動増幅器38が設置されているとともに、出力トランジスタ4に対応するトランジスタ40が設置され、抵抗10、12に対応する抵抗42、44、46が設置されている。また、差動増幅器38の正相入力端子(+)には、電圧源48が接続されて基準電圧Vrefが加えられ、また、その逆相入力端子(−)には抵抗44、46の接続点Pに発生する基準電圧Vpが帰還されている。そして、この基準電圧Vpは、基準電圧Vrefに対応して同値であって、安定化回路6の差動増幅器2の正相入力端子(+)に加えられている。

【0010】この電源回路において、抵抗42の抵抗値をRα、抵抗44の抵抗値をR1 、抵抗46の抵抗値をR2 、抵抗10の抵抗値をR1 ′、抵抗12の抵抗値をR2 ′とすると、R1 :R2 =R1 ′:R2 ′となるように各抵抗10、12、44、46の各抵抗値を整合させ、寄生トランジスタの影響が少ないトランジスタ40を出力トランジスタ4の飽和に先立って飽和するように抵抗42が挿入されている。即ち、その飽和に移行する基準電圧Vpは、電圧Vnより電圧Vref・Rα/R2 だけ低下させている。したがって、減電時、出力トランジスタ4の飽和に先立ってトランジスタ40が飽和状態に移行し、その結果、出力トランジスタ4の飽和状態への移行が阻止される。

【0011】そして、安定化動作によって、出力端子18に取り出される出力電圧Voは

【0012】

【数1】

【0013】となる。

【0014】ところが、このような電源回路では、トランジスタ40の飽和状態への移行によって出力トランジスタ4の飽和を防止できるが、トランジスタ40は飽和しており、基板への飽和電流はトランジスタ40の容量が小さいことにより低減できるが、製造工程のばらつき等による突入電流の増減が制御できないため、電源回路における消費電流が不安定となる。また、トランジスタ40の飽和電圧の増減が基準電圧Vpによって出力電圧Voに反映され、その結果、安定化が妨げられることになる。

【0015】そこで、本発明は、減電時、出力トランジスタに供給すべきベース電流を適正値に制御して出力トランジスタの飽和を防止した電源回路を提供することを目的とする。

【0016】

【課題を解決するための手段】本発明の電源回路は、基準電圧(Vref)と出力側からの帰還電圧(Vn)とを比較し、両者の差電圧に応じた電流を発生する増幅器(差動増幅器2)と、この増幅器が発生した電流がベース電流として供給され、そのベース電流に応じた電流を流す出力トランジスタ(4)と、この出力トランジスタに直列に接続されて安定化出力を発生するとともに前記増幅器に対する前記帰還電圧を発生する負荷抵抗(抵抗10、12)とを備えた電源回路であって、前記出力トランジスタに加えられる電圧の低下を検出し、その電圧低下に応じた電流を前記出力トランジスタから取り出して前記出力トランジスタの前記ベース電流を調整する飽和防止回路(50)を備えたことを特徴とする。

【0017】本発明の電源回路において、飽和防止回路(50)は、前記出力トランジスタに加えられる前記電圧の低下を検出する電圧検出回路(52、Tr502、抵抗504、定電流源506)と、この電圧検出回路が検出した電圧低下に応じて前記出力トランジスタに流れる電流を引き込むとともに、その電流に対応する電流を前記出力トランジスタのベース入力側から接地側に放流させる電流帰還回路(54)とを備えたことを特徴とする。

【0018】

【作用】本発明の電源回路では、出力トランジスタに流れる電流に応じて負荷抵抗に発生させた帰還電圧は、増幅器に帰還されて基準電圧と比較される。増幅器には、両者の差電圧に応じた電流が発生し、この電流が出力トランジスタのベース電流となる。したがって、基準電圧と帰還電圧との差電圧に応じたベース電流が出力トランジスタに流れ、このベース電流に応じた出力電流が負荷抵抗に流れて安定化出力を取り出すことができる。

【0019】そして、出力トランジスタに加えられる電圧が低下すると、その電圧低下に応じた電流が出力トランジスタ側から取り出され、その電流に応じて出力トランジスタのベース電流を抑制させる。この結果、出力トランジスタの飽和状態への移行を防止でき、減電時にも安定化動作が得られる。

【0020】また、飽和防止回路は、出力トランジスタに加えられる前記電圧の低下を検出する電圧検出回路と、この電圧検出回路が検出した電圧低下に応じて出力トランジスタに流れる電流を引き込むとともに、その電流に対応する電流を出力トランジスタのベース入力側から接地側に放流させる電流帰還回路とで構成すれば、電圧検出回路の電圧低下の検出に基づき、出力トランジスタに流れる電流が電流帰還回路を通して出力トランジスタのベース入力側に帰還され、そのベース入力側から接地側にベース電流の一部が放流されることにより、出力トランジスタの飽和状態への移行が阻止される。

【0021】

【実施例】以下、本発明の電源回路の一実施例を図面を参照して詳細に説明する。図1は、本発明の電源回路の一実施例を示している。この電源回路には、図5に示す電源回路と同様に、電圧比較手段としての差動増幅器2とともに出力トランジスタ4を備えた安定化回路6が設置され、安定化回路6の差動増幅器2の正相入力端子(+)と接地点との間には電圧源8が接続され、正相入力端子(+)に基準電圧Vrefが加えられている。また、出力トランジスタ4のコレクタ側に負荷抵抗を成すとともに出力を検出するための分圧回路を成す抵抗10、12が直列に接続されており、これら出力トランジスタ4及び抵抗10、12の直列回路は、電源端子14を通して電源電圧Vccに接続されている電源ライン15と接地点との間に直列に接続されている。抵抗10、12の分圧点に現れる電圧Vnは帰還回路16を通して差動増幅器2の逆相入力端子(−)に加えられている。

【0022】そして、この電源回路には、電源電圧Vccの電圧低下を検出し、その電圧低下に応じて出力トランジスタ4のベース電流を抑制することにより出力トランジスタ4の飽和状態への移行を防止する飽和防止回路50が設置されている。即ち、この飽和防止回路50には、電源電圧Vccの低下を検出する電圧検出回路52とともに、出力トランジスタ4に流れている電流をその電圧低下検出に基づいて引き込み、出力トランジスタ4のベース入力側に帰還し、出力トランジスタ4のベース電流を抑制する電流帰還回路54が設置されている。

【0023】このような構成によれば、電圧検出回路52は電源ライン15を通して電源電圧Vccの低下を検出し、その電圧低下を表す電流を出力し、この電流は検出出力として電流帰還回路54に加えられる。電流帰還回路54は、電圧検出回路52からの電流を受けて出力トランジスタ4のコレクタ側から電流を引き込み、その電流を出力トランジスタ4のベース入力側に帰還し、そのベース電流を抑制する。この結果、出力トランジスタ4のベース電流は、減電状態に応じて制御、即ち、抑制されることになり、出力トランジスタ4の飽和状態への移行を迅速かつ効果的に抑制することが可能になる。

【0024】そして、このような出力トランジスタ4の減電時の飽和防止は、何等安定化動作を損なうものではない。即ち、定常状態及び減電状態においても、差動増幅器2では基準電圧Vrefと抵抗10、12の分圧点で検出された電圧Vnとの比較が行われ、その差電圧に応じた電流が出力トランジスタ4のベース電流となり、差電圧に基づいて出力トランジスタ4の電流が制御されるからである。したがって、出力トランジスタ4の電流制御に基づき、出力端子18には安定化出力としての出力電圧Voが取り出されることになる。

【0025】次に、図2は、本発明の電源回路の具体的な回路構成例を示している。基準電圧Vrefと帰還電圧Vnとの電圧比較手段を成す差動増幅器2には、抵抗202、204を介してエミッタが共通化されたトランジスタ206、208を備えた差動回路が設置され、この差動回路と電源ライン15との間には差動対に動作電流を流すための定電流源210が接続され、また、トランジスタ206、208のコレクタ側と接地点との間にはトランジスタ212、214からなる能動負荷としてカレントミラー回路216が接続されている。この実施例では、接地端子218を通して接地された接地ライン220が接地点を成している。

【0026】各トランジスタ206、208のベースには、それぞれレベルシフト回路を成すトランジスタ222、224が設置され、トランジスタ222、224のエミッタと電源ライン15との間にはそれぞれ定電流源226、228が設置されており、各定電流源226、228からの定電流が各トランジスタ222、224のレベルシフト動作に寄与している。そして、トランジスタ222のベースは正相入力端子(+)、トランジスタ224のベースは逆相入力端子(−)となっており、トランジスタ222のベースと接地ライン220との間には電圧源8が接続されて基準電圧Vrefが加えられ、また、トランジスタ224のベースと接地ライン220との間には抵抗12に発生させた帰還電圧Vnが帰還回路16を通して帰還されている。

【0027】この差動回路の出力はトランジスタ208のコレクタ側から取り出されて出力回路225に加えられる。即ち、トランジスタ208のコレクタ側から取り出された出力はトランジスタ227のベースに加えられ、そのベース入力に応じた出力はそのエミッタから抵抗229を通してトランジスタ230のベースに加えられる。トランジスタ227、230はダーリントン接続されており、トランジスタ227に加えられるベース電流Iβを増幅した電流がトランジスタ230に引き込まれ、この電流が出力トランジスタ4のベース電流となる。この場合、出力トランジスタ4のベース・エミッタ間に接続されている抵抗232は、トランジスタ230の負荷抵抗であるとともに、出力トランジスタ4のバイアス電源を構成している。このような構成から、差動増幅器2の出力電流が出力トランジスタ4のベース電流となり、その電流増幅率に応じた電流が出力トランジスタ4を通して負荷抵抗である抵抗10、12に流れ、この結果、安定化出力としての出力電圧Voを発生させるとともに帰還電圧Vnを発生させるのである。したがって、差動増幅器2に対する帰還電圧Vnと基準電圧Vrefとの差電圧に応じて出力トランジスタ4のベース電流が制御されることにより、出力端子18には安定化出力としての出力電圧Voが取り出されることになる。

【0028】そして、この電源回路には、電源電圧Vccの減電時の出力トランジスタ4の飽和を防止するために飽和防止回路50が設置されている。即ち、電源ライン15と接地ライン220との間には、ベース・コレクタを共通にして実質的なダイオードを成すトランジスタ502、抵抗504及び定電流源506の直列回路が設置されており、この直列回路が電圧検出回路52を構成している。また、出力トランジスタ4のコレクタ側に分流回路を成すトランジスタ508のエミッタが接続され、このトランジスタ508のベースは抵抗504と定電流源506の接続点に接続されている。そして、トランジスタ508に流れる電流はトランジスタ510及び512からなるカレントミラー回路514を通して出力トランジスタ4のベース入力側回路をなすトランジスタ208と出力回路225のトランジスタ227とを結ぶベース入力ラインに帰還され、トランジスタ508に流れる電流をカレントミラー回路514を経て接地ライン220側に放流させるように構成されている。即ち、電流帰還回路54はトランジスタ508及びカレントミラー回路514で構成されている。

【0029】このような構成によれば、電源電圧Vccが所定の電圧に維持されている場合、電圧検出回路52のトランジスタ502及び抵抗504には、定電流源506に発生する定電流Iによって一定の電圧降下が生じ、定常時、トランジスタ508は遮断状態を維持する。このとき、差動増幅器2及び出力トランジスタ4による安定化動作により、出力端子18には安定化出力としての出力電圧Voが得られる。この定常状態における出力電圧Voは、

【0030】

【数2】

【0031】となり、図5に示した電源回路と同様の安定化動作が行われる。

【0032】また、電源電圧Vccが低下し、抵抗504の電圧降下が大きくなってトランジスタ508が導通すると、このトランジスタ508の導通によって出力トランジスタ4の電流はトランジスタ508を通してカレントミラー回路514側のトランジスタ510側に引き込まれる。トランジスタ510側に流れる電流は、カレントミラー効果によってトランジスタ512に流れ、トランジスタ227のベースに流れ込むべきベース電流Iβの一部がトランジスタ512に引き込まれて接地ライン220を通して接地点に放流することになる。

【0033】ここで、抵抗504の抵抗値をR3 、トランジスタ508のベース・エミッタ間電圧をVF 、トランジスタ502のベース・エミッタ間電圧をVF ′、定電流源506に流れる定電流をIとすると、 Vcc=Vo−VF +I・R3 +VF ′ ・・・(3)

が成立し、VF =VF ′とすると、式(3)は、 Vcc=Vo+I・R3 ・・・(4)

となり、出力電圧Voは、 Vo=Vcc+I・R3 ・・・(5)

となり、定電流Iと抵抗504の抵抗値R3 で設定できることが判る。

【0034】そして、このとき、カレントミラー回路514の電流吸込みにより、トランジスタ208、214のコレクタ側から引き出されるベース電流Iβは増大することになり、出力トランジスタ4のドライブ電流を増大させるような動作となるが、トランジスタ508、510、512で構成された電流帰還回路54の電流帰還動作により、ベース電流Iβが出力トランジスタ4を飽和させない適正な値に収束させることになり、制御系の安定化が図られることになる。したがって、このような飽和防止回路50の動作により、安定化動作を損なうことなく、減電時の出力トランジスタ4の飽和が防止でき、安定化出力を取り出すことができる。

【0035】次に、図3及び図4は、図2に示した電源回路における定電流源506の具体的な実施例を示す。即ち、定電流源506は、差動増幅器516の出力側にトランジスタ518のベースを接続するとともに、トランジスタ518のエミッタ側に抵抗520を接続し、差動増幅器516の正相入力端子(+)には電圧源522から基準電圧Vrefを加え、その逆相入力端子(−)には抵抗520に発生した電圧を帰還させることにより、抵抗520の抵抗値を抵抗504と同一の抵抗値R3 に設定し、この抵抗値R3 と基準電圧Vrefとで定まる定電流Iを取り出すようにしたものである。このような定電流回路を図2に示す電源回路の定電流源506に用いても、前記実施例と同様の動作を得ることができ、ばらつきの少ない入出力差を実現することができる。

【0036】また、図4に示すように、定電流源506は、ダイオード接続したトランジスタ524のベース・コレクタにトランジスタ526のベースを接続し、トランジスタ526のエミッタ側に抵抗528を接続してなるカレントミラー回路で構成してもよい。この場合、トランジスタ524に対してトランジスタ526の電流容量をn倍とし、抵抗528の抵抗値を抵抗504と同様の抵抗値R3 に設定すれば、前記実施例と同様の動作を得ることができ、ばらつきの少ない入出力差を実現することができる。

【0037】

【発明の効果】以上説明したように、本発明によれば、次の効果が得られる。

a.安定化動作を損なうことなく、減電に応じて出力トランジスタのベース入力側電流を制御して出力トランジスタの飽和を確実に防止でき、突入電流の発生を防止できる。

b.従来、出力トランジスタに飽和防止のために付加された回路と比較して、安定化回路を多重化しないため、回路の構成の簡略化を図ることができるとともに、出力トランジスタだけでなく前段側の回路の飽和状態への移行を阻止でき、動作の信頼性を高めることができる。

【図面の簡単な説明】

【図1】本発明の電源回路の一実施例を示す回路図である。

【図2】本発明の電源回路の具体的な回路構成例を示す回路図である。

【図3】図1の電源回路における定電流源の具体的な回路構成例を示す回路図である。

【図4】図1の電源回路における定電流源の他の具体的な回路構成例を示す回路図である。

【図5】従来の電源回路を示す回路図である。

【図6】図5に示した電源回路における出力トランジスタに対する寄生トランジスタの生起を示す図である。

【図7】出力トランジスタの飽和防止回路が付加された従来の電源回路を示す回路図である。

【符号の説明】

2 差動増幅器

4 出力トランジスタ

50 飽和防止回路

52 電圧検出回路

54 電流帰還回路

【特許請求の範囲】

【請求項1】 基準電圧と出力側からの帰還電圧とを比較し、両者の差電圧に応じた電流を発生する増幅器と、この増幅器が発生した電流がベース電流として供給され、そのベース電流に応じた電流を流す出力トランジスタと、この出力トランジスタに直列に接続されて安定化出力を発生するとともに前記増幅器に対する前記帰還電圧を発生する負荷抵抗と、を備えた電源回路であって、前記出力トランジスタに加えられる電圧の低下を検出し、その電圧低下に応じた電流を前記出力トランジスタから取り出して前記出力トランジスタの前記ベース電流を調整する飽和防止回路を備えたことを特徴とする電源回路。

【請求項2】 前記飽和防止回路は、前記出力トランジスタに加えられる前記電圧の低下を検出する電圧検出回路と、この電圧検出回路が検出した電圧低下に応じて前記出力トランジスタに流れる電流を引き込むとともに、その電流に対応する電流を前記出力トランジスタのベース入力側から接地側に放流させる電流帰還回路と、を備えたことを特徴とする請求項1記載の電源回路。

【請求項1】 基準電圧と出力側からの帰還電圧とを比較し、両者の差電圧に応じた電流を発生する増幅器と、この増幅器が発生した電流がベース電流として供給され、そのベース電流に応じた電流を流す出力トランジスタと、この出力トランジスタに直列に接続されて安定化出力を発生するとともに前記増幅器に対する前記帰還電圧を発生する負荷抵抗と、を備えた電源回路であって、前記出力トランジスタに加えられる電圧の低下を検出し、その電圧低下に応じた電流を前記出力トランジスタから取り出して前記出力トランジスタの前記ベース電流を調整する飽和防止回路を備えたことを特徴とする電源回路。

【請求項2】 前記飽和防止回路は、前記出力トランジスタに加えられる前記電圧の低下を検出する電圧検出回路と、この電圧検出回路が検出した電圧低下に応じて前記出力トランジスタに流れる電流を引き込むとともに、その電流に対応する電流を前記出力トランジスタのベース入力側から接地側に放流させる電流帰還回路と、を備えたことを特徴とする請求項1記載の電源回路。

【図1】

【図3】

【図4】

【図5】

【図2】

【図6】

【図7】

【図3】

【図4】

【図5】

【図2】

【図6】

【図7】

【公開番号】特開平5−150848

【公開日】平成5年(1993)6月18日

【国際特許分類】

【出願番号】特願平3−336048

【出願日】平成3年(1991)11月26日

【出願人】(000116024)ローム株式会社 (3,539)

【公開日】平成5年(1993)6月18日

【国際特許分類】

【出願日】平成3年(1991)11月26日

【出願人】(000116024)ローム株式会社 (3,539)

[ Back to top ]