シーゲイト テクノロジー エルエルシーにより出願された特許

101 - 110 / 278

トンネル磁気抵抗再生素子

【課題】垂直異方性自由層およびサイドシールドを備えた磁気センサを開示する。

【解決手段】トンネル磁気抵抗再生素子は、下部磁気シールドから上部磁気シールドを隔てるセンサスタックを含む。センサスタックは、基準磁化配向方向を有する基準磁気要素と、基準磁化配向方向に対して実質的に垂直な自由磁化配向方向を有する自由磁気要素とを含む。非磁性スペーサ層により基準磁気要素が自由磁気要素から隔てられる。第1のサイド磁気シールドおよび第2のサイド磁気シールドは、上部磁気シールドと下部磁気シールドとの間に配置される。センサスタックは、第1のサイド磁気シールドと第2のサイド磁気シールドとの間にある。第1のサイド磁気シールドおよび第2のサイド磁気シールドは、下部磁気シールドから上部磁気シールドを電気的に絶縁する。

(もっと読む)

トランスデューサおよびトランスデューサの製造方法

【課題】トランスデューサおよびトランスデューサの製造方法を開示する。

【解決手段】トランスデューサは、後縁と、前縁と、後縁および前縁の間に延びる1対の対向する側壁とを含むように成形される、基板上に形成された磁性材料を含む。保護材料の層は、成形された磁性材料の1対の側壁の各々と接触して位置決めされる。埋め戻し材料は、成形された磁性材料の1対の側壁の各々の上の保護材料を取囲む。

(もっと読む)

パンチスルーアクセスを有する縦型不揮発性スイッチおよびその製造方法

不揮発性メモリセルにアクセスするための半導体装置が提供される。いくつかの実施形態においては、半導体装置は、ソース、ドレインおよびウェルを含む半導体層の縦型スタックを有する。半導体装置へのドレイン−ソースバイアス電圧の印加は、ウェルにわたってパンチスルー機構を生成し、ソースとドレインとの間の電流の流れを発生させる。  (もっと読む)

(もっと読む)

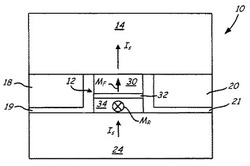

直交磁化配向方向を伴う基準層を有する磁気スタック

磁気セル(10)は、自由磁化配向方向(MF)を有する強磁性自由層(18)と、自由磁化配向方向に平行または逆平行の第1の基準磁化配向方向(MR1)を有する第1の強磁性固定基準層(14)とを含む。第1の酸化物バリヤ層(16)は、強磁性自由層と第1の強磁性固定基準層との間にある。磁気セルは、第1の基準磁化配向方向に直交する第2の基準磁化配向方向(MR2)を有する第2の強磁性固定基準層(13)をさらに含む。強磁性自由層は、第1の強磁性固定基準層と第2の強磁性固定基準層との間にある。  (もっと読む)

(もっと読む)

活性イオン界面領域を備えた不揮発性メモリ

不揮発性メモリおよびその使用方法が開示される。さまざまな実施例に従って、メモリセルは、導電領域と金属領域との間に配置されたトンネル領域を含み、トンネル領域は、第1のトンネル障壁と第2のトンネル障壁との間または第1のトンネル障壁と導電領域または金属領域との間に配置された活性界面領域を含む。メモリセルを選択された抵抗状態にプログラムする書込電流に応じた金属領域と導電領域との両方からのイオンの移動とともに高抵抗性膜が活性界面領域の中に形成される。  (もっと読む)

(もっと読む)

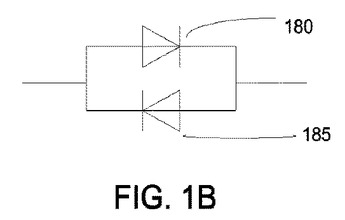

ショットキーダイオードスイッチおよびそれを含むメモリユニット

スイッチング素子は、第1の部分と第2の部分とを有する第1の半導体層と、第1の部分と第2の部分とを有する第2の半導体層と、上記第1の半導体層と上記第2の半導体層との間に配置される絶縁層と、上記第1の半導体層の上記第1の部分と接触して第1の接合部を形成するとともに、上記第2の半導体層の上記第1の部分と接触して第2の接合部を形成する第1の金属コンタクトと、上記第1の半導体層の上記第2の部分と接触して第3の接合部を形成するとともに、上記第2の半導体層の上記第2の部分と接触して第4の接合部を形成する第2の金属コンタクトとを含み、上記第1の接合部と上記第4の接合部とはショットキー接触部であり、上記第2の接合部と上記第3の接合部はオーミック接触部である。  (もっと読む)

(もっと読む)

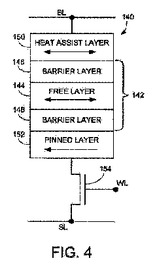

静磁場によりアシストされた抵抗性検知素子

スピン注入型ランダムアクセスメモリ(STRAM)等の不揮発性メモリセル(140,154)にデータを書込むための装置および関連する方法。いくつかの実施例に従うと、抵抗性検知素子(RSE)(140)は、ヒートアシスト領域(150)、磁気トンネル接合(MTJ)(142)およびピン止め領域(152)を有する。スピン分極された電流を用いてMTJに第1論理状態が書込まれるとき、ピン止め領域およびヒートアシスト領域は、各々、実質的にゼロの正味磁気モーメントを有する。静磁場を用いてMTJに第2論理状態が書込まれるとき、ピン止め領域は実質的にゼロの正味磁気モーメントを有し、ヒートアシスト領域は非ゼロの正味磁気モーメントを有する。  (もっと読む)

(もっと読む)

磁気積層体設計

磁気積層体は、磁化の向きを切換えることができる自由層と、磁化の向きが固定された基準層と、これらの間にあるバリア層とを有する。この積層体は、自由層から電気的に分離されるとともに基準層と物理的に接触する環状反強磁性ピニング層を含む。ある実施の形態では、基準層は自由層よりも大きい。  (もっと読む)

(もっと読む)

非オーム選択層を有する不揮発性メモリセル

非オーム選択層を含む、不揮発性メモリセルおよび関連する方法が開示されている。一部の実施例に従い、不揮発性メモリセルは、非オーム選択層に結合される抵抗検知素子(RSE)からなる。選択層は、所定のしきい値以上の電流に応答して、第1の抵抗状態から第2の抵抗状態に遷移するよう構成されている。  (もっと読む)

(もっと読む)

不揮発性メモリセルの階層的クロスポイントアレイ

不揮発性メモリセルからデータを読出すための方法および装置。いくつかの実施形態においては、不揮発性メモリセルのクロスポイントアレイは、行および列に配置される。第2のメモリセルブロックを非活性化している間に第1のメモリセルブロックを活性化することができる選択回路が設けられる。さらに、読出回路が設けられ、それは、第2のメモリセルブロックに対応するブロック選択素子に第2の抵抗状態をプログラミングしながら、第1のメモリセルブロックに対応するブロック選択素子に第1の抵抗状態をプログラムすることによって、漏れ電流が低減された状態で、第1のメモリセルブロックにおける予め定められたメモリセルの論理状態を読出すことができる。  (もっと読む)

(もっと読む)

101 - 110 / 278

[ Back to top ]