インターシル アメリカズ インクにより出願された特許

1 - 10 / 14

能動領域ボンディングの両立性のある高電流構造体

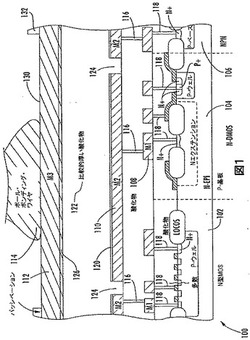

【課題】ボンディング・パッド下方に各回路を有する集積回路。

【解決手段】一実施例において、集積回路は基板と、最上部導電層と、1つ以上の中間導電層と、絶縁材料から成る各層と、各デバイスとを具備する。最上部導電層は少なくとも1個のボンディング・パッド及び比較的硬質の材料から成る副層を有する。1つ以上の中間導電層は最上部導電層及び基板の間に形成する。絶縁材料から成る各層は各導電層を分離する。更に、絶縁材料から成る各層のうちの1つの層は比較的硬質で、最上部導電層及びこの最上部導電層に最も近接した中間導電層の間に位置する。各デバイスは集積回路に形成する。また、最上部導電層に最も近接した少なくとも中間導電層は、ボンディング・パッド下方の各選択デバイスの機能的相互接続部に対して適合する。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

【課題】PWMコントローラチップのサイズ、コスト及び製造上の複雑を減らす。

【解決手段】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラが、提供される。PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL)とを備えている。このPLLは、位相信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器と、前記発振器に結合され、前記基準信号を受信し、且つ前記基準信号と、フィードバック信号との間の位相差に基づいて前記位相信号を生成させる位相周波数検出器(PFD)と、前記PFDに結合され、周期的にPFDが前記位相信号を生成することができるようにする抑制回路と、前記PFDに結合され、前記位相信号が同時に活性である時間の長さを制限するように動作可能なフィードフォワード回路とを備えている。

(もっと読む)

セルバランス充電システム及び方法

【課題】複数の直列接続されたバッテリセルのセルバランス充電システムの提供。

【解決手段】充電装置は、複数の直列接続されたバッテリセルに充電電圧を供給する第一及び第二の入力端子を含む。変圧器は、充電電圧と連携する一次側と、複数の二次側を含み、複数の直列接続されたバッテリセルのうち少なくとも二つのバッテリセルの両端に接続されている。二次側の複数の部分の各々と、複数の直列接続されたバッテリセルのうち少なくとも二つのバッテリセルの第一のバッテリセルとの間の直列の第一のスイッチは、変圧器の一次側中の電流のサイクルの第一の部分中に第一のバッテリセルに充電電流を供給する。二次側の複数の部分の各々と、複数の直列接続されたバッテリセルのうち少なくとも二つの第二のバッテリセルの間の直列の第二のスイッチは、変圧器の一次側中の電流のサイクルの第二の部分中に、第二のバッテリセルに充電電流を供給する。

(もっと読む)

鏡面反射を低減する光センサ

光源と光検出器を備えた本発明の実施形態に係る光センサ装置。光源は1つ以上の発光素子を含み,光検出器は1つ以上の光検出素子を含む。光源と光検出器の間にある第1の不透明な光バリア部は,光源から光検出器への光の直接伝達を遮るように構成される。第1の不透明な光バリア部から光源に向かう方向に延びる第2の不透明な光バリア部は,光透過性カバープレートが光センサ装置上に設置された場合に起こりうる鏡面反射の量を低減するように構成される。第1の不透明な光バリア部から光検出器に向かう方向に延びる第3の不透明な光バリア部は,光透過性カバープレートが光センサ装置上に設置された場合,光検出器で検出される鏡面反射量を低減するように構成される。 (もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

【課題】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラを提供する。

【解決手段】PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL300)とを備えている。このPLL300は、誤り訂正信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器312と、前記発振器312に結合され、前記基準信号341を受信し、且つ前記基準信号341と、フィードバック信号342との間の位相差に基づいて誤り訂正信号を生成させる位相周波数検出器(PFD302)と、前記PFD302に結合され、周期的にPFD302が誤り訂正信号を生成することができるようにする抑制回路321とを備えている。

(もっと読む)

容量性分圧器・バックコンバータ・バッテリ充電器一体型の電圧変換器

【課題】バックコンバータ117及びバッテリ充電器504と一体化した容量性分圧器を備えた電圧変換器501を提供する。

【解決手段】変換器は、4つのキャパシタ、スイッチ回路Q1〜Q4、インダクタL及び制御装置503を備える。これらのキャパシタは、入力ノード101と基準ノードGNDとの間にキャパシタループを形成し、スイッチ回路により制御されるフライキャパシタC2を備える。スイッチ回路は、第1の出力ノード105に第1の出力電圧VOUT1を供給するため入力電圧VINを半減し、かつ、インダクタを介して第1の出力電圧を第2の出力電圧VOUT2に変換するため、PWM信号により制御される。制御装置は、第2の出力電圧を調節するPWM信号を制御するとともに、第1の出力ノードを所定の最大バッテリ電圧レベルと所定の最小バッテリ電圧レベルの間に保つために、入力電圧を制御する電圧制御信号VCを与える。バッテリ充電経路は、基準ノードに結合され、バッテリ充電モードはバッテリ電圧によって決まる。

(もっと読む)

バックコンバータ・容量性分圧器一体型の電圧変換器

【課題】バックコンバータ117及び容量性分圧器を備えた電圧変換器100及び200を提供する。

【解決手段】変換器は、4つのキャパシタ、スイッチ回路Q1〜Q4、インダクタL及び制御装置IIIを備える。第1のキャパシタL1は、基準ノードと第1の出力電圧VOUT1を発生する第1の出力ノード105との間に結合される。第2のキャパシタC3或いはCAは、入力ノードと、基準ノード又は第1の出力ノードのいずれかとの間に結合される。スイッチ回路は、第3のキャパシタC2を、PWM信号の第1の状態においては基準ノードと第1の出力ノードとの間に、PWM信号の第2の状態においては第1の出力と入力ノードとの間に結合する。インダクタは、第3のキャパシタに結合され、第2の出力電圧VOUT2を供給する第4のキャパシタに結合された第2の出力ノード113を備える。制御装置は、第2の出力電圧を所定のレベルに調節するPWM信号のデューティサイクルを制御する。

(もっと読む)

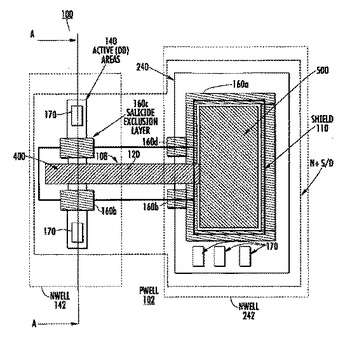

フローティングゲートトンネリング素子構造体のシールド

フローティングゲートトンネリング素子をシールドする方法とその構造体。標準的なCMOSプロセスを用いて、電界酸化物に囲まれた基板内に形成された第1および第2のドープウェル領域により定義される2つの活性領域内のゲート酸化物上にフローティングゲートを配置する工程と、前記フローティングゲートを囲むようにフローティングゲートシールド層を形成する工程を含む方法。前記フローティングゲートは、前記第1のドープウェル領域内の活性領域上の第1のフローティングゲート部および前記第2のドープウェル領域内の活性領域上の第2のフローティングゲート部を含む。前記第1のドープウェル領域と前記第1のフローティングゲート部との間にファウラーノルドハイムトンネリングのための適当な電圧カップリングが発生しうるよう、前記第1のフローティングゲート部は第2のフローティングゲート部より実質的に小さくなっている。トンネリングの方向は、前記ドープウェル領域の1つに高電圧を印加することにより決定される。  (もっと読む)

(もっと読む)

空乏可能コレクタ列を備えた改良されたBVCEO/RCS相殺を有するバイポーラ構造

【課題】本発明によれば、バイポーラトランジスタからなる集積回路の多様な製造方法を提供する。

【解決手段】本発明の一実施の形態によれば、バイポーラトランジスタは、基板と、複数の交互にドープされた領域を含み、複数の交互にドープされた領域は正味の第1導電型から正味の第2導電型へ横方向に交互に配置されたコレクタと、コレクタと電気的にコンタクトするコレクタコンタクトからなるように構成できる。また、バイポーラトランジスタは、コレクタの下において高濃度にドープされた埋め込み層と、ベースコンタクトと電気的にコンタクトし、正味の第2導電型にドープされ、複数の交互にドープされた領域の一部にかかるベースと、ベース内に配置され、正味の第1導電型にドープされたエミッタからなり、エミッタの下の複数の交互にドープされた領域の一部が、約3×1012cm-2未満の濃度でドープされていることを特徴とすることができる。

(もっと読む)

機能性が増した光ピックアップユニットとレーザドライバ

これに限られないが、DVDドライブ及びCDドライブ、DVDカムコーダ、並びにDVDビオデレコーダなどのさまざまなタイプの情報記録/再生装置で用いることが可能な光ピックアップユニット及びレーザドライバを開示する。レーザドライバ集積回路(LDIC)は、自動出力コントローラと、ランニング光出力コントローラと、書き込み戦略ジェネレータとを含む。LDICは、チップセットの一部となって、光ピックアップユニット(OPU)上に置くことが可能である。このチップセットはまた、レーザダイオードを監視する出力モニター集積回路(PMIC)と、レーザダイオードによって発生された光を検出する光検出集積回路(PDIC)とを含む。PMICとPDICは各々が、自分自身の専用のオフセット、利得及びサンプル・ホールドの回路を含んでいる。  (もっと読む)

(もっと読む)

1 - 10 / 14

[ Back to top ]