インテルユニフェルシタイル マイクロ−エレクトロニカ セントリューム (イーエムエーセー) フェーゼットヴェーにより出願された特許

1 - 1 / 1

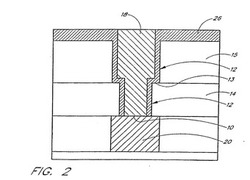

集積回路のメタライゼーションスキームにおけるバリア層のボトムレス堆積方法

【課題】デュアルダマシンメタライゼーションにおいて、Cu配線構造のバリア材料を絶縁層の表面上のみに選択的に形成し、接続構造部のエレクトロマイグレーションを抑制するとともに、下層導電層との接続抵抗を低減する選択的堆積方法を提供する。

【解決手段】Cu層20上の絶縁層14,15をエッチングしてトレンチとビアを開孔する。ビア底部のCu層の表面10に原子層成長(ALD)ブロック層を形成する。この後、原子層成長(ALD)法を用いてTiNバリア材料26を絶縁層表面12、13に堆積する。ブロック層により、ビア底部のCu層の表面にはバリアは形成されないため、ビア底部のCuは露出した状態のままである。開口部内にCu18を充填するとCu層に直接接続することが出来る。

(もっと読む)

1 - 1 / 1

[ Back to top ]