HIREC株式会社により出願された特許

1 - 5 / 5

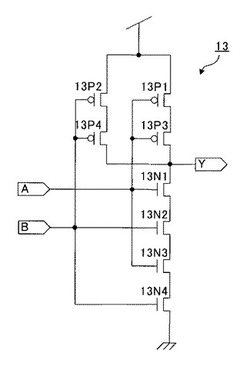

SOI構造シングルイベント耐性のNAND素子、及びNOR素子

【課題】高いシングルイベント耐性を有するNAND素子、NOR素子を提供する。

【解決手段】チャネルが並列に接続された第1のpチャネルMOSトランジスタ及び第2のpチャネルMOSトランジスタと、チャネルが直列に接続された第1のnチャネルMOSトランジスタ及び第2のnチャネルMOSトランジスタと、が第1の電圧源側に接続されたノードから第2の電圧源側に接続されたノードに向かって直列にSOI構造の基板上で接続され、それらのトランジスタのそれぞれに対して、それとゲート同士が相互に接続された同じ導電型のチャネルのMOSトランジスタがチャネルが直列に更に接続された二重化構造を有する。

(もっと読む)

オフアングル中性子積分フラックス測定演算装置及びその方法

【課題】強度高エネルギーの中性子ビームの積分フラックスのその場測定を可能とする、放射性物質を使用しない可搬型の測定演算装置を提供する。

【解決手段】ラジエータから中性子ビームに対して所定の角度(オフアングル角度)をおいて配置され、ノイズを防止する放射線遮蔽体に覆われた半導体検出器によって、ラジエータから発生する反跳陽子で所定のエネルギー以上のものの強度を測定し、それに所定の校正定数を乗ずることによって中性子ビームの積分フラックスを求める。

(もっと読む)

シングルイベント耐性のラッチ回路

【課題】シングルイベント現象が発生しにくく、シングルイベントトランジェント(SET)現象が発生してもそれの回路への影響を排除することができるラッチ回路及びフリップフロップ回路を提供する。

【解決手段】形成される強電界領域を狭くするために、ラッチ回路をデュアルポートインバータと、トランスミッションゲートを含まないデュアルポートクロックドインバータとから構成する。SET現象の影響をクロックに遅延時間を設けることにより排除するが、その遅延時間によってホールド時間が増加させられることを防止するために、一方の記憶ノードへは、その記憶ノード及び全体のラッチモードからスルーモードへの移行が遅延させられるような前縁エッジ遅延クロックが入力される。

(もっと読む)

シングルイベント耐性のラッチ回路及びフリップフロップ回路

【課題】シングルイベント現象が発生しにくく、シングルイベントトランジェント(SET)現象が発生してもそれの回路への影響を排除することができるラッチ回路及びフリップフロップ回路を提供する。

【解決手段】形成される強電界領域を狭くするために、ラッチ回路をデュアルポートインバータと、トランスミッションゲートを含まないデュアルポートクロックドインバータとから構成する。SET現象の影響をクロックに遅延時間を設けることにより排除するが、その遅延時間によってホールド時間が増加させられることを防止するために、一方の記憶ノードへは、その記憶ノード及び全体のラッチモードからスルーモードへの移行が遅延させられるような前縁エッジ遅延クロックが入力される。

(もっと読む)

SOI構造シングルイベント耐性のインバータ、NAND素子、NOR素子、半導体メモリ素子、及びデータラッチ回路

高いシングルイベント耐性を有するインバータ、NAND素子、NOR素子、メモリ素子、データラッチ回路を提供する。シングルイベント耐性インバータ(3I)は、インバータを構成するpチャネルMOSトランジスタ及びnチャネルMOSトランジスタのそれぞれに対して同じ導電型のトランジスタをさらに直列に接続した二重化構造(3P1,3P2,3N1,3N2)にし、2つのpチャネルMOSトランジスタの間のノード(A)と、2つのnチャネルMOSトランジスタの間のノード(B)とを接続線で接続する。シングルイベント耐性のメモリ素子及びデータラッチ回路(4)は、当該シングルイベント耐性インバータ(3I)を含む。 (もっと読む)

1 - 5 / 5

[ Back to top ]