ロッキード マーティン コーポレーションにより出願された特許

11 - 19 / 19

衛星利用測位システム・データ・インテグレータおよび配信システム

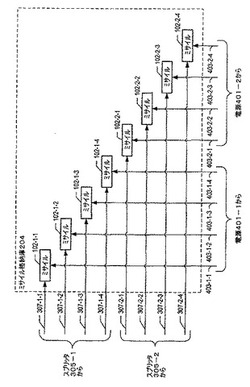

【課題】飛行前のミサイルの衛星利用測位システム受信機にホット・スタート航行情報を提供する兵器システムの改善を提供する。

【解決手段】分類された赤暗号鍵を使用して、衛星の1つまたは複数の衛星利用測位システムコンステレーションからのP(Y)信号を復号する衛星利用測位システム受信機を備える。一旦P(Y)信号が復号されると、信号の1つまたは複数の特性(例えば、PRN符号同期化、ドップラ・シフト、変調ビット・シーケンス等)が導き出される。次に、これらの信号の特性−および赤暗号鍵を含む黒暗号鍵他の情報−は、飛行前のミサイルの衛星利用測位システム受信機に提供される。ミサイルにこの情報を提供することによって、ミサイルはP(Y)信号を取得でき、これによってミサイルは他の方法に比べてその位置をより迅速に判断することが可能となる。

(もっと読む)

カーボン・ナノチューブを浸出したファイバとその製造方法

【課題】カーボン・ナノチューブを浸出したファイバとそれを形成する方法を提供する。

【解決手段】 本発明のカーボン・ナノチューブを浸出したファイバを形成する方法は、(a) カーボン・ナノチューブを形成する触媒を、母材であるファイバの表面上に配置するステップと、(b) 前記カーボン・ナノチューブを前記母材であるファイバ上で直接合成するステップとを有する。前記(a)ステップは、(a1) 前記触媒の溶液を液状に形成するステップと、(a2) 前記触媒の溶液を前記母材であるファイバ上に噴霧するステップとを有する。

(もっと読む)

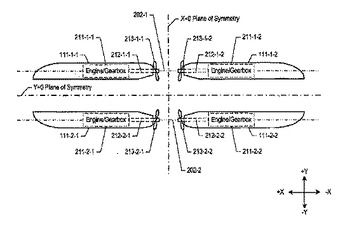

プロペラを中央に搭載した複数の艇体を有する船舶

4個の高いフロード(Froude)数(船首に2個、船尾に2個、左舷に2個、右舷に2個)の艇体を有するダブルエンド型のフェリーを開示した。各艇体は、独立したエンジンを有し、これにより、プロペラシャフトと、船の中央に配置されたプロペラとを駆動する。右舷の複数のプロペラシャフトは、左舷の複数のプロペラシャフトと同様、同軸上にある。右舷の複数のプロペラは、互いに向かい合い、反対方向に回転し、左舷のプロペラについても同様である。プロペラは、可変ピッチのプロペラである。フェリーが前進から後退に、後退から前進に、進行方向を変える時に、右舷のプロペラのピッチが変わる。これにより、フェリーは、前進と同様に後退も効率よくできる。また、フェリーが前進から後退に、後退から前進に、進行方向を変える時に、左舷のプロペラのピッチも変わる。  (もっと読む)

(もっと読む)

キャビテーションを遅延または低減するための後流適応プロペラ駆動機構

【課題】キャビテーションを遅延または低減するための後流適応プロペラ駆動機構を構成することである。

【解決手段】キャビテーションを遅延または低減するための後流適応プロペラ駆動機構は、前部および後部を備え、さらに外殻の後部で回転するように取り付けた後流適応プロペラを有し、水を横切る外殻の前進によって生じる後流内で回転できるようにする。  (もっと読む)

(もっと読む)

改善された計算アーキテクチャを有する計算マシン、関連システム、並びに、方法

計算マシンは第1バッファと該バッファと結合されたプロセッサとを含む。プロセッサは、アプリケーション、第1データ転送オブジェクト、並びに、第2データ転送オブジェクトを実行し、アプリケーションの制御下でデータを発行し、第1データ転送オブジェクトの制御下でその発行されたデータをバッファにロードし、そして、第2データ転送オブジェクトの制御下でバッファからその発行されたデータを検索する。代替的には、プロセッサは、データを検索して、第1データ転送オブジェクトの制御下でその検索されたデータをバッファにロードし、第2データ転送オブジェクトの制御下でバッファからそのデータをアンロードし、そして、アプリケーションの制御下でそのアンロードされたデータを処理する。計算マシンがプロセッサと結合されたハードウェアに組み込まれたパイプライン加速器を含むピア−ベクトル・マシンである場合、バッファ及びデータ転送オブジェクトはアプリケーション及び加速器の間でのデータの転送を補助する。 (もっと読む)

改善された計算アーキテクチャ、関連システム、並びに、方法

ピア−ベクトル・マシンはホストプロセッサとハードウェアに組み込まれたパイプライン加速器とを含む。ホストプロセッサはプログラムを実行し、該プログラムに応じてホスト・データを生成し、そしてパイプライン加速器はそのホスト・データからパイプライン・データを生成する。代替的には、パイプライン加速器はパイプライン・データを生成し、ホストプロセッサはそのパイプライン・データからホスト・データを生成する。ピア−ベクトル・マシンはプロセッサ及びパイプライン加速器の両方を含むので、しばしば、プロセッサだけ或は加速器だけを含むマシンよりもより効率的にデータを処理できる。例えば、ホストプロセッサが意思決定を実行すると共に数学的に非集中的な演算を実行し、そして加速器が非意思決定を実行すると共に数学的に集中的な演算を実行するようにピア−ベクトル・マシンを設計できる。数学的に集中的な演算を加速器にシフトすることによって、ピア−ベクトル・マシンは、しばしば、所与のクロック周波数で、プロセッサだけのマシンがデータを処理できる速度を凌ぐ速度でデータを処理できる。  (もっと読む)

(もっと読む)

改善された計算アーキテクチャ用パイプライン加速器、関連システム、並びに、方法

パイプライン加速器はメモリと該メモリと結合されたハードウェアに組み込まれたパイプライン回路とを含む。このハードウェアに組み込まれたパイプライン回路は、データを受信し、前記データを前記メモリにロードし、前記メモリから前記データを検索し、前記検索されたデータを処理し、そして前記処理されたデータを外部ソースに提供するように動作できる。加えて或は代替例で、ハードウェアに組み込まれたパイプライン回路は、データを受信し、前記受信されたデータを処理し、前記処理されたデータを前記メモリにロードし、前記メモリから前記処理されたデータを検索し、そして前記検索された処理データを外部ソースに提供するように動作できる。パイプライン加速器がピア-ベクトル・マシンの一部としてのプロセッサと結合されている場合、前記メモリは前記ハードウェアに組み込まれたパイプライン回路と前記プロセッサが実行するアプリケーションとの間におけるデータの転送−単向性であろうが二方向性であろうが−を補助する。 (もっと読む)

プログラマブル回路、関連計算マシン、並びに、方法

プログラマブル回路は、外部ソースからコンフィギュレーション・データを受信し、ファームウェアをメモリに記憶してから、そのメモリからそのファームウェアをダウンロードする。そうしたプログラマブル回路は、計算マシン等のシステムにプログラマブル回路のコンフィギュレーションを変更させて、コンフィギュレーション・メモリをマニュアルで再プログラムする必要性をなくしている。例えば、もしプログラマブル回路がパイプライン加速器の部分であるFPGAであれば、その加速器と結合されたプロセッサはFPGAのコンフィギュレーションを変更できる。より詳細には、プロセッサはコンフィギュレーション・レジストリから変更されたコンフィギュレーションを表すファームウェアを検索し、そのファームウェアをFPGAに送信し、次いで該FPGAがそのファームウェアを電気的に消去可能でプログラム可能な読み取り専用メモリ(EEPROM)等のメモリに記憶する。次に、FPGAはメモリからそのコンフィギュレーション・レジスタにそのファームウェアをダウンロードし、よってそれ自体を変更されたコンフィギュレーションを有するように再構成する。 (もっと読む)

電磁ミサイル発射装置

従来技術の問題点を回避するミサイルを発射する装置を提供する。本発明の装置は、電磁カタパルトを有し、ミサイルのエンジンに点火する前に、航空飛行に達成する為の十分な速度でもって発射台からミサイルを発射する。

(もっと読む)

(もっと読む)

11 - 19 / 19

[ Back to top ]