メアーズ テクノロジーズ, インコーポレイテッドにより出願された特許

1 - 10 / 25

バンド設計超格子を有する半導体装置

【課題】例えば大きな電荷キャリア移動度を有する半導体装置を提供する。

【解決手段】半導体装置は、複数の積層された層群を有する超格子を有する。また装置は、電荷キャリアが積層された層群と平行な方向に超格子を通って輸送される領域を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

半導体装置を製作する方法

【課題】例えば大きな電荷キャリア移動度を有する半導体装置を製作する方法を提供する。

【解決手段】複数の積層された層群を有する超格子を形成するステップによって、半導体装置を製作する方法である。また当該方法は、前記超格子を通って、前記積層された層群と平行な方向に、電荷キャリアの輸送が生じる領域を形成するステップを有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。前記エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取りこまれた、少なくとも一つの非半導体分子層を有し、前記超格子は、超格子が存在しない場合に比べて、前記平行な方向において大きな電荷キャリア移動度を有する。また前記超格子は、共通のエネルギーバンド構造を有しても良い。

(もっと読む)

堆積途中でアニーリングを行うことによってバンドが設計された超格子を有する半導体素子の作製方法

半導体素子の作製方法は、各々が複数の層からなる複数の群を積層した状態で有する超格子を作製する工程を有して良い。複数の層からなる群の各々は、基礎となる半導体部分を画定する、複数の積層された基礎となる半導体分子層、及び隣接する基礎となる半導体部分の結晶格子の内部に束縛された少なくとも1の非半導体分子層を有して良い。当該方法はまた、その超格子が完全に形成される前に少なくとも1回のアニーリングを行う工程をも有して良い。  (もっと読む)

(もっと読む)

絶縁体上に半導体が存在する配置及び超格子を有する半導体素子並びに関連方法

半導体素子は、SOI基板、該基板に隣接する絶縁層、及び前記基板に対向する前記絶縁層の面に隣接する半導体層を有して良い。当該素子は、前記半導体層上に存在するソースとドレイン領域、前記半導体層に隣接して前記ソースとドレイン領域間で延在することでチャネルを画定する超格子、前記超格子は、複数の層からなる複数の積層群を含んで良い。前記超格子の層が構成する各群は、基本半導体部分を画定する複数の積層された基本半導体分子層、及びエネルギーバンド修正層を有して良い。該エネルギーバンド修正層は隣接する基本半導体部分の結晶格子内部に束縛された少なくとも1層の非半導体分子層を有して良い。前記超格子はゲルマニウムを含んで良い。  (もっと読む)

(もっと読む)

ドーパントを阻止する超格子を有する半導体素子及び関連方法

半導体素子は、少なくとも1つの金属-酸化物電界効果型トランジスタ(MOSFET)を有して良い。前記少なくとも1つのMOSFETは、主部、該主部に隣接するチャネル層、及び前記主部と前記チャネル層との間に設けられたドーパントを阻止する超格子を有して良い。前記ドーパントを阻止する超格子は、複数の層からなる複数の積層群を含んで良い。前記ドーパントを阻止する超格子の層が構成する各群は、基本半導体部分を画定する複数の積層された基本半導体分子層、及び隣接する基本半導体部分の結晶格子内部に束縛された少なくとも1層の非半導体分子層を有して良い。  (もっと読む)

(もっと読む)

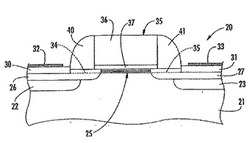

超格子チャネルを有する浮遊ゲートメモリセルを含む半導体素子及び関連方法

半導体素子は、半導体基板(21)及び少なくとも1つの不揮発性メモリセルを有して良い。前記少なくとも1つのメモリセルは互いに離れて存在するソース領域とドレイン領域(26,27)、並びに該ソース領域とドレイン領域との間に設けられた、前記半導体基板上の複数の層からなる複数の積層群を有する超格子チャネル(25)を含んで良い。前記超格子チャネルの層が構成する各群は、基本半導体部分を画定する複数の積層された基本半導体分子層、及び前記基本半導体部分上に存在するエネルギーバンド修正層を有して良い。前記エネルギーバンド修正層は、隣接する基本半導体部分の結晶格子内部で束縛された少なくとも1層の非半導体分子層を有して良い。浮遊ゲート(37)は前記超格子チャネルに隣接して良い。制御ゲート(39)は第2ゲート絶縁層(38)に隣接して良い。  (もっと読む)

(もっと読む)

拘束されたスピントロニクスドーパントを有するスピントロニクスデバイス、及びその製造方法

スピントロニクスデバイスは、少なくとも1つの超格子と、それに結合された少なくとも1つの電気コンタクトとを有し、前記少なくとも1つの超格子は複数のレイヤー群を含む。各レイヤー群は、結晶格子を有するベース半導体部分を画成する複数の積層されたベース半導体モノレイヤー、隣接し合うベース半導体部分の結晶格子内に拘束された少なくとも1つの非半導体モノレイヤー、及びスピントロニクスドーパントを含み得る。スピントロニクスドーパントは、前記少なくとも1つの非半導体モノレイヤーによって、ベース半導体部分の結晶格子内に拘束され得る。一部の実施形態において、超格子の反復構造は必要とされない。  (もっと読む)

(もっと読む)

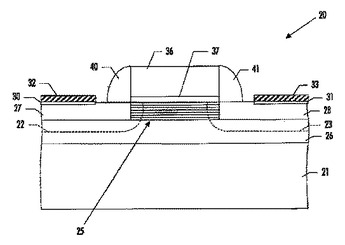

超格子領域を含む電界効果半導体デバイス

半導体デバイス(20)は、基板(21)と、該基板内の、それらの間にチャネル領域(24)を画成する空間的に隔てられたソース領域(23)及びドレイン領域(27)とを含んでいる。この基板は、チャネル領域及び/又はドレイン領域内に、空間的に隔てられた複数の超格子を有する。各超格子は積層された複数の層群を含んでおり、各層群は、ベース半導体部分を画成する積層された複数のベース半導体モノレイヤーと、その上の少なくとも1つの非半導体モノレイヤーとを含んでいる。上記の少なくとも1つの非半導体モノレイヤーは、隣接し合うベース半導体部分の結晶格子内に拘束されていてもよい。この半導体デバイスは、例えば、DMOSデバイスとし得る。  (もっと読む)

(もっと読む)

表側の歪んでいる超格子層、裏側の応力層を有する半導体装置及び関連する方法

半導体装置は、表面及び裏面を有する半導体基板と、半導体基板の表面に隣接し、複数の層の積層された群を有する、歪みが導入された超格子層と、半導体基板の裏面における、半導体基板と異なる材料を有する応力層と、を有する。歪みが導入された超格子層の各々の層の群は、ベース半導体部分を規定する複数の積層されたベース半導体単層と、隣接するベース半導体部分の結晶格子内に拘束されている少なくとも1つの非半導体単層とを有する。  (もっと読む)

(もっと読む)

非半導体モノレイヤーを有するチャネルを含む半導体デバイス、及びその製造方法

半導体デバイスは、半導体基板及びその上の少なくとも1つのMOSFETを含んでいる。このMOSFETは、空間的に隔てられたソース領域及びドレイン領域、ソース領域とドレイン領域との間のチャネル、及びチャネルの上に位置しチャネルとの界面を画成するゲートを含んでいる。ゲートは、チャネルの上に位置するゲート誘電体と、ゲート誘電体の上に位置するゲート電極とを含んでいる。また、このチャネルは、積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体モノレイヤーの結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。上記少なくとも1つの非半導体モノレイヤーは、チャネルとゲート誘電体との間の界面に対しておよそ4−100モノレイヤーの深さに位置付けられている。  (もっと読む)

(もっと読む)

1 - 10 / 25

[ Back to top ]