オヴォニクス,インコーポレイテッドにより出願された特許

1 - 10 / 20

優れたデータ保持特性を有する可変抵抗材料

【課題】高温において優れたデータ保持特性を示す可変抵抗メモリ組成物及びデバイスを提供する。

【解決手段】組成物は、可変抵抗成分と不活性成分とを含む複合材料である。可変抵抗成分は相変化材料を含み、不活性成分は誘電材料を含む。相変化材料はGe、Sb、及びTeを含む。Sbの原子濃度は3%から16%であり、及び/又はSb/Ge比は0.07から0.68であり、及び/又はGe/Te比は0.6から1.1であり、及び/又は誘電成分の濃度(その構成元素の原子濃度の合計)は95%から50%である。組成物は高い10年データ保持温度及び高温における長いデータ保持時間を示す。

(もっと読む)

相変化メモリデバイスに電極を形成する方法

サブリソグラフィックな寸法又は高アスペクト比を含む、小寸法の開口内に電極材料を均一に形成する方法を提供する。この方法は、内部に形成された開口を有する絶縁層を提供するステップと、開口の上部及び内部に非等質的導電又は準抵抗性材料を形成するステップと、導電材料を移動化して開港内に圧縮するステップとを有する。この方法は、導電又は準抵抗性材料における空孔又は欠陥密度を堆積されたままの状態に対して低減する。移動化するステップは、押出又は熱的リフローによって達成され、空隙又は欠陥を合体、崩壊、染み透り又は他の方法によって堆積したままの導電又は準抵抗性材料から除去する。  (もっと読む)

(もっと読む)

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

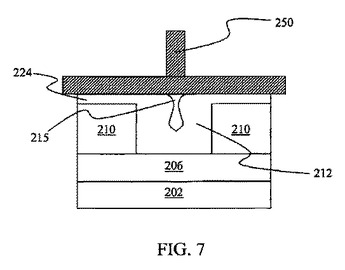

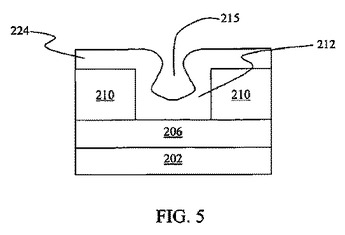

閉じ込め層を有する活物質素子

活物質電子素子が、閉じ込め層とともに説明される。素子は、上部及び下部電極と電気的に接続した活性カルコゲニド材料、ニクティド材料又は相変化物質を含んでいる。閉じ込め層は、製造又は動作の間に素子が高温に暴露されたときに活物質から揮発した物質の脱出を防ぐ活物質上に形成された閉じ込め層を含んでいる。閉じ込め層は、処理環境又は周囲の環境における反応種から保護することによって、活物質の化学汚染をさらに防いでいる。閉じ込め層と、活物質と閉じ込め層との間に形成された中間層とは、活物質の揮発を防ぐように十分な低温で形成される。一旦閉じ込め層が形成されると、素子は、活物質の組成又は構造の完全性を損なうことなく高温環境又は化学侵食環境のもとに置くことができる。閉じ込め層を含むことにより、素子の動作回数寿命が2の次数の強度を超えて延びることが示される。  (もっと読む)

(もっと読む)

改善動作特性を有する多層カルコゲナイド及び関連デバイス

多層カルコゲナイドのメモリ又はスイッチングデバイスである。当該デバイスは、第1端子と第2端子との間に配置された活性領域を含む。当該活性領域は第1層及び第2層を含む。当該層の一方は、オペレーショナル成分及びプロモータ成分を含むヘテロジニアス層である。他方は、ホモジニアス又はヘテロジニアス層である。実施例では、オペレーショナル成分はカルコゲナイド又は相変化材料であり、プロモータ成分は絶縁又は誘電材料である。プロモータ成分を含めることにより、リセット電流の低減又はフォーメーション必要性の最小化のような有利な性能特性が得られる。  (もっと読む)

(もっと読む)

相変化物質をプログラミングする方法

【課題】 記憶装置に好適に利用される相変化物質をプログラミングする方法を提供すること。

【解決手段】 本発明の一特徴は、相変化物質をプログラミングする方法であって、設定された抵抗を有する設定抵抗状態と、リセットされた抵抗を有するリセット抵抗状態と、前記設定された抵抗より大きく、前記リセットされた抵抗より小さい抵抗を有する複数の中間抵抗状態とを含む複数の抵抗状態を有する相変化物質を提供するステップと、第1抵抗を有する前記相変化物質の第1中間抵抗状態を含む前記相変化物質の第1メモリ状態を規定するステップと、前記第1抵抗を上回る第2抵抗を有する前記相変化物質の第2中間抵抗状態を含む前記相変化物質の第2メモリ状態を規定するステップと、前記相変化物質を前記第1メモリ状態と前記第2メモリ状態との一方にプログラミングするステップとを有し、前記プログラミングするステップは、第1プログラミング信号と第2プログラミング信号とを前記相変化物質に印加する方法に関する。

(もっと読む)

ゲルマニウムまたはテルル含有量の少ないカルコゲナイドデバイス及びカルコゲナイド材料

広範囲のリセット状態の抵抗に対して、高速動作すなわち、短いリセットパルス時間を示すカルコゲナイド材料及びカルコゲナイドメモリデバイス。

本発明のカルコゲナイド材料を含む電気デバイスは、リセット状態とセット状態の間の抵抗比が高い場合に、リセット状態からの迅速な変化ができるようにする。本発明のデバイスは、デバイスの高速動作スピードを保ちつつ、メモリ状態の高い抵抗比及び改良された読み出し性を提供する。カルコゲナイド材料は、Ge、Sb及びTeを含み、Ge及び/またはTeの含有量が一般的に用いられるGe2Sb2Te5カルコゲナイド組成に比較して少ない。本発明の一実施形態においては、Ge、Sb、Teの含有量は、Geが11〜22原子%、Sbが22〜65原子%、Teが28〜55原子%である。好ましい実施形態においては、Ge、Sb、Teの含有量は、Geが15〜18原子%、Sbが32〜35原子%、そして、Teが48〜51原子%である。  (もっと読む)

(もっと読む)

相変化メモリセルにおける相変化層の成形方法

【課題】

本発明は、相変化メモリセルにおける相変化層の成形方法を提供する。

【解決手段】

相変化メモリセルは、相変化材料から成る相変化層を半導体ボディ上に含む。ハードマスク構造が相変化層上に形成され、レジストマスクがハードマスク構造上に形成される。レジストマスクを用いてハードマスク構造を成形することによってハードマスクが形成される。ハードマスクを用いて相変化層が成形される。相変化層を成形する前にレジストマスクが除去される。

(もっと読む)

リセットセル閾値デバイスをトリガすることなく相変化メモリを読み出す方法

【課題】従来技術の問題点を解決する方法、メモリ及びシステムを提供する。

【解決手段】相変化メモリは、読み出し妨害の可能性を低減するよう読み出されうる。読み出し妨害は、例えば、リセットデバイスが、その閾値デバイスをトリガさせる電圧へと上昇する場合に生じうる。閾値デバイスのトリガは、リセットデバイスを設定デバイスへと変換する変位電流を作る。リセットセルが、閾値デバイスのトリガをもたらしうる電圧に決して達しないことを確実にすることによって、読み出し妨害は低減されうる。

(もっと読む)

メモリを読み出すためのビット特定基準レベルの使用

【課題】メモリセルの任意の配列、組又はブロックに亘るビット間の変化に、より依存しない読み出し窓又は読み出しマージンを作ることが可能な方法等を提供する。

【解決手段】選ばれたビットに1つの読み出し電流を用いてアクセスすることにより導かれる電圧は、読み出し電流が変えられた後に、トリガーされていない相変化メモリの選ばれたビットを読み出すために使用される。結果として、異なる基準電圧は、抵抗値の低い選ばれたセルに対する抵抗値の高い選ばれたセルの状態を検知するために使用されても良い。結果として得られる読み出し窓又はマージンは、幾つかの実施例において改善されうる。

(もっと読む)

1 - 10 / 20

[ Back to top ]