スパンジョン・リミテッド・ライアビリティ・カンパニーにより出願された特許

1 - 10 / 37

電気経路およびメモリセルのフローティングゲートから電荷を消去する方法

【課題】高度にドープされかつ高いエネルギで、薄くドープされた分離ウェル中に注入される埋込層を提供する。

【解決手段】埋込層(500)はそれが設けられるウェルと同じ導電ドーパントでドープされる。埋込層(500)はフラッシュEPROMセルのチャネルの大きさを低減し、より高いアレイ密度を提供することを可能にする。フラッシュEPROMセルのチャネルは、埋込層が(500)フラッシュEPROMセルのチャネル間に低抵抗経路を設けるのでゲートとセルの基板との間に電圧電位差を与えることによって消去が行なわれることを可能にするまでフラッシュEPROMのチャネルは低減される。

(もっと読む)

低抵抗共通ソースおよび高電流駆動能力を有するメモリセルアレイ

この抵抗メモリアレイには、基板と、基板にある複数のソース領域と、複数のソース領域を接続する導体とが含まれ、導体は基板に隣接して位置決めされ、複数のソース領域とともに共通ソースを形成する。1つの実施例においては、導体は、断面がT字型の細長い金属体(378)である。別の実施例においては、導体は、プレート状の金属体(766)である。  (もっと読む)

(もっと読む)

犠牲マスキング構造を用いた半導体装置の製造方法

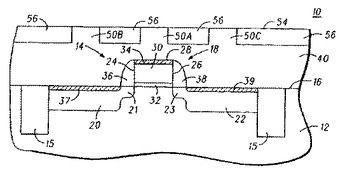

犠牲マスキング構造(50)を用いた半導体装置(10)の製造方法を提供する。半導体デバイスは半導体基板(12)から形成され、誘電材料からなる層(40)は半導体基板(40)および半導体デバイスの上に形成される。誘電材料からなる層(40)は、半導体基板(12)上に直接に形成される場合もあれば、中間層によって半導体基板(12)から間隔があいている場合もある。側壁を有するポストまたは凸部(50)が、誘電材料からなる層(40)から形成される。好ましくは誘電材料からなる層(40)とは異なる電気絶縁材料(52)がポスト(50)の側壁に隣接して形成される。電気絶縁材料(52)は平坦化され、ポスト(50)が除去されて、半導体デバイスの一部または中間層材料の一部を露出させ得る開口を形成する。導電性材料が開口に形成される。  (もっと読む)

(もっと読む)

バンクおよびセクタに配置されるメモリアレイならびに関連の復号器

メモリアレイ(150)は複数のメモリバンク(B)を含み、各々が複数のセクタ(S)および複数のセクタ復号器を有し、各セクタ復号器はセクタ(S)に動作可能に関連付けられる。第1の複数の線が第1の信号を与え、第2の複数の線が第2の信号を与える。第1の信号を受けるため、および第1の単一の線によってメモリバンク(B)のセクタ復号器に第1のアドレス信号を与えるために、第1の復号器装置が第1の複数の線に動作可能に関連付けられる。第2の信号を受けるため、および第2の単一の線によってメモリバンク(B)のセクタ復号器に第2のアドレス信号を与えるために、第2の復号器装置が第2の複数の線に動作可能に関連付けられる。  (もっと読む)

(もっと読む)

プログラムされるべきビットを予め定めるためのプログラミングウインドウおよびDC−DC変換器を使用する高性能のフラッシュメモリデバイス

メモリセル(201)のアレイ(102)を含む不揮発性メモリアレイをプログラムするための方法を提供し、各メモリセル(201)は、基板(310)と、制御ゲート(328)と、電荷蓄積素子(322)と、ソース領域(203)と、ドレイン領域(202)とを含む。この方法は、アレイにおいてプログラムされるべき予め定められた数のビットを含むプログラミングウインドウを受取ること(700)と、予め定められた数のビットのうちどれをメモリアレイにおいてプログラムすべきであるかを判断すること(703)とを含む。予め定められた数のビットは、アレイにおける対応するメモリセルに同時にプログラムされる(705)。アレイにおける予め定められた数のビットのプログラミング状態は同時に検証される(708)。  (もっと読む)

(もっと読む)

仮想接地メモリアレイのビット線間スペーサ

1つの例示的な実施例によると、基板(434)内に位置するビット線(402、404、406)を含む仮想接地メモリアレイの製造方法は、2つの隣接するビット線(402、404、406)同士の間の基板(434)内に少なくとも1つの凹部(436、438)を形成するステップを備え、少なくとも1つの凹部(436、438)は仮想接地メモリアレイのビット線コンタクト領域(132)内に位置し、少なくとも1つの凹部(436、438)は基板(434)内の側壁(452)および底面(454)を規定する。少なくとも1つの凹部(436、438)を形成するステップ(370)は、ハードマスク部分(208、210、212)をマスクとして使用するステップを含み、ハードマスク部分(208、210、212)の各々はビット線(202、204、206)の上に位置する。本方法は、少なくとも1つの凹部(436、438)内にスペーサ(460、462)を形成するステップ(374)をさらに含み、スペーサ(460、462)は、隣接するビット線(402、404、406)間のビット線からビット線へのリークを低減する。本方法は、少なくとも1つの凹部(436、438)を形成するステップ(370)の前にスタックゲート構造(114、116、118)を形成するステップをさらに含み、各スタックゲート構造(114、116、118)はビット線(102、104、106)の上に、かつビット線に垂直に位置する。  (もっと読む)

(もっと読む)

プログラム速度が改善したマルチビットフラッシュメモリ

メモリセル(201)のアレイを含む不揮発性メモリアレイ(102)をプログラムするための方法を提供し、各メモリセル(201)は、基板(315)と、制御ゲート(328)と、少なくとも2つの独立した電荷を蓄積するための少なくとも2つの電荷蓄積エリア(432,433)を有する電荷蓄積素子(322)と、ソース領域(203)と、ドレイン領域(202)とを含む。この方法は、少なくとも1つのメモリセルを高速メモリセルとして指定すること(802)と、少なくとも2つの電荷蓄積エリア(432,433)の第1の電荷蓄積エリアをプログラムされた状態にすることによって高速メモリセル(201)を事前調整すること(804)と、その後はるかに速い速度で第2のエリア上でのプログラミングを可能にすることとを含む。  (もっと読む)

(もっと読む)

集積回路テストソケット

集積回路、特にBGAパッケージ中の集積回路をテストするのに用いられるテストソケットを提供する。テストソケットは、ベース部材と、ベース部材に対して上方位置および下方位置の間で上下動するように構成された被覆部材とを備える。ベース部材と被覆部材との間にはばねが配置され、被覆部材を上方位置に付勢するように構成される。ベース部材および被覆部材にレバーが連結され、被覆部材が下方位置にあるときには開位置に旋回し、被覆部材が上方位置にあるときには閉位置に旋回して、集積回路をベース部材内に閉じ込めるように構成される。  (もっと読む)

(もっと読む)

ナノスケール抵抗記憶装置のプログラミング、消去、読出のためのページバッファアーキテクチャ

抵抗記憶装置(30)のアレイの抵抗記憶装置をプログラミングおよび消去する方法において、1つのコマンドに応じて、高電流がプログラミング機能および消去機能双方について与えられ、前の状態から変わるべき状態にある記憶装置(30)のみがプログラミングおよび消去される。  (もっと読む)

(もっと読む)

誘電体の破壊によってプログラムすることが可能なリードオンリメモリアレイ

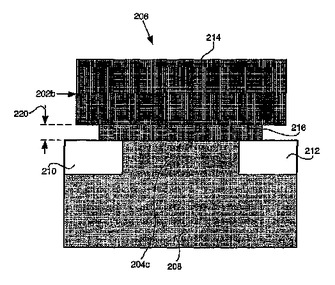

一実施の形態によれば、プログラムすることが可能なROMアレイは、基板に位置付けられた少なくとも1のビット線(204c)を含んでいる。また、プログラムすることが可能なROMアレイは、少なくとも1のビット線(204c)を横切るように位置付けられた少なくとも1のワード線(202b)を含んでいる。また、プログラムすることが可能なROMアレイは、少なくとも1のビット線(204c)と少なくとも1のワード線(202b)との交差点に位置付けられたメモリセル(206)を含み、メモリセル(206)は、少なくとも1のビット線(204c)と少なくとも1のワード線(202b)との間に位置付けられた誘電体領域(216)を含んでいる。プログラミング動作は、誘電体領域(216)を破壊することによって、メモリセル(206)を第1の論理状態から第2の論理状態へ変化させる。プログラミング動作は、メモリセル(206)をダイオードとして動作させる。メモリセル(206)の抵抗は、メモリセル(206)が第1または第2の論理状態を有しているかどうかを決定するために、読出動作において測定され得る。  (もっと読む)

(もっと読む)

1 - 10 / 37

[ Back to top ]