ミシシッピ ステート ユニバーシティーにより出願された特許

1 - 4 / 4

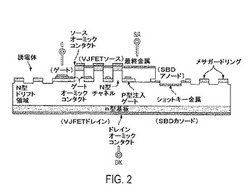

シリコンカーバイドから製造されるモノリシックな縦型接合型電界効果トランジスタおよびショットキーバリアダイオード、および、その製造方法

【課題】縦型接合型電界効果トランジスタ(JFET)およびショットキーバリアダイオード(SBD)を備えるスイッチング素子を提供すること。

【解決手段】自己整合縦型接合型電界効果トランジスタを、エッチング注入ゲートおよび集積逆並列ショットキーバリアダイオードと組み合わせたスイッチング素子が、記載されている。ダイオードのアノードは、漂遊インダクタンスによる損失を低減するために、デバイスレベルでトランジスタのソースに接続される。SBDアノード領域におけるSiC表面は、SBDのターンオン電圧と関連するパワー損失が低減されるよう低いショットキーバリア高さを達成するために、乾式エッチングによって調整される。

(もっと読む)

炭化ケイ素のエピタキシャル成長方法

【解決手段】 化学気相堆積法(chemical vapor depositionCVD)を用いた炭素ケイ酸のエピタキシャル成長方法が提供される。この方法は、ハロゲン化炭素前駆体を利用し、更にケイ素及び炭素を含むハロゲン含有中間体化学生成物間の気相相互作用制御するものである。また、デバイス品質であるエピタキシャル層を、低い成長温度で尚且つ軸上又は低いオフ角の基板表面上にて達成される可能性が確認された。当該成長方法は、SiC基板表面の非ケイ素カートリッジ領域に形成されるウインドウの中に成長を制限させることにより、所望の形と大きさのSiCデバイス領域の形成に適用可能である。本願明細書に記載された当該発明を適用させることにより、高品質炭化ケイ素物質及びデバイスの製造に大きな利益を与えるものである。 (もっと読む)

埋込みゲートを有する垂直チャネル接合型電界効果トランジスタおよび製造方法

半導体装置およびその装置の製造方法を説明する。装置は、SiCにおいて実施され、エピタキシャルに成長したn型ドリフト、p型溝ゲート領域、およびp−溝ゲート領域の上にあるn型のエピタキシャルに再成長したチャネル領域を含んでよい。ソース領域は、チャネル領域の上でエピタキシャルに再成長したり、選択的にチャネル領域に注入してよい。その後、ソース、ゲートおよびドレイン領域とのオーム接点が形成されてよい。装置は、ガードリング、接合型ターミネーション・エクステンション(JTE)、またはその他の適当なp−n遮断構造などのエッジターミネーション構造を含んでよい。装置は異なる閾値電圧で加工してよく、同じチャネルドーピングに対して、減少および増加モードの両方の操作を行ってよい。装置は、デジタル、アナログ、およびモノリシックのマイクロ波集積回路で個別電力トランジスタとして使用してよい。  (もっと読む)

(もっと読む)

シリコンカーバイドから製造されるモノリシックな縦型接合型電界効果トランジスタおよびショットキーバリアダイオード、および、その製造方法

自己整合縦型接合型電界効果トランジスタを、エッチング注入ゲートおよび集積逆並列ショットキーバリアダイオードと組み合わせたスイッチング素子が、記載されている。ダイオードのアノードは、漂遊インダクタンスによる損失を低減するために、デバイスレベルでトランジスタのソースに接続される。SBDアノード領域におけるSiC表面は、SBDのターンオン電圧と関連するパワー損失が低減されるよう低いショットキーバリア高さを達成するために、乾式エッチングによって調整される。  (もっと読む)

(もっと読む)

1 - 4 / 4

[ Back to top ]