ディー−ウェイブ システムズ,インコーポレイテッドにより出願された特許

1 - 10 / 16

超伝導集積回路のためのシステムおよび方法

【課題】超伝導集積回路の要素間の相互インダクタンスの望まない不一致を緩和する。

【解決手段】超伝導集積回路は、内部誘導結合要素と、その長さの少なくとも一部分に沿って内部誘導結合要素を囲む外部誘導結合要素とを有する磁束トランスを含み得る。磁束トランスは、第1の誘導結合要素と第2の誘導結合要素との間の相互インダクタンスが、第1の外部誘導結合要素から第1の内部誘導結合要素を分離する距離にほぼ直線的に比例するように同軸様形状を有し得る。第1の誘導結合要素および第2の誘導結合要素の少なくとも1つは、超伝導量子ビットなどの超伝導プログラマブル素子と結合することができる。

(もっと読む)

超伝導集積回路を製造するためのシステムおよび方法

様々な技法および装置が、例えば量子コンピュータで有用となることがある超伝導回路および構造、例えばジョセフソン接合の製造を可能にする。例えば、超伝導することができる2つの要素または層の間に誘電体構造または層が挿間された、低い磁束ノイズの三層構造を製造することができる。超伝導バイアが、ジョセフソン接合の上に直接位置することがある。平坦化された誘電体層上に構造、例えばジョセフソン接合を担持することができる。構造から熱を除去するためにフィンを採用することができる。超伝導することができるバイアは、約1マイクロメートル未満の幅を有することができる。構造は、例えばバイアおよび/またはストラップコネクタによって抵抗器に結合することができる。  (もっと読む)

(もっと読む)

磁場測定用のシステム、方法および装置

SQUIDは局所磁場を検出し得る。様々なサイズ、従って様々な感度のSQUIDは、異なる大きさの磁場を検出し得る。SQUIDは、様々な向きにおいて、例えばチップまたはウエハの直交する基準座標系に沿って磁場を検出するように向けられ得る。SQUIDは、超伝導プロセッサ(例えば、超伝導量子プロセッサ)と同じチップまたはウエハ上に形成または保持され得る。磁場の測定によって補償すること、例えば補償コイルおよび/またはヒータを介して補償磁場を調整して、システムの選択した部分を温めることが可能となる。SQIFを、型にはまらない格子構造を有するSQUIDとして実装し得る。動作可能なSQIFの製造の成功は、型にはまらない格子構造の各アームにおいて直列に複数のジョセフソン接合を組み込むことによって促進され得る。 (もっと読む)

量子プロセッサ素子の能動的補償のためのシステム、方法および装置

本装置と方法は量子プロセッサの超伝導素子の望ましくない相違の能動的補償を可能にする。量子ビットは主複合ジョセフソン接合(CJJ)構造を備えることができ、主複合ジョセフソン接合(CJJ)構造は主CJJ構造におけるジョセフソン接合非対称性の補償を可能にするために少なくとも1つの第1の副CJJ構造を備えることができる。量子ビットは、チューニング可能な容量を与えるために第1のCJJ構造と並列に結合された直列LC回路を備えることができる。量子ビット制御システムは、量子ビットループのインダクタンスをチューニングする手段、例えば量子ビットループに誘導結合されプログラミングインターフェースにより制御されるチューニング可能結合器あるいは量子ビットループと直列に結合されプログラミングインターフェースにより制御されるCJJ構造を備えることができる。 (もっと読む)

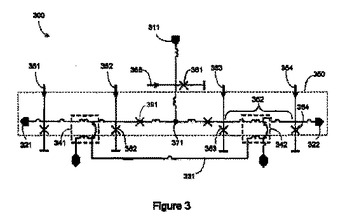

超伝導デマルチプレクサ回路用のシステム、方法、および装置

デマルチプレクサ回路用のスイッチングセルは超伝導入力信号経路、少なくとも2個の超伝導出力信号経路、および交差ノードと出力信号経路との各端部の間に配置されたトランスを含む。トランスを介して印加された磁束は信号が伝播する方向に影響を及ぼすことができる。スイッチングセルはまた、電源入力ノードを含んでいてもよい。スイッチングセルは、各種の構成、例えば2分木またはH木に配置されてもよい。超伝導インダクタラダー回路はデジタル/アナログ変換を実行することができる。個別スイッチングセルと共に磁束記憶構造を用いてもよい。ラッチング量子ビットを用いてもよい。カスケードエラーを減少または除去すべくスイッチングセルのバッファ段を用いてもよい。  (もっと読む)

(もっと読む)

量子プロセッサを較正し、制御し、動作させるためのシステム、方法および装置

量子アニーリングは、量子プロセッサの量子ビット(例えば、超伝導量子プロセッサの超伝導磁束量子ビット)に無秩序項を付加し徐々に取り除く工程を含むことができる。問題ハミルトニアンは量子ビットに制御信号を印加することにより設定され得る。展開ハミルトニアンは無秩序項を付加することにより、そして無秩序項を徐々に取り除くことによりアニーリングすることにより、設定される。量子ビット内の永久電流の変化を補正することができる。乗算器は、例えばそれぞれのスケーリング係数を印加することにより様々な量子ビットとグローバル信号線間の結合を仲介することができる。2つのグローバル信号線は、通信的に結合された一対の量子ビットのそれぞれの量子ビットに結合するために互いに入り組んだパターンで構成することができる。規定信号に対する互いの応答を測定するために量子ビット対を通信的に分離して使用することができる。 (もっと読む)

アナログ処理用のシステム、装置、および方法

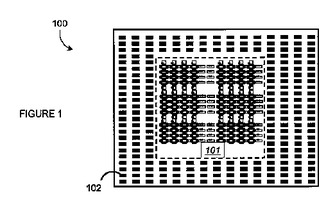

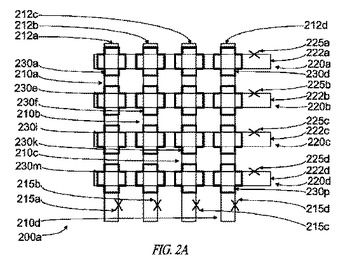

システムは、互いに交差する第1および第2量子ビットと、第1および第2量子ビットの少なくとも一部を含む周辺部を有する第1カプラとを含んでいてよく、第1カプラは、第1および第2量子ビットを互いに強磁性的または反強磁性的に結合すべく動作可能である。多層コンピュータチップは、第1金属層内に配置された第1の複数すなわちN個の量子ビットと、第1の複数量子ビットの各量子ビットと交差する第2金属層内に少なくとも部分的に配置された第2の複数すなわちM個の量子ビットと、第1および第2の複数量子ビットからの量子ビットの各対が互いに交差する領域を少なくとも部分的に含む第1の複数すなわちN×M個の結合素子とを含んでいてよい。  (もっと読む)

(もっと読む)

量子ビット状態の読み出しシステム、方法、および装置

【課題】 計算量子ビット状態の読み出しにおけるラッチ量子ビットの利用を提供する。

【解決手段】

超伝導読み出しシステムは、計算量子ビットと、計算量子ビットの状態を測定する測定装置と、計算量子ビットと測定装置との間の導電結合を仲介するラッチ量子ビットとを含む。ラッチ量子ビットは、互いに直列結合された少なくとも2つの超伝導インダクタンスコイルを含む量子ビットループと、複合ジョセフソン接合内で互いに直列結合された、および量子ビットループに関して互いに並列に結合された少なくとも2つのジョセフソン接合を含む量子ビットループを遮断する複合ジョセフソン接合と、クロック信号を複合ジョセフソン接合に結合する第1のクロック信号入力構造とを含む。

(もっと読む)

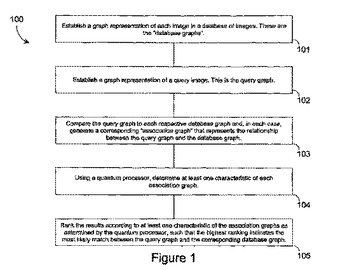

自動画像認識用のシステム、方法、および装置

連合グラフおよび量子プロセッサの実装により自動画像認識の精度および計算時間を向上させる方法。  (もっと読む)

(もっと読む)

汎用断熱量子コンピュータの物理的実現

デバイス、方法、および物品が量子ビット間で好適な通信を可能にして汎用断熱量子計算のアーキテクチャを提供する。このアーキテクチャは、第1の結合された基底A1B1と、第1の基底A1B1と交換しない第2の結合された基底A2B2を含む。  (もっと読む)

(もっと読む)

1 - 10 / 16

[ Back to top ]