精材科技股▲ふん▼有限公司により出願された特許

1 - 7 / 7

ロードボード及びその製造方法

【課題】ロードボード及びその製造方法を提供する。

【解決手段】第1の表面、第2の表面、及び第1の表面と第2の表面とを連通する少なくとも1つの貫通孔を有する半導体基板を用意する工程と、第1の表面、第2の表面及び貫通孔の内壁に電気めっき高分子層を電気めっきする工程と、電気めっき高分子層に、第1の表面から貫通孔の内壁を経由して第2の表面まで延在した回路層を形成する工程とを備える。さらに、ロードボードの絶縁層、即ち電気めっき高分子層を電気めっきにより形成するため、製造コストを効果的に低減することができる。

(もっと読む)

チップパッケージとその製造方法

【課題】チップパッケージとその製造方法を提供する。

【解決手段】本発明の実施例は、チップパッケージの製造方法を提供する。複数のスクライブラインにより隔てられる複数のデバイス領域を有する半導体ウェハを提供する工程と、パッケージ基板を半導体ウェハに接合し、スペーサ層をパッケージ基板と半導体ウェハの間に設置して、スペーサ層は、それぞれデバイス領域を露出する複数のキャビティを区画し、半導体ウェハの外縁に隣接する複数の貫通孔を有する工程と、貫通孔中に、接着材料を充填し、スペーサ層は粘性を有し、材料は接着材料と異なる工程と、スクライブラインに沿って半導体ウェハ、パッケージ基板とスペーサ層をダイスして、互いに分離した複数のチップパッケージを形成する工程と、を含む。

(もっと読む)

インターポーザ及びその形成方法

【課題】異なる構造や特性を持つ電子要素の要求に合致する新規なインターポーザとその形成方法を提供する。

【解決手段】インターポーザは、第1面及び第2面を有する基板と、第1面から第2面に延出する第1ホールと、第1面から第2面に延出し、幅が第1ホールと異なる第2ホールと、基板上に位置し、第1ホールの側壁と第2ホールの側壁上に延出する絶縁層と、基板上の絶縁層に位置し、第1ホールの側壁上に延出する導電層と、を含み、第2ホール中には導電層を持たない。

(もっと読む)

チップパッケージ及びその形成方法

【課題】 チップパッケージの信頼性及び構造安定性を提供する。

【解決手段】 第1表面と第2表面を有する基板、前記基板の前記第1表面上に位置された導電パッド構造、前記基板の前記第1表面と前記導電パッド構造上に位置され、前記導電パッド構造の一部を露出する開口を有する誘電体層、及び前記誘電体層上に位置され、前記開口内に充填されるキャップ層を含むチップパッケージ。

(もっと読む)

チップパッケージおよびその製造方法

本発明は、デバイス領域を有する半導体基板と、前記半導体基板上に配置されたパッケージ層と、前記半導体基板と前記パッケージ層との間に配置され、前記デバイス領域を囲む間隔層と、前記間隔層内に形成された中空パターン、前記間隔層と前記デバイス領域との間に配置された実体パターン、または、それらの組み合わせを含む補助パターンと、を含むチップパッケージである。  (もっと読む)

(もっと読む)

電子装置とその製造方法

【課題】

電子装置とその製造方法を提供する。

【解決手段】

電子装置は、ガラス基板と、少なくとも一つの開口を有し、ガラス基板上に設置されるパターン化半導体基板と、第一導電層と第二導電層を有し、第一導電層が、パターン化半導体基板とガラス基板間に設置される少なくとも一つの受動素子と、からなる。

(もっと読む)

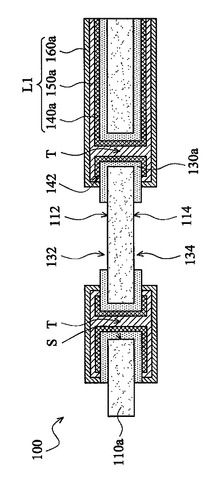

電子デバイスパッケージ及びその製造方法

【課題】従来技術よりも簡略化した電子デバイスパッケージ及びその製造方法を提供する。

【解決手段】半導体チップは第1基板100を有する。支持ブリック101aは第1基板と既定距離が隔てられている。接合パッド104は第1基板から支持ブリックにわたる表面を有する。第1基板は、第1表面と第1表面と向かい合う第2表面とを有する。感光素子102は、第1基板の第1表面上に形成される。第2基板112は、第1基板の第2表面と接合され、上パッケージ層120と下パッケージ層130とは、第1基板の第1表面と第2基板とをそれぞれ覆う。導電体配線層136は、下パッケージ層の下に形成されている。さらに導電体配線層は、接合パッドと支持ブリックの側面上まで延設されている。導電体配線層は、接合パッドに電気的に接続されている。また、導電体バンプ140は、下パッケージ層の下に形成されており、導電体配線層に電気的に接続されている。

(もっと読む)

1 - 7 / 7

[ Back to top ]