サイクロス セミコンダクター, インコーポレイテッドにより出願された特許

1 - 5 / 5

共振クロックネットワークを従来モードで作動させるためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。提示されたアーキテクチャにより、共振クロック分配ネットワークの従来モードでのエネルギ効率の良い作動が可能になり、クロック波形の目標仕様を満たすことができる。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、アットスピード試験及び達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

インダクタオーバーヘッドなしで共振クロック分配ネットワークの固有周波数を選択する方法

共振クロック分配ネットワークのためのインダクタアーキテクチャが提示される。このアーキテクチャにより、選択的にインダクタを切り離すことによって共振クロック分配ネットワークの固有周波数の調整が可能になり、複数のクロック周波数でエネルギ効率の良い作動が実現する。提示されたアーキテクチャは、主として統合されたインダクタを備える共振クロックネットワーク設計を対象としており、面積オーバヘッドが現れない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

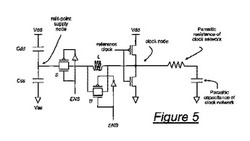

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

マルチクロックネットワークを備えたデジタルデバイス用共振クロックおよびインターコネクトアーキテクチャ

バッファなしでクロックおよびデータ信号を分配する共振ドライバを使ったクロック、データ分配ネットワークが提案されており、低ジッター、低スキュー、低エネルギー消費、そして緩いタイミング要求が実現される。このようなネットワークは、概してFPGAのようなPLD用アーキテクチャに適用可能であり、同様に、マイクロプロセッサ、ASIC、SOCなど、複数のクロックネットワークとクロック周波数、ハイパフォーマンスおよび低電力クロッキング仕様をもつ他の半導体デバイスにも適用可能である。  (もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]