アクテル・コーポレイシヨンにより出願された特許

1 - 10 / 14

高速フラッシュメモリデバイスのアドレス遷移検出器

アドレス遷移検出回路は、入力ノードと、出力ノードと、バンドギャップリファレンスと、バンドギャップリファレンスノードとから得られる電圧を有するPbias及びNbiasノードを備えている。カスケード接続された第1乃至第5インバータは、Pbiasノード及びNbiasノードとそれぞれ接続されたゲートを有するpチャネル及びnチャネルMOSトランジスタによって、それぞれ電源供給される。第1インバータの入力は、入力ノードに接続されている。第1及び第2キャパシタは、カスケード接続された第1及び第4インバータの出力からグランドにそれぞれ接続されている。NANDゲートは、入力ノードに接続された第1入力と、カスケード接続された第5インバータの出力に接続された第2入力と、出力ノードに接続された出力とを備えている。  (もっと読む)

(もっと読む)

ビットライン・プリセット回路及びフラッシュメモリ検知手段のための方法

フラッシュメモリアレイは、基準電流が流れる基準ビットラインを具備する。読み出し処理中、読み出しに選択されたビットラインは、電流−電圧変換器と結合する。前記の各電流−電圧変換器は、ビットラインを流れる入力電流を基に出力電圧を生成する。電流−電圧変換器の出力電圧は、基準電流−電圧変換器の出力から得られる基準電圧と比較される。基準電流−電圧変換器の入力は、基準ビットライン上の基準電流よって得られる。基準電流より大きな電流を流すセルはいずれも消去セルとしてみなされる。逆に、基準電流より小さい電流を流すセルはいずれも、プログラムセルとしてみなされる。  (もっと読む)

(もっと読む)

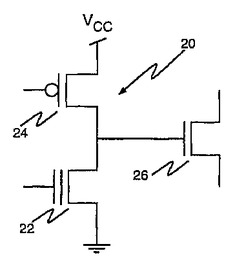

プログラマブルロジックアレイ用不揮発性プログラマブルメモリセル

プログラマブルロジックアレイに用いるために適した不揮発性プログラマブルメモリセルは、第2導電型の揮発性MOSトランジスタ24と直列に、第1導電型の不揮発性MOSトランジスタ22を具備する。不揮発性MOSトランジスタ22は、フラッシュトランジスタのようなフローティングゲートトランジスタであるか、又はフローティング電荷トラッピングSONOS、MONOSトランジスタ、若しくはナノ結晶トランジスタのような別のタイプの不揮発性トランジスタであってもよい。揮発性MOSトランジスタ、インバータ、又はバッファ26は、そのゲート又は入力を、不揮発性MOSトランジスタ22と揮発性MOSトランジスタ24との間のコモン接続点に接続することによって駆動される。  (もっと読む)

(もっと読む)

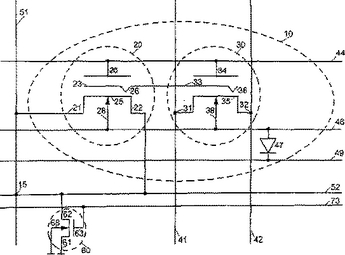

不揮発性、2トランジスタのプログラマブル論理セルおよびアレイのレイアウト

2トランジスタ不揮発性メモリセルが半導体本体内で形成される。メモリトランジスタウェルが、その半導体本体内に配置される。スイッチトランジスタウェルが、その半導体本体内に配置され、メモリトランジスタウェルから電気的に分離される。離隔されたソース領域およびドレイン領域を含むメモリトランジスタが、メモリトランジスタウェル内で形成される。離隔されたソース領域およびドレイン領域を含むスイッチトランジスタが、スイッチトランジスタウェル領域内で形成される。フローティングゲートは、メモリトランジスタおよびスイッチトランジスタのソース領域およびドレイン領域から絶縁され、それらと自己整合する。制御ゲートは、フローティングゲートの上方に配置され、フローティングゲートに対して位置合わせされ、またメモリトランジスタおよびスイッチトランジスタのソース領域およびドレイン領域と位置合わせされる。  (もっと読む)

(もっと読む)

放射線に耐性のある、スタティックRAMのフィールドプログラマブルゲートアレイにおける誤りの検出と訂正の方法及び装置

本システムは、論理モジュールと、論理モジュールと共に結合された配線資源を持った、放射線に耐性のあるプログラマブル論理素子を備える。構成データを提供する構成データラインは、論理モジュールと配線資源とを制御する。構成データラインに結合される誤り訂正回路は、単一事象の異常(SEU)によって起こり得る構成データ内の誤りを分析して訂正する。本システムは、また、プログラマブル論理素子をプログラムするための構成データを持ったプログラマブル論理素子内の誤りを訂正する方法を備える。本方法は、構成データのバックグラウンド読み取り段階を備える。次に、構成データは、誤りに対して分析される。最後に構成データは、訂正されて、もし誤りが見付かれば、構成データは書き換えられる。  (もっと読む)

(もっと読む)

正電圧および負電圧の両方を対象とする入出力パッドのためのESD保護構造

本発明に係るESD保護回路がトリプル・ウェル・プロセスの内部p−ウェルの中に形成され、さらに正電圧および負電圧の両方を印加され得る入出力パッドに接続されたn−チャンネルMOSトランジスタのために開示されている。第1スイッチは、入出力パッドにおける電位が正であるとき、n−チャンネルMOSトランジスタを有するp−ウェルをグランドに接続する。第2スイッチは、入出力パッドにおける電位が負であるとき、n−チャンネルMOSトランジスタを有するp−ウェルを入出力パッドに接続する。第3スイッチは、前記n−チャンネルMOSトランジスタがターンオフされているとき、前記n−チャンネルMOSトランジスタのゲートを前記p−ウェルに接続する。第4スイッチは、前記n−チャンネルMOSトランジスタがターンオンされているとき、前記n−チャンネルMOSトランジスタのゲートをVccに接続する。  (もっと読む)

(もっと読む)

FPGAにおける揮発性メモリベースのプログラマブル回路のための不揮発性メモリ構成方式

不揮発性メモリ構成方式は、FPGAファブリックと、FPGAファブリック外部の複数の第1構成変更可能回路素子と、FPGAファブリック外部の複数の第2構成変更可能回路素子とを具備するプログラマブル集積回路中の、揮発性メモリベースのプログラマブル回路のために開示される。複数の分散構成不揮発性メモリセルは、FPGA中に配置される。前記各分散構成不揮発性メモリセルは、複数の第1構成変更可能回路素子のうちの異なる1つと接続されている。不揮発性メモリアレイは、第2構成変更可能回路素子のための構成情報を格納する。複数のレジスタセルには、第2構成変更可能回路素子が配置され、かつ不揮発性メモリアレイと接続可能である。前記各レジスタセルは、複数の第2構成変更可能回路素子のうちの異なる1つと接続されている。  (もっと読む)

(もっと読む)

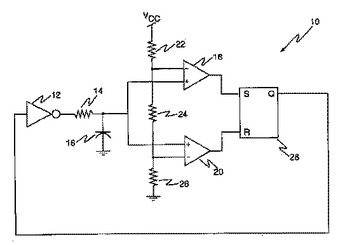

電圧補償及び温度補償されたRC発振回路

入力及び出力を有するインバータを具備する、温度補償された集積RC発振回路。RC網は、前記インバータと、比較器の対との間に接続されている。第1比較器は、第1基準電圧に接続された反転入力と、前記RC網に接続された非反転入力と、出力とを具備する。第2比較気は、前記RC網に接続された反転入力と、第2談笑電圧に接続された非反転入力と、出力とを具備する。セット・リセット・フリップフロップは、前記第1比較器の出力に接続されているセット入力と、前記第2比較器の出力に接続されているリセット入力と、前記インバータの入力に接続されている出力とを具備する。前記比較器の差動増幅器は、各々ミラー接続されたpチャネルMOSトランジスタを制御する、ダイオード接続されたpチャネルMOSトランジスタを具備し、前記pチャネルMOSトランジスタのチャネル幅は、前記ダイオード接続されたpチャネルカレントミラートランジスタの幅より狭い。  (もっと読む)

(もっと読む)

フィールドプログラマブルゲートアレイを構成するためのプログラム可能な相互接続セル

本発明は、制御ゲート電位のノードと、ドレイン、ソース、フローティングゲート、前記制御ゲート電位のノードに接続された制御ゲートを有する第1のフローティングゲートフラッシュメモリトランジスタと、第1のプログラム可能なノードに接続されると共に、第2のプログラム可能なノードに接続されたドレイン、第1のフローティングゲートフラッシュメモリトランジスタのフローティングゲートに接続されたフローティングゲート、制御ゲート電位のノードに接続された制御ゲートを有する第2のフローティングゲートフラッシュメモリトランジスタとを有するプログラム可能な相互接続セル切り替え回路構造を備え、それによって、第1のフローティングゲートフラッシュメモリトランジスタのソースまたはドレインが、プログラム動作の間、セルの外でアースに接続されることを必要とする。  (もっと読む)

(もっと読む)

対面ボンディングされるI/O回路ダイ及び機能論理回路システム

第1のセットの集積回路ダイであって、そのセットのそれぞれの構成要素が、種々の形状でかつ該ダイ上に配置された入/出力回路を有する第1のセットの集積回路ダイと、第2のセットの集積回路ダイであって、それぞれが、該ダイ上に配置された種々の論理機能回路を有する第2のセットの集積回路ダイと、を含むことを特徴とする集積回路システム。集積回路ダイの第1および第2のセットのそれぞれの構成要素は、該ダイ上に配置されかつ他のセットのそれぞれの構成要素の一連の対面ボンディングパッドと結合される、一連の対面ボンディングパッドを含む。  (もっと読む)

(もっと読む)

1 - 10 / 14

[ Back to top ]