イノテック株式会社により出願された特許

1 - 10 / 10

半導体集積回路

本半導体集積回路は、複数個のメモリブロック(11)から構成されている。各メモリブロック(11)は、四辺(12a〜12d)で囲まれ、各辺(12a〜12d)毎にアドレス入力端子(A0〜A11)およびデータ入出力端子(D0〜D11)が設けられている。隣接する2つのメモリブロック(11)を第1および第2のメモリブロック(11)とすると、第1のメモリブロック(11)の辺(12a)に設けられたアドレス入力端子(A0〜A2)が、第2のメモリブロック(11)の対向する辺のデータ入出力端子(D8〜D6)にそれぞれ接続されている。第1のメモリブロック(11)の辺(12a)に設けられたデータ入出力端子(D0〜D2)は、第2のメモリブロック(11)の対向する辺のアドレス入力端子(A8〜A6)にそれぞれ接続されている。各メモリブロック(11)は、フレキシブルな可変論理セルを構成する。これらの可変論理セルによって所望の論理回路が形成される。  (もっと読む)

(もっと読む)

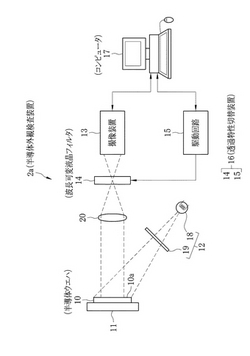

半導体外観検査装置

【課題】 半導体ウエハあるいはペレット上の欠陥を高速で確実に検出することができる半導体外観検査装置を提供する。

【解決手段】 半導体外観検査装置2aは、検査対象面10aで反射した反射光から、少なくともその半値幅が100nm波長帯域の1/2以下からなる狭帯域幅のピークを有する透過光を生成するとともに、100nm波長帯域内において、透過光を複数の波長で選択的に出力させるようにした透過特性切替装置16を備える。透過特性切替装置16は、その実効光路長が設定中心透過波長の整数倍からなるように厚みが設定された液晶デバイスを少なくとも1つ有する複数の平行ニコル液晶セルおよび垂直ニコル液晶セルを組み合わせてなる波長可変液晶フィルタ14と、各液晶セルに複数の電位を多段に切り替えて印加する駆動回路15とから構成される。

(もっと読む)

半導体集積回路のテスト装置および方法

【課題】 より実用的且つ汎用性の高い半導体集積回路のテスト装置および方法を提供する。

【解決手段】 半導体集積回路のテスト装置2は、HC18から送信されるテストプログラムを、テスト条件設定データとテスト回路構築データとに分けて、DRAM22とフラッシュメモリ23とにそれぞれ記憶し、テスト回路構築データに基づいて、FPGA13に所望のテスト回路19を構築し、テスト条件設定データに基づいて、検査波形信号生成回路30により検査波形信号を生成してこれをDUT20に出力し、検査波形信号に対してDUT20で出力される出力波形信号と理論値とを比較回路31で比較してDUT20の動作の良否を判定し、判定結果をHC18に送信する。

(もっと読む)

半導体記憶装置

【課題】 セクタ単位での消去を可能とした半導体記憶装置を提供する。

【解決手段】 セルアレイ2内のワード線を8本ごとに区分し、各ブロックに消去セクタES0〜ES15を構成する。シリコン基板に所定の負電圧を印加した状態で、消去対象の消去セクタに属する8本のワード線に所定の正電圧を印加するとともに、その他の消去対象外の消去セクタに属するワード線を接地することにより、消去対象の消去セクタに属するメモリセルには消去動作を行わせ、消去対象外の消去セクタに属するメモリセルには消去動作を行わせない。これにより上記消去セクタ単位でのセクタ消去が実現される。セルアレイ2内にはメモリセルが2次元マトリクス状に配列されている。メモリセルは、1対のフローティングゲートを有し、2ビット以上のデータを書き替え自在に保持することができる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 製造が容易であり、かつ動作の信頼性が高い半導体記憶装置を提供する。

【解決手段】 セルトランジスタ11は、p型シリコン基板、コントロールゲートCG、及び電気的に孤立した一対のフローティングゲートFG1,FG2からなる。シリコン基板には、コラム方向に延在した帯状の凸部13が形成されており、ソース又はドレインとして機能する一対の帯状のn型拡散領域14a,14bが凸部13を挟む表層に形成されている。コントロールゲートCGは、凸部13及びフローティングゲートFG1,FG2の上に絶縁膜を介して形成され、帯状にロウ方向に延在している。コラム方向に関するフローティングゲートFG1,FG2の幅W1はコントロールゲートCGの幅W2より大きい。フローティングゲートFG1,FG2及びコントロールゲートCGは、技術的課題のあるコラム方向におけるセルフアラインプロセスを用いずに簡単に形成することができる。

(もっと読む)

固体撮像装置

【課題】 光照射の少ない暗部における固定パターンノイズの発生を抑制する。

【解決手段】 信号出力回路43は、ピクセルが光照射された場合にソース領域に生成されて第1ラインメモリ50に記憶される電位VS1と、ピクセルが初期化された場合にソース領域に生成されて第2ラインメモリ52に記憶される電位VS2との差に応じた映像信号を出力する。電位VS1,VS2は、水平走査手段によって第1及び第2水平信号線52,53に伝達され差動アンプ54に入力される。差動アンプ54からなる演算増幅手段は、水平出力線57,58に映像信号を出力した後、第1及び第2水平信号線52,53の電位をともに等しくするとともに、該電位を該出力時までに第1及び第2水平信号線52,53に伝達された電位VS1,VS2に応じて決定される電位とする。

(もっと読む)

データ読出し回路

【課題】 データ読出し速度を高速化する。

【解決手段】 差動比較器7の反転入力端子には、Yセレクタ4によって選択されるメモリセルのソースが配線31aを介して接続されており、非反転入力端子には、基準セル32のソースが配線31bを介して接続されている。配線31a,31bには、ゲートバイアス電圧Vcgsがゲートに印加されたnMOSトランジスタ34a,34bが接続され、ソースフォロア回路が構成されている。ラッチ回路33は、差動比較器7の出力端子に接続されており、差動比較器7による電位Vc,Vrの比較結果をラッチする。ゲートがバイアスされたnMOSトランジスタ34a,34bは電流源となり、差動比較器7の各入力端子に生じる寄生容量C1,C2が早期に充電され、電位Vc,Vrが短時間で飽和するので、データ読出し速度が高速化する。

(もっと読む)

技術評価システムおよび方法

【課題】設計技術自体を評価することができるシステムおよび方法を提供する。

【解決手段】設計用ソフトウエアを用いて設計を行なうユーザの、設計用ソフトウエアを用いた設計の技術レベルを評価する設計技術評価システム10において、評価用の問題であるテスト用設計データをデータファイル20aに記憶し、テスト用設計データに基づいて設計用ソフトウエアを用いて設計を行なって得られる設計結果を評価するための評価基準を評価ファイル20bに記憶し、クライアントマシーン16に設計用ソフトウエアを格納し、設計用ソフトウエアを用いてユーザがテスト用設計データに基づいて設計を行ない、社内評価システムサーバ18は、クライアントマシーン16を用いてユーザが行なった設計結果を、評価基準に従って評価して、ユーザの技術レベルの評価結果を生成する。

(もっと読む)

冷却システム

冷却システム

【課題】 エネルギー消費量を少なくすることができ、しかも、エネルギーロスの少ない冷却システムを提供すること。

【解決手段】 負荷Hと、この負荷を冷媒によって冷却する冷却回路Aと、この冷却回路Aの冷媒の熱を外部に放熱する放熱機構5と、冷却回路Aに合流バルブ13を介して接続した冷媒タンク8と、冷媒タンク8内の冷媒を所定温度に保つ冷却装置11と、合流バルブ13の開度を制御するコントローラ12と、冷却回路Aの冷媒の温度を検出する温度センサー14とを備え、コントローラ12は、温度センサー14によって検出された冷却回路A内の冷媒の温度が、所定の温度よりも高いときに、合流バルブ13を開いて、冷媒タンク8内の冷媒を冷却回路Aに合流させる一方、冷却装置11は、冷媒タンク8内の冷媒の温度が、所定の範囲内に保たれているときに、その作動を停止する。

(もっと読む)

1 - 10 / 10

[ Back to top ]