山梨日本電気株式会社により出願された特許

1 - 9 / 9

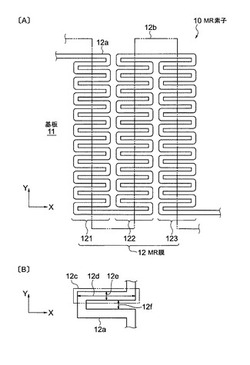

磁気抵抗効果素子及びこれを用いた磁気センサ

【課題】MR素子の消費電力を低減する。

【解決手段】MR素子10は、基板11と、基板11上に設けられたMR膜12とを備えている。MR膜12は、ジグザグ状に折れ曲がる直線12aが更に多重にジグザグ状に折れ曲がる形状12bを有する。直線12aは、複数の形状部121,122,123を形成している。それぞれの形状部121,122,123は、互いに平行な複数の長方形12cがジグザグ状に直列に接続された形状を有し、かつジグザグ状に互いに直列に接続されている。

(もっと読む)

磁気センサ及びその製造方法

【課題】センサ寸法の拡大が抑制され小型化に有利で、高いセンサ特性が安定して得られ、作製工程が複雑化しない、磁気センサを提供する。

【解決手段】抵抗素子を直列に接続した通電経路単位41,42,43,44のそれぞれに関し、一方端部は電源端子Vccに電気的に接続され、他方端部は接地端子GNDに電気的に接続され、抵抗素子同士の接続部は出力端子Vo1〜Vo4に電気的に接続される。通電経路単位のそれぞれを構成する複数の抵抗素子の少なくとも1つは、磁気抵抗効果膜からなる磁気抵抗効果素子であり、電源端子は全ての通電経路単位につき共通化され、接地端子は全ての通電経路単位につき共通化される。全ての通電経路単位は絶縁膜の一方の面に接して形成され、絶縁膜の他方の面に接して配置された導電膜を用いて、電源端子共通化のための電源接続配線及び接地端子共通化のための接地接続配線が形成される。

(もっと読む)

磁気センサ、磁気センサの駆動方法およびコンピュータプログラム

【課題】磁電変換素子の消費電力を抑制する。

【解決手段】外部間欠電源からの間欠電源信号の電源オン時間より短いパルス幅のパルスを発生するパルス発生回路と、磁電変換素子と、パルスに基づいて磁電変換素子への間欠電源信号の電源オン時間内の信号印加時間を制御するスイッチと、を有する。磁電変換素子は、例えば、外部の磁界の有無により信号レベルの大小関係の異なる2つの検知信号を出力するMR素子である。2つの検知信号を増幅するアンプと、増幅された2つの検出信号を比較するコンパレータと、を設けることができる。

(もっと読む)

プリント配線板及びその製造方法

【課題】表面実装用のパッドの間隔を狭くすることが可能であるとともに、FPCを実装する場合でも電子部品と同時にリフロー法によって実装可能な構造のプリント配線板及びその製造方法を提供する。

【解決手段】パッド2を露出させるようにソルダレジスト3が表面に形成され、隣接するパッド同士の間には、ソルダレジスト4が形成され、ソルダレジスト3とソルダレジスト4によって他のパッド2と隔てられたパッド2には、ソルダレジスト4と略同一高さ以上のはんだペーストが印刷によって配置されている。

(もっと読む)

プリント配線板及びこれとフレキシブルプリント基板とのはんだ接続構造並びに方法

【課題】はんだ接合に際してPCBとFPCとの位置決めを容易に行えるプリント配線板及びこれとフレキシブルプリント基板とのはんだ接続構造並びに方法を提供する。

【解決手段】フレキシブルプリント基板実装用の複数のパッド2を備えたプリント配線板1であって、パッド2を露出させるように表面にソルダレジスト3が形成され、各パッド2の周囲には、絶縁印刷層4によって凸部が構成されている。

(もっと読む)

光モジュール及びその製造方法

【課題】光結合素子端面と光導波路結合端面の間隔の精度を向上させ、光素子と光導波路とを高効率で結合した光モジュール及びその製造方法を提供する。

【解決手段】基板1上に形成された下部クラッド層2、コア層3及び上部クラッド層4の光導波路形成層からなる光導波路5と、光導波路形成層の一部分を除去して形成した光素子搭載部とを有し、露出した光導波路5の端面と光素子搭載部に搭載された光素子8とを光学的に結合させた光モジュールであって、光導波路5の端面には、光導波路5から離れた位置に上部クラッド層4の最上部以上の高さで形成した少なくとも一つの突き当て用突起部18を有し、突き当て用突起部18と光素子8の光導波路5側の端面とを接触させた状態から、光素子8をその光軸方向に所定距離移動させて光素子8を光素子搭載部に固定した。

(もっと読む)

光導波路デバイス及びその製造方法

【課題】 高温の熱処理が必要な場合でも、高精度な台座ブロックを作製する。

【解決手段】 光導波路デバイス10は、シリコン基板11上に形成された下部クラッド層12、コア層13及び上部クラッド層141,142を有する光導波路形成層15から成る光導波路部16と、光導波路形成層15の一部が除去されて成る光素子搭載部17とを有し、光導波路形成層15の一部の除去によって露出した光導波路部16の端面に光素子搭載部17に搭載された発光素子18が光学的に結合されるものである。マスク22となるクロム膜21は、上部クラッド層142上に設けられる。そのため、クロム膜21を形成する前に、下部クラッド層12及びコア層13などに高温の熱処理を施しても、クロム膜21には何ら影響を与えない。

(もっと読む)

磁気センサ、その製造方法および電子機器

【課題】検知する磁界が2点以上ある磁気センサに用いることが可能な、低磁界側から高磁界側まで広い領域で磁気抵抗が変化し、膜応力の影響が小さく、かつ工程上の制限の少ない合金金属薄膜を使用する磁気センサ、その製造方法および磁気センサを使用した電子機器を得ること。

【解決手段】各種電子機器に適用する磁気センサに用いる合金金属薄膜の組成比が、Niの組成比をx重量%、Coの組成比をy重量%とすると、21x+19y≦1869、5x+28y≧546、y≦11、x+y≧85を同時に満たす組成範囲内にある。もしくは、この合金金属薄膜の磁歪定数の絶対値が1.5×10-5以下であり、かつ異方性磁界(Hk)が8Oe以上16Oe以下であり、かつ磁気抵抗変化率が2.5%以上である。

(もっと読む)

磁気センサ、その製造方法、回転検出装置及び位置検出装置

【課題】異方性磁気抵抗素子をIC基板上に薄膜形成した磁気センサにおいて、垂直方向と水平方向の印加磁界を検出でき、磁界の印加方向に対する検出感度の調整が可能であり、かつ、印加方向とは異なる他方向から磁界が印加された条件下での感磁界特性への影響を抑制できる1チップ構成の磁気センサ等を提供する。

【解決手段】

磁気センサは、基板上に磁気抵抗素子11〜14を薄膜形成し比較増幅機能を有する電気回路を備えた半導体基板67と、半導体基板67を実装するリードフレーム60と、半導体基板67と接続されるリードフレーム61及び62とをパッケージ66内に収容する。リードフレーム60は、屈曲加工により半導体取付面がパッケージ表面に対して傾斜のある構造を有し、半導体基板67は該取付面に取り付けられる。

(もっと読む)

1 - 9 / 9

[ Back to top ]