Fターム[2G132AL38]の内容

Fターム[2G132AL38]に分類される特許

1 - 20 / 78

半導体試験装置、電気長測定方法

【課題】測定経路端を接地して電気長を測定する場合に、経路に断線があっても測定結果を得られるようにする。

【解決手段】測定経路端を接地して電気長を測定する半導体試験装置であって、測定経路に測定信号を出力する信号発生手段と、測定経路から分岐して入力される入力信号と、任意の閾値電圧とを比較する比較手段と、信号発生手段に測定信号を出力させ、比較手段の入力信号が第1閾値電圧以上となってから第2閾値電圧以下となるまでの時間を計測し、所定時間内に計測された場合には、計測された時間に基づいて測定経路の電気長を算出し、所定時間内に計測されなかった場合には、比較手段の入力信号が第1閾値電圧以上となってから、第1閾値電圧よりも高い第3閾値電圧以上となるまでの時間を計測して、測定経路の異常箇所までの電気長を算出する電気長測定制御手段とを備える。

(もっと読む)

複数個の各テスト回路を対象とする誤動作検出装置及び当該装置を使用した誤動作検出方法

【課題】ノイズの放電時期を適宜選択しながら、効率的に実現し得るような装置及び検査方法を提供すること。

【解決手段】直流電源1と複数個の各テスト回路5との間を、充電用抵抗素子(R1)、放電用抵抗素子(R2)、キャパシタンス(C)を備えているノイズ放電回路2を設け、当該ノイズ放電回路2と各テスト回路5との間に介在しているプローブ4が、複数個の各テスト回路5を選択しかつ接続可能とする一方、前記各テスト回路5に対し選択回路8を介して接続されている同期遅延コントローラー回路6が、印加コントローラー回路7を介してノイズ放電の時期を調整することができるテスト回路5の誤動作試験装置及び当該装置を使用している誤動作検出方法。

(もっと読む)

タイミング信号生成装置及び半導体試験装置

【課題】エッジ信号の発生エラーの原因を短時間且つ容易に解析することができるタイミング信号生成装置、及び当該装置を備える半導体試験装置を提供する。

【解決手段】タイミング信号生成装置1は、生成すべきタイミング信号TSのエッジの位置を規定するエッジ信号EG1,EG2を規定する複数のタイミングデータを記憶する記憶部11と、生成すべきタイミング信号TSに応じて記憶部11から読み出されたタイミングデータの入れ替えを行う入替部12と、入替部12から出力されるタイミングデータに基づいてエッジ信号EG1,EG2を生成するエッジ信号生成部15と、エッジ信号生成部15で生成されるエッジ信号EG1,EG2の発生エラーを検出する検出部16と、検出部16の検出結果を入替部12の入れ替え規則に応じて変換する変換部18とを備える。

(もっと読む)

半導体試験装置、半導体試験装置の診断プログラムおよび半導体試験装置の診断方法

【課題】半導体試験装置に備えられるユニットの診断を行って、交換するユニットを推定することで、試験時間の短縮化を図ることを目的とする。

【解決手段】本発明の半導体試験装置1は、DUTの試験を行う半導体試験装置1であって、交換可能な複数のFRUのそれぞれに対応して設けられ、FRUに故障を生じているか否かの故障診断を行う診断部11、21と、診断部11、21が行う故障診断について、当該故障診断に対応して故障の原因となるFRUの可能性の統計である故障統計情報を記憶するカバレッジデータベース31と、診断部11、21がFRUに故障を生じていると診断したときに、この診断を行ったFRUに対応する故障統計情報の値を各FRUのそれぞれについて合算して生成した診断データを生成する診断データ生成部24と、診断データを値の順番に並び替える並び替え部26と、を備えている。

(もっと読む)

半導体試験装置およびリレーのオフ容量異常検出方法

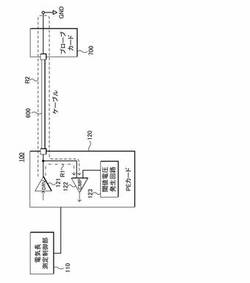

【課題】半導体試験装置に設けられるリレーのオフ容量に異常を生じているか否かを検出することを目的とする。

【解決手段】本発明の半導体試験装置は、DUT2の試験を行うためのドライバ回路10、コンパレータ回路11を設けた試験部1を備える半導体試験装置であって、試験部1に設けられる複数のリレーのうち検査対象のリレーをオフにして電圧または電流を出力してリレーからの電圧を検出し、検出した電圧の時間的な変化に基づいて、リレーのオフ容量に異常を生じているか否かを検出する異常検出部36を備えている。これにより、ドライバ回路10やコンパレータ回路11の動作タイミングを校正する前に、リレーのオフ容量に異常を生じているか否かの検出を行うことができるようになる。

(もっと読む)

試験装置及び診断方法

【課題】複数の入出力ピンを一度の診断で診断するための試験装置及び試験方法を提供する。

【解決手段】被試験デバイスと信号を受け渡す複数の入出力部と、複数の入出力部におけるそれぞれの入出力部の動作を診断する場合に被試験デバイスに代えて複数の入出力部に接続され、それぞれの入出力部の出力値を入出力部と対応付けて記憶する診断用メモリと、それぞれの入出力部に、診断用メモリから対応する出力値を読み出させ、それぞれの入出力部が読み出した出力値に基づいて、それぞれの出力値に対応する入出力部を診断する診断部とを備える被試験デバイスを試験する試験装置。

(もっと読む)

システム診断装置、システム診断方法

【課題】診断内容の最適化と診断実行時間の短縮を図ることができるシステム診断装置を提供する。

【解決手段】システムの構成が変更された場合にシステムが正常に動作するかを診断するシステム診断装置であって、システムを構成するハードウェア、またはシステムを構成するハードウェアに対して診断を行うときに用いられる診断プログラムのうちで、前回の診断から変更されたハードウェアの識別情報、または診断プログラムの識別情報を抽出するシステム情報処理部12と、ハードウェアの識別情報が抽出された場合、ハードウェアの識別情報に対応する診断プログラムを実行する一方、診断プログラムの識別情報が抽出された場合、診断プログラムに対応するハードウェアに対し、診断プログラムを実行する診断実行部11と、を有するシステム診断装置を提供する。

(もっと読む)

半導体試験装置

【課題】安価な回路構成で診断に要する時間を短縮することが可能な半導体試験装置を実現する。

【解決手段】複数のピンを有し、第1のピンのドライバから出力された出力信号と比較電圧とを第1のピンのコンパレータで比較して診断を行う半導体試験装置において、第1のピンとは異なる第2のピンに設けられ、複数のピンそれぞれのコンパレータの出力から1つを選択して出力する信号選択部と、第2のピンに設けられ、信号選択部の出力と期待値パターンとが一致しているか否かを判定する判定部と、第1のピンのコンパレータの出力を第2のピンの信号選択部に選択させ、第2のピンの信号選択部の出力と第2のピンの期待値パターンとが一致しているか否かを第2のピンの判定部で判定させる制御部とを備える。

(もっと読む)

検査装置の操作方法及び検査装置の操作プログラム

【課題】複数のステージを有する検査装置の検査効率を格段に高めることができる検査装置の操作方法を提供する。

【解決手段】本発明の検査装置の操作方法は、複数のモニター14それぞれの操作画面に表示される操作ボタンを用いて複数の検査用のステージ17を備えた検査装置10において、検査装置10の各種の機能を実行するために必要なデータをまとめた排他条件データDと、排他条件データDの排他条件を、各機能を実行するための操作ボタンを押下できるか否かのデータとしてまとめた排他条件パターンPと、を用いて、操作ボタンを排除するための排他条件ボタンを少なくとも一つのモニター14に設定し、排他条件ボタンを押下して他のモニターでは少なくとも一つのモニターの排他条件に即した画面の表示を禁止する。

(もっと読む)

試験装置およびその診断方法

【課題】試験装置の診断時間を短縮する。

【解決手段】複数のモジュールmod_pinはそれぞれ、その診断結果を示す診断データRDATA_pinをそれと対応する期待値データEXPと比較する期待値比較部20を含み、期待値比較部20による比較結果を示す比較判定データCDATA_pinを出力する。第1論理ゲート10は、複数のモジュールmod_pinそれぞれの比較判定データCDATA_pin_1〜CDATA_pin_nの論理和を生成する。論理和CDATA_mod_topにもとづいて、試験装置100全体が診断される。

(もっと読む)

半導体試験装置

【課題】ALPGが生成したパターンデータに転送エラーが生じたときに、異常が生じた箇所を特定することにより、メンテナンス性を向上させることを目的とする。

【解決手段】DUT1を試験するパターンデータを生成するALPG2とパターンデータをDUT1に印加する複数のPE3とを備える半導体試験装置であって、ALPG2に備えられ、PE3にパターンデータを分配するピンセレクタ21から出力される各パターンデータをそれぞれ記憶するALPG用ログメモリ23と、PE3ごとに備えられ、DUT1に入力されるパターンデータを記憶するPE用ログメモリ12と、ALPG用ログメモリ21に記憶されたパターンデータとPE用ログメモリ12に記憶されたパターンデータとを比較して、ピンセレクタ21とPE3との間に異常が発生しているか否かを検出する異常部位検出部32と、を備えている。

(もっと読む)

診断機能を備える装置、診断方法、およびプログラム

【課題】デバイスの生産性を下げないシステム。

【解決手段】複数の診断箇所の診断機能を備える装置であって、複数の診断箇所のそれぞれの診断不要期間を取得する取得部と、複数の診断箇所のうち、診断不要期間が経過している診断箇所を選択して診断する診断部と、を備える装置を提供する。複数の診断箇所のそれぞれに対応する診断インターバルを記憶する診断インターバル記憶部と、複数の診断箇所のうち診断部が診断した診断箇所の診断不要期間を、当該診断箇所に対応する診断インターバルにより更新する更新部と、を更に備えてもよい。

(もっと読む)

製品試験装置、ロット管理方法およびプログラム

【課題】 製品試験装置の自己診断結果に異常が発見された場合における影響を受ける範囲の特定の容易化。

【解決手段】 製品試験装置は、試験対象の製品に応じて試験条件を設定し、前記試験条件を用いて試験を行った製品のロット情報を前記試験条件と関連付けて記録していく。前記自己診断機能による自己診断結果が出る度に、前記自己診断結果と、前記試験条件とを照合し、前記自己診断結果による影響を受ける試験条件にて試験を行った製品のロット情報を出力する。

(もっと読む)

回路基板検査装置、サーバー、回路基板検査システム

【課題】故障部位を特定することは容易ではない。そのため、回路基板検査装置の修理に要する時間が長くなってしまうという課題がある。

【解決手段】被検査回路基板Sを順次検査し、被検査回路基板Sごとの検査結果を出力する検査部4と、文字や画像を表示するディスプレイ2と、検査結果が異常であることを示すエラー情報としてのエラーコードを検査部4から取得すると、サーバー30にエラーコードを送信するエラー情報送信部10と、サーバー30から送信された検査部4のエラーコードに対応する修理情報としての修理内容を取得する修理情報取得部11と、修理内容をディスプレイ2に表示する修理情報表示部12と、を備えた回路基板検査装置1を提供する。

(もっと読む)

半導体試験装置及びその診断方法

【課題】ユーザに煩雑な作業を強いることなく半導体試験装置のバリエーションを容易に診断することができる半導体試験装置及びその診断方法を提供する。

【解決手段】半導体試験装置1は、テストヘッド10に実装されるカードC1〜Cnの増減により、規模及び機能の少なくとも一方が相違する複数の装置態様(バリエーション)を実現可能であって、カードが実装されるスロット11a〜11nのうち、バリエーション毎に異なるカードが実装されるスロットを含むブロックにおけるカードの種類を示す情報を記憶するメモリ22と、上記のブロックに含まれるスロットに実装されているカードの種類を示す情報を取得してメモリ22にスロットブロックテーブルTBとして記憶するフラグ設定部21aと、メモリ22に記憶されたスロットブロックテーブルTBに基づいて実際のバリエーションを決定するバリエーション決定部21bとを備える。

(もっと読む)

半導体試験装置

【課題】被測定デバイスの電源ピンにバイパスコンデンサとしてどのような容量値のものが接続されたとしても、最低限の位相余裕を確保しつつ応答速度の低下を防止し、テスト時間を短縮することができる電圧印加電流測定機能を備えた半導体試験装置を提供する。

【解決手段】被測定デバイスの電源ピンに所定の電圧を印加して電流を測定する機能を備えた半導体試験装置において、測定開始前に電源ピンに接続されているバイパスコンデンサの容量値を測定し、測定結果に応じて位相補償用の抵抗または容量の値を変えることで最低限の位相余裕が得られるように電源供給部の応答特性を調整するとともに、測定された容量値に応じて電流測定開始タイミングを最適化するようにした。

(もっと読む)

ポゴタワー電気チャネル自己検査式半導体試験システム

【課題】ポゴタワー電気チャネル自己検査式半導体試験システムの提供。

【解決手段】本ポゴタワー電気チャネル自己検査式半導体試験システムは、ショートボードを提供し、その各接点をロードボード上のポゴタワーの各種ポゴピンに電気的に接続し、それぞれ回路を形成させ、さらに自己検査コントローラが異なる検査信号を各電源チャネル、各伝送チャネル、各駆動チャネルに入力し、上述の回路を通し、複数のパラメータ検出ユニットが各電源チャネル、各伝送チャネル、各駆動チャネルが上述の検査信号を受けて発生する応答信号を検出し並びに判断する。これにより本発明はウエハ試験の前に、各電気チャネルの開路或いは短絡状態が正常であるか、或いは漏電が発生しているか否かを自己検査できる。

(もっと読む)

診断装置、診断方法および試験装置

【課題】診断時における使用者の負担を軽減することができる。

【解決手段】被試験デバイスを試験する複数の試験モジュールを備える試験装置を診断する診断装置であって、複数の試験モジュールのそれぞれの種類および接続関係が記述された構成情報を記憶する構成記憶部と、構成情報に基づいて、複数の試験モジュールのそれぞれを診断するための診断用パターンを記述したパターンファイルを生成する生成部と、複数の試験モジュールのそれぞれに対して、対応する診断用パターンに応じた診断用信号を発生させて、それぞれの試験モジュールを診断する診断部と、を備える診断装置を提供する。

(もっと読む)

試験装置の制御方法

【課題】 複数の測定ステーションのいずれを用いても正常に点検を実施することができる、試験装置の制御方法を提供する。

【解決手段】 試験装置の制御方法は、複数の被試験デバイスステーションと、同じ項目を測定可能な複数の測定部と、複数の被試験デバイスステーションと複数の測定部との接続組合せを変更可能なマトリクススイッチと、を備える試験装置において、複数の測定部を用いて標準デバイスを測定することによって測定部の点検を行う測定部点検ステップを複数の測定部に対して行う第1ステップと、被試験デバイスステーションに標準サンプルを搭載し標準サンプルが搭載された被試験デバイスステーションと接続された測定部を用いて標準サンプルの点検を行う被試験デバイスステーション点検ステップを複数の被試験デバイスステーションに対して行う第2ステップと、を含む。

(もっと読む)

差動バッファのテスト方法およびテスト回路

【課題】簡単な構成で差動信号のオフセット電圧と差動電圧の評価を行うことができる差動バッファのテスト方法およびテスト回路を提供する。

【解決手段】テスト回路は、差動バッファから出力される差動信号の各々とテスタの第1および第2のテストチャネルとの間にそれぞれ接続された第1および第2の抵抗素子と、第1の抵抗素子と第1のテストチャネルの間の第1のノードと、第2の抵抗素子と第2のテストチャネルの間の第2のノードと、の間に接続された容量素子とを備えている。このテスト回路を用いて、テスタにより、テストパターンに基づいて、差動バッファのオフセット電圧と差動電圧の評価を行う。

(もっと読む)

1 - 20 / 78

[ Back to top ]