Fターム[4M104FF29]の内容

半導体の電極 (138,591) | 構造 (12,435) | コンタクト面の位置、配置 (799) | 合金化による潜り込み (29) | 領域を越えるもの (6)

Fターム[4M104FF29]に分類される特許

1 - 6 / 6

半導体装置及びその製造方法

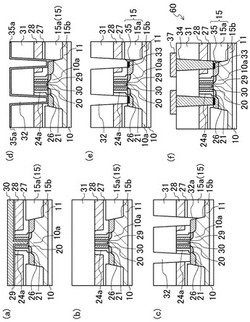

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタのn型化合物半導体コンタクト層と、その上に設けられた絶縁膜との界面に存在する界面電荷により、M型コンタクト層内に空乏層が形成され、それに伴い電流の通り道となる部分が狭窄し、遮断周波数Ftが低下するという課題に対する解決手段を提供する。

【解決手段】このコンタクト層を、n型不純物によりドープされた下層とノンドープの上層から成る構成とした。これにより、たとえ界面電荷が存在する場合であっても、電流の通り道であるn型不純物によりドープされた下層とは充分離れた位置にあることとなる。よって、コンタクト層と絶縁膜との界面準位に起因する負電荷によるコンタクト層上部の空乏化に伴う電流の通り道となる部分の狭窄を防ぐことができる。

(もっと読む)

半導体装置

【課題】半導体膜の厚みを適当な範囲に制御することによって、大きいドレイン電流を有するとともに、所望の電気的特性を備える半導体装置を提供する。

【解決手段】半導体装置は、主表面1aを有するガラス基板1と、主表面1a上に設けられ、チャネル領域11と、チャネル領域11の両側に位置するソース領域9およびドレイン領域13とが形成されたポリシリコン膜7と、ポリシリコン膜7に接触するように設けられたゲート絶縁膜17と、ゲート絶縁膜17を介してチャネル領域11に向い合う位置に設けられたゲート電極21とを備える。ポリシリコン膜7は、50nmを超え150nm以下の厚みを有する。ソース領域9およびドレイン領域13は、ポリシリコン膜7の頂面7aからポリシリコン膜7の底面7cにまで達して形成されている。

(もっと読む)

成膜方法及び処理装置

【課題】クリーニング処理開始前の被処理体の処理枚数に関係なく、ジャストエッチの時点を自動的に確実に把握することにより、エッチング処理の適正な終点時点を決定することが可能な処理装置を提供する。

【解決手段】真空引き可能になされた処理チャンバー16と、所定の処理が施される被処理体Wを載置する載置台20と、処理チャンバーへ必要なガスを供給するガス供給手段40と、途中に真空ポンプが介設されて処理チャンバー内の雰囲気を真空引きする排気系6とを有す処理装置において、排気ガス中に含まれるパーティクル数を計測するために前記排気系に設けられたパーティクル計測手段8と、処理チャンバー内にクリーニングガスを流してクリーニング処理を行う時にパーティクル計測手段の計測値に基づいてクリーニング処理の終点時点を決定するクリーニング終点決定手段14とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】オーミック電極である第1ソース電極と第1ドレイン電極は、ゲートのリセスエッチングのためのマスクとしての窒化膜を開口して形成されるため、窒化膜との間に隙間Gが形成される。このためガルバニック効果によりオーミック電極端部のキャップ層がエッチングされ、オン抵抗が増大する問題がある。

【解決手段】初期窒化膜を全面除去した後、オーミック電極を形成し、キャップ層とオーミック電極の段差を密着して覆う第1窒化膜を形成する。ゲートのリセスエッチングは、第1窒化膜をマスクとして行うと、オーミック電極の端部に隙間Gが形成されない。従って、ガルバニック効果を抑制し、オン抵抗の増大を抑制できる。

(もっと読む)

1 - 6 / 6

[ Back to top ]