Fターム[4M119BB12]の内容

MRAM・スピンメモリ技術 (17,699) | 記憶素子の種類 (1,713) | トランジスタ型(三端子素子) (46) | FET型 (42)

Fターム[4M119BB12]の下位に属するFターム

スピンFET (38)

スピン依存単電子トランジスタ (1)

Fターム[4M119BB12]に分類される特許

1 - 3 / 3

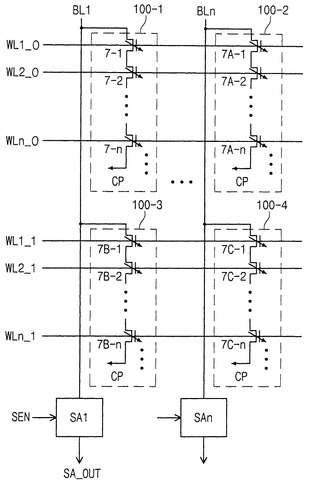

磁気抵抗ラム

【課題】セル構造が簡単かつセルサイズが小さく、従って製造工程が容易な磁気抵抗ラムを提供すること。

【解決手段】1つのビットラインとセルプレートとの間にNAND型に直列連結され、各々のゲートに複数のワードラインの信号が印加されるMRAMセルグループ、及び前記1つのビットラインに連結されセンスアンプイネーブル信号が印加されると、前記ビットラインに印加されたデータをセンシングするセンスアンプを備え、もしくは、

ビットラインとセルプレートとの間にNAND型に直列接続され、各々のゲート端子に複数のワードラインの信号が印加されるMRAMセルグループ、及び前記ビットラインに接続され前記MRAMセルグループに流れる電流を電圧に変換した後、前記MRAMセルグループ内のMTJの磁気分極方向の差による多重データを検出する多重データ検出回路を備える。

【選択図】図15  (もっと読む)

(もっと読む)

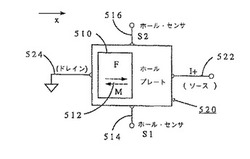

ホール効果装置及びその動作方法

【課題】 強磁性体構成要素を含む改良されたホール効果素子であって、例えば、ディジタルの組合わせ可能なタスクを実行する論理応用例や、磁界センサ等においてディジタル情報の不揮発性記憶装置用のメモリ素子として使用可能なホール効果素子を提供する。

【解決手段】 ホール・プレート520の一部を覆って該ホール・プレート520から電気的に絶縁されている強磁性体層510を含む。ホール・プレート520上のこの強磁性体層510は、外部的に印加された磁界によって変更可能であり、この素子がメモリ要素として用いられると、当該素子が2つの異なるデータ値(0或いは1)に対応し得る2つの安定磁化状態(正及び負)を異方性軸に沿って有することを可能としている。

(もっと読む)

半導体集積回路

【課題】 信頼性高く不揮発記憶を書き込めるようにする。非記憶と不揮発記憶の両方、一時記憶(揮発記憶)と不揮発記憶の両方を一つの回路で行い得るようにする。

【解決手段】 前段回路の情報を状態検地強調回路Aを介して本段回路に書き込む。制御信号V selectがL、即ち/V selectがHの時、回路Aでは小電圧のVcc0とVss0が選択され、これが前段回路に印加される。この時、本段回路のn-Tr2のゲート-p型基板端子間には0V以上Vcc0-Vss0以下の電位しか印加されないのでオフとオンの判別が可能な程度にチャネル抵抗は変化するが十分な不揮発記憶書き込みを行うほどではない。V selectがH、即ち/V selectがLに変わると、回路Aでは大電圧のVcc3とVss3が選択され、これが前段回路に印加される。V selectがHになる直前のVnの論理がHならば、n-Tr2には不揮発オン状態の書込が行われ、p-Tr2には不揮発オフ状態の書込が行われる。

(もっと読む)

1 - 3 / 3

[ Back to top ]