Fターム[4M119GG10]の内容

MRAM・スピンメモリ技術 (17,699) | レイアウト (382) | その他構成のレイアウト (10)

Fターム[4M119GG10]に分類される特許

1 - 10 / 10

半導体装置の製造方法および半導体装置

【課題】孤立パターンに銅の化合物が析出するのを抑制する半導体装置の製造方法と、半導体装置とを提供する。

【解決手段】半導体装置では、素子・基板層ESLの低誘電率膜LOW1、ファイン層FLの極低誘電率膜ELK1等およびセミグローバル層SGLの低誘電率膜LOW2等のそれぞれの開口部に形成されるアライメントマークAMおよび重ね合わせ検査マークKMが、半導体基板SUBに形成された所定の導電型の不純物領域IRに電気的に接続されて、アライメントマークAMおよび重ね合わせ検査マークKMが接地電位に固定されている。

(もっと読む)

集積磁気薄膜増強回路素子を有する磁気抵抗ランダムアクセスメモリ(MRAM)

半導体集積回路装置

【課題】設計工数をほとんど掛けないで、CMP対策及び短時間光アニール対策の両対策に最適化されたダミーパターンを有する半導体集積回路装置を提供すること。

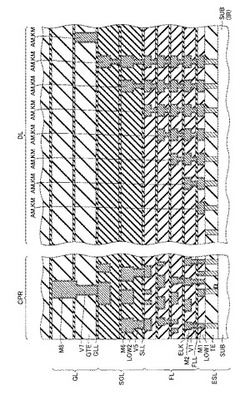

【解決手段】基板上に、メモリマクロ領域10及び機能回路領域20を有する半導体集積回路装置1において、機能回路領域20間、及び、メモリマクロ領域10と機能回路領域20との間に配置されるとともにダミーパターン41を含むダミーパターン領域40を備え、ダミーパターン41は、前記メモリセルアレイ領域におけるメモリセルパターン11の拡散層12、13及びゲート電極14と同等のパターンであり、ダミーパターン領域40におけるダミー拡散層42、43及びダミーゲート電極44の面積率は、メモリセルアレイ領域における拡散層12、13及びゲート電極14の面積率と同等以上である。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

磁気記録媒体再生装置、磁気記録媒体、および、磁気記録媒体再生方法

【課題】磁性細線でトラックを形成した磁気記録媒体を対象として、磁区の移動によるデータの消失を防ぐと共に、磁性細線の記録層を有効に記録、保存、再生に活用し、実質的に使用されていない空き容量を減少させることができる磁気記録媒体再生装置、これに用いる磁気記録媒体、および、磁気記録媒体再生方法を提供する。

【解決手段】パルス電流を、磁性細線5の一端から他端に向かう細線方向に供給する電流供給手段10と、磁性細線5の書込領域にデータの記録を行うデータ記録手段20と、読出領域に記録されているデータを再生するデータ再生手段30と、あふれデータ検出領域に記録されているデータを検出するあふれデータ検出手段40と、あふれデータ検出手段40で検出されたデータを、再書込領域に再度記録するあふれデータ再記録手段50と、を備えることを特徴とする。

(もっと読む)

半導体パッケージ

【課題】磁気メモリ素子に記憶された情報を不正な手段で読み出すことを困難にして、磁気メモリ素子に記憶された情報が漏洩することを抑制できる半導体パッケージを提供すること。

【解決手段】磁気を加えることにより情報を記憶するメモリセル11を有するダイ10を内部に備える半導体パッケージ1であって、パッケージ本体20の内部に配置され、メモリセル11の磁気メモリ素子を磁化可能な磁界MF1を少なくともメモリセル11が位置する空間に発生させる磁界源41と、ダイ10の基板面10Aを覆って配置され、メモリセル11に加わる磁界MF1を減衰させる磁気シールド材42と、を備えることを特徴とする。

(もっと読む)

積層メモリ素子

【課題】高集積化が容易な積層メモリ素子を提供する。

【解決手段】本願発明の積層メモリ素子は、基板と、基板上に互いに積層された、少なくとも1層のメモリ層をそれぞれ含む複数のメモリグループと、該複数のメモリグループのうち、複数の隣接した2つのメモリグループ間に介在する複数のXデコーダ層と、前記複数の隣接した2つのメモリグループ間に、複数のXデコーダ層と交互に介在される複数のYデコーダ層と、を具備する積層メモリ素子である。

(もっと読む)

積層メモリ素子

【課題】集積度を高めることが容易な3次元積層された多層構造メモリ素子を提供する。

【解決手段】本積層メモリ素子は、基板と、基板上に相互積層され、複数の群に分割された複数のメモリ層と、各群内のメモリ層と電気的に接続され、各群内のメモリ層の間に配された複数のインターデコーダと、複数のインターデコーダと電気的に接続され、複数のインターデコーダの間に配された少なくとも一つのプレデコーダと、を備えることを特徴とする。

(もっと読む)

対称なSTT−MRAMビットセルデザイン

対称なスピントランスファトルク磁気抵抗ランダムアクセスメモリ(STT−MRAM)ビットセルおよびSTT−MRAMビットセルアレイが示される。STT−MRAMビットセルは、ポリシリコン層、磁気トンネル接合(MTJ)記憶素子およびボトム電極(BE)プレートを含んでいる。 (もっと読む)

電気機械メモリ、それを用いた電気回路及び電気機械メモリの駆動方法

【課題】従来の半導体プロセスとの親和性が高く、機械的に電気的導通路を完全遮断するスイッチング機能を有し、かつ不揮発性の情報記録を可能とするメモリ素子を実現する。

【解決手段】基板上に形成された電気機械メモリであって、メモリセルを電極で挟む形で形成されており、ポスト部を介して中空に架橋された梁である可動電極を具備した電気機械メモリを実現する。この構成により、簡易な構造で不揮発性メモリを実現することが可能となり、従来実現困難であった低消費電力、低コストの高性能電気機械メモリおよびそれを用いた電気機器が実現可能となる。

(もっと読む)

1 - 10 / 10

[ Back to top ]