Fターム[5B013BB00]の内容

先行制御 (1,991) | 分岐制御 (338)

Fターム[5B013BB00]の下位に属するFターム

Fターム[5B013BB00]に分類される特許

1 - 3 / 3

VLIWプロセッサと命令構造と命令実行方法

【課題】VLIWプロセッサにおいて、小さな回路規模で複雑な条件判定処理を効率良く実行する。

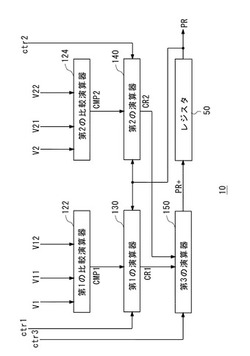

【解決手段】第1の演算器130は、第1の制御信号ctr1に応じて、第1の比較演算器122の出力、該出力とレジスタ50が既に保持している値の論理積、論理和のうちの1つを第1の演算結果CR1として出力する。第2の演算器140は、第2の制御信号ctr2に応じて、第2の比較演算器124の出力と、該出力とレジスタ50が既に保持している値の論理積、論理和の3つのうちの1つを第2の演算結果CR2として出力する。第3の演算器150は、第3の制御信号ctr3に応じて、第1の演算結果CR1、第1の演算結果CR1と第2の演算結果CR2の論理積、論理和のうちの1つを実行結果としてレジスタ50に出力する。レジスタ50は、第3の演算器150からの実行結果を新たに保持し、出力する。

(もっと読む)

プロシージャリターンシーケンスを加速するための方法およびシステム

パイプラインプロセッサの中のプロシージャから戻るときにリンクスタックからリターンアドレスを取り出すための方法が、開示される。本方法は、ソフトウェアスタックからリターンアドレスを取り出すように動作可能な検索命令を識別する。本方法は、さらに、リターンアドレスへと分岐するように動作可能なブランチ命令を識別する。本方法は、識別される命令とブランチ命令との両方に応じてリターンアドレスをリンクスタックから取り出し、そしてリターンアドレスを使用して命令をフェッチする。  (もっと読む)

(もっと読む)

非シーケンシャル命令アドレスをプリフェッチするための方法および装置

プロセッサは、非シーケンシャル命令アドレス上で、プリフェッチオペレーションを実行する。第1の命令アドレスが、命令キャッシュにおいてミスし、フェッチオペレーションの一部として高次メモリにアクセスし、また、第1の命令アドレスあるいは第1の命令アドレスに続くアドレスに関連づけられる分岐命令が、検出され、成立と予測される場合、プリフェッチオペレーションは、高次メモリアクセスの間に、予測される分岐ターゲットアドレスを使用して実行される。予測される分岐ターゲットアドレスが、プリフェッチオペレーションの間に命令キャッシュにおいてヒットする場合には、関連する命令は、電力を維持するために、検索されない。予測される分岐ターゲットアドレスが、プリフェッチオペレーションの間に、命令キャッシュにおいてミスする場合には、高次メモリアクセスは、予測される分岐命令アドレスを使用して、起動されることができる。いずれの場合においても、第1の命令アドレスは、その高次メモリアクセスから命令の戻りを待つためにフェッチステージパイプラインへとリロードされる。  (もっと読む)

(もっと読む)

1 - 3 / 3

[ Back to top ]