Fターム[5B016FA02]の内容

位取り記数法を用いた四則演算 (704) | キャリの処理 (32) | キャリ先見(CLA) (7)

Fターム[5B016FA02]の下位に属するFターム

キャリの有無検出 (2)

Fターム[5B016FA02]に分類される特許

1 - 5 / 5

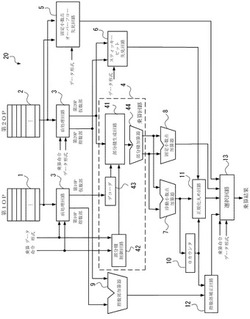

ベクトル乗算処理装置および方法ならびにプログラム

【課題】オペランドのシフトを要することなく消費電力の削減をはかる。

【解決手段】高速化回路(固定小数点オーバーフロー先見回路5、スティッキービット先見回路6)を備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置であって、高速化回路を使用し、入力される第1オペランドと第2オペランドとの部分積を生成し、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する乗算回路4(部分積生成回路41、部分積制御回路42)、を備える。

(もっと読む)

複合加算回路アレイ及びAND/OR面

【課題】全加算回路グループを変更し、所定の数の入力ビットの論理関数を計算する方法を提供する。

【解決手段】前記全加算回路のそれぞれは、第1及び第2データ入力、データ出力、桁上げ入力、及び桁上げ出力を有する。前記全加算回路は相互に接続されて桁上げチェーンを構成する。前記方法は、前記全加算回路のそれぞれの第1の入力を同じ固定値に設定する工程と、前記所定の数の入力ビットをそれぞれ前記全加算回路の第2の入力に接続する工程と、前記全加算回路のアレイからなる桁上げチェーンの出力を前記論理関数の結果として用いる工程とを備える。

(もっと読む)

条件選択加算器

【課題】条件選択加算器を提供する。

【解決手段】条件選択加算器は、第1信号生成部、第2信号生成部、及び合算回路を含む。第1信号生成部は、合算される被演算子対に応答して、キャリー生成信号及びキャリー伝達信号を生成する。第2信号生成部は、キャリー生成信号及びキャリー伝達信号に応答してブロックキャリー信号と入力キャリー信号を生成する。第2信号生成部は、少なくとも1つ以上のリーフセルを具備する少なくとも1つ以上のグループを含む。グループは、各グループに含まれるリーフセルの数が少ない第1グループから各グループに含まれるリーフセルの数が多い第2グループに、リーフセルの個数によって昇冪の順にグループ化され配置される。合算回路は、ブロックキャリー信号、キャリー伝達信号、及び入力キャリー信号に応答して被演算子の和を生成する。合算回路は、グループバイパス回路と合算部を含むことができる。

(もっと読む)

ダイナミック回路

【課題】ダイナミック回路において、評価制御トランジスタを省略してトランジスタのスタック段数を削減するとともに評価制御トランジスタの省略に伴う初期化動作時の貫通電流の発生を抑制する。

【解決手段】ダイナミック回路は、ダイナミックノード(10)、複数の入力信号についての論理評価結果に応じてダイナミックノード(10)の充電状態を変化させる評価回路(30)、評価回路(30)のレプリカ回路(403)による論理評価結果に応じて論理レベルが変化する制御信号を出力する制御回路(40)、制御回路(40)及び外部からそれぞれ制御信号を受け、これら制御信号に従ってダイナミックノード(10)の初期化の開始及び停止を制御する初期化回路(20)を備えている。

(もっと読む)

合計セルと結合されたキャリースキップセルを具備するキャリースキップ加算器

マルチビット加算器はキャリーチェーン、キャリースキップ・ネットワーク、合計セル、及びキャリー合計セルを有する。キャリーチェーンはキャリーインビットを伝播、生成又はキルする。キャリースキップ・ネットワークは、キャリーチェーンの少なくとも一部にわたってキャリーインビットを選択的にスキップさせるように、キャリーチェーンに結合されている。合計セルは、2つのオペランドの対応するビットを用いてキャリーインビットを加算するようにキャリーチェーンに沿って結合され、マルチビットの結果を生成する。キャリー合計セルは、キャリーインビットの、キャリーチェーン上の単一の中間ビット位置への1つを受け取って、マルチビットの結果の、上記単一の中間ビット位置より上位のビット位置を有する1ビットを生成するように結合されている。  (もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]