Fターム[5B018NA07]の内容

記憶装置の信頼性向上技術 (13,264) | メモリの種類 (2,134) | マルチポートメモリ (2)

Fターム[5B018NA07]に分類される特許

1 - 2 / 2

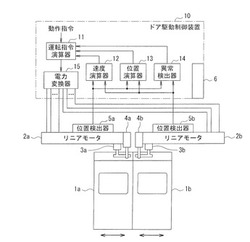

車両用ドア駆動制御検査装置、車両用ドア駆動制御検査方法および車両用ドア駆動制御検査プログラム

【課題】簡易な装置にて異常個所をフィールドで特定することが可能な車両用ドア駆動制御検査装置を提供する。

【解決手段】書き込み指令手段202は、デュアルポートRAM101に接続されたCPU1、4に対してデュアルポートRAM101に対する書き込み指令を行い、読み出しデータ受信手段203は、CPU1、4にてデュアルポートRAM101から読み出された読み出しデータを受信し、故障診断手段204は、書き込み指令手段202にて指令された書き込みデータと、読み出しデータ受信手段203にて受信された読み出しデータとの比較結果に基づいて、デュアルポートRAM101の故障を診断する。

(もっと読む)

半導体回路装置及び誤り検出回路

【課題】データ書き込み時の方向と直交する方向に連続するメモリセルに記憶されたデータ列を該データ列単位で順次読み出すことが可能な半導体回路装置において、前記読み出したデータ列の誤り検出を行うのに好適な半導体回路装置を提供する。

【解決手段】半導体回路装置1の誤り検出回路43を、列誤り検出回路50_0〜50_nと、誤り検出用OR回路51とを含んだ構成とし、各列誤り検出回路において、LCDからのクロック信号LCD_CKに同期してメモリセルアレイ21から行単位に順に読み出される表示用データLCD_RDの、1ライン目の読み出し時において同じ1周期にパリティデータPTDを読み出し、行単位で順次読み出される各ラインにおける列方向に書き込まれた各ビットデータと1つ前の演算結果との排他的論理和演算を順次行い、表示用データCPU_WDに対する最終的な演算結果を誤り検出用OR回路51に出力する構成とした。

(もっと読む)

1 - 2 / 2

[ Back to top ]