Fターム[5B033DC01]の内容

Fターム[5B033DC01]の下位に属するFターム

バウンダリ、アラインメント (10)

データ転送幅変換 (4)

オペランド重複

命令切出 (3)

バイト・ワード処理 (6)

Fターム[5B033DC01]に分類される特許

1 - 10 / 10

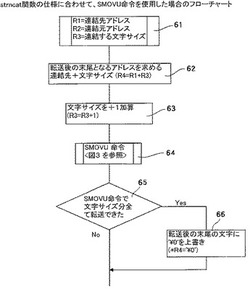

文字列転送命令を用いて文字列連結関数の動作を行う方法及びプログラム

【課題】RXCコンパイラが用意する文字列操作をおこなう標準ライブラリ関数strncatに対して、直接に文字列操作命令であるSMOVUを当てはめて、strncat関数のオブジェクトサイズを増やすことなく、実行サイクル数を大幅に削減する。

【解決手段】演算処理装置が、連結先アドレスR1、連結元アドレスR2、及び、連結する文字サイズR3を入力データとし、連結先アドレスR1に文字サイズR3を加算することにより、転送後の末尾のアドレスR4を得るとともに、前記文字サイズR3に1を加算し、転送後の末尾のアドレスR4、連結元アドレスR2、及び、1を加算された文字サイズを入力データとして、文字列転送命令を実行し、実行後、1を加算された文字サイズ分全て転送できたか否かを判断し、全て転送できた場合に転送後の末尾の文字に'\0'を上書きする。

(もっと読む)

データ選択とデータ整列またはデータ複製とを組み合わせることを含む多段階の多重化操作

データ選択とデータ整列またはデータ複製とを組み合わせることを含む、多段階の多重化操作が開示される。ある具体的な実施形態では、方法は、多段階の多重化操作の第1の段階を実行するステップを含む。第1の段階の間に、第1のデータソースが、第1の複数のデータソースから選択される。第1のデータ整列操作と第1のデータ複製操作のうちの少なくとも1つも、第1の段階の間に選択された第1のデータソースからの第1のデータに対して、実行される。  (もっと読む)

(もっと読む)

状態遷移管理装置及びその状態遷移管理方法

【課題】メモリを用いて状態遷移の管理を行う状態遷移管理装置において、メモリの使用効率を高める。

【解決手段】現在の状態番号に対する次状態番号候補を格納したメモリ101と、メモリから読み出した次状態番号候補の中から次状態番号を選択する選択回路(104、105、113、114)を備える。メモリは、現在の状態番号に対する分岐先である次状態番号候補の数が少ない状態番号に対しては、複数の状態番号に対する次状態番号候補をメモリの同時に読み出し可能なアドレスに格納する。選択回路は、イベント識別コード(109、110)と、現在の状態番号108と、から次状態番号を選択する。

(もっと読む)

信号処理プロセッサ及び半導体装置

【課題】データの型に応じてアドレス変位値が適切に設定される、信号処理プロセッサ及び半導体装置を提供する。

【解決手段】アドレスデータを記憶するアドレス・レジスタ122と、デコード部110でデコードされたデータ演算命令とアドレス・レジスタ122に記憶されるアドレスデータに基づいてメモリ200にアクセスするメモリアクセス部170とを含む信号処理プロセッサにおいて、アドレスデータに対応するメモリ200に記憶されるデータの属性情報を、アドレス・レジスタ122に関連付けて記憶する属性情報保持部124と、メモリアクセス部170がアドレス・レジスタ122からアドレスデータを読み出す際に所与のアドレス変位値をアドレスデータに加算するアドレス更新処理を行うアドレス更新処理部141,161を含み、アドレス更新処理部141,161は、所与のアドレス変位値を属性情報に基づいて制御する。

(もっと読む)

信号処理プロセッサ及び半導体装置

【課題】データ演算命令の種類の増加や語長を抑制した、信号処理プロセッサ及び半導体装置を提供する。

【解決手段】アドレスデータを記憶するアドレス・レジスタ122と、データ演算命令をデコードするデコード部110と、デコード部110でデコードされたデータ演算命令と、アドレス・レジスタ122に記憶されるアドレスデータに基づいてメモリ200からのデータを読み出す読み出し処理部140と、デコード部110でデコードされたデータ演算命令に基づき、読み出し処理部140により読み出されたデータに対して所与の演算処理を行う演算処理部150を含む信号処理プロセッサ100において、アドレスデータに対応するメモリ200に記憶されるデータの属性情報を、アドレス・レジスタ122に関連付けて記憶する属性情報保持部124を含み、読み出し処理部140は、属性情報に基づいて、メモリ200から読み出すデータのサイズを制御する。

(もっと読む)

情報処理装置

【課題】CPUと拡張演算器を備える情報処理装置において割込み命令が発生した時に、少ない専用命令数で必要なデータ全てを退避させる。

【解決手段】「GETACX Dm,Dn」という1つの専用命令で全てのレジスタからのデータの退避を実現する。Dmは、汎用レジスタ104から第1データ入力バス120に出力される値であり、拡張演算器110の各演算機はそれぞれ自己の値を認識している。Dmが自己を指定する値の場合に各演算機は自己内部のレジスタに格納されているデータをセレクタ116に出力する。拡張演算器情報出力回路117は、拡張演算器110に搭載されている演算器の個数の情報を記憶しており、第1データ入力バス120の値がその数値を上回るとフラグレジスタ102に「1」を出力し、CPU100はフラグレジスタ102の値が「1」になっていることを以ってレジスタからのデータの対比が終了したことを認識する。

(もっと読む)

データプロセッサ

【課題】分岐命令のディスプレースメントの拡張による分岐アドレステーブルの参照において、論理アドレス空間を規定するアドレスのビット数が異なる互換モードに対応する。

【解決手段】データプロセッサは、第1分岐命令の分岐アドレスを生成するとき、論理アドレス空間を規定するアドレスのビット数に応じてディスプレースメント(disp)に乗ずる倍数を最適化し、これによって拡張されたアドレス情報をレジスタ(TBR)の値に加算し、加算によって得られたアドレス情報により分岐アドレステーブルを参照する。参照された情報を分岐アドレスとする。論理アドレス空間を規定するアドレスのビット数の異なる互換モードに対応するには、当該モードに応じてディスプレースメントに乗ずる倍数を変えればよい。

(もっと読む)

データ処理装置

【課題】論理的・物理的規模の増大を最小限とし、データ処理速度を向上する。

【解決手段】命令中のディスプレースメント(基準アドレス)と、汎用レジスタ(ER0〜ER7)に割当てられるインデックスレジスタが保有する情報とから実効アドレスを計算するアドレッシングモードを設ける。メモリをアクセスするサイズに応じて、バイトであればインデックスレジスタの値を×1とし、ワードであれば×2というようにシフトする。実効アドレスの計算に、前記拡張およびシフトを含むことにより、命令数を削減し、実行ステート数も短縮できる。配列の大きさは、アドレス空間の大きさより小さいから、汎用レジスタの上位を、別のデータレジスタとして使用し、汎用レジスタに配置できるデータの量を増加でき、メモリとのリードライトの回数を削減することによって、命令数を更に削減し、プログラム容量を削減することができる。

(もっと読む)

プロセッサ

【課題】 メモリ上のビット列を効率良くレジスタへ読み込んだり、レジスタ内のビット列をメモリへ効率良く書き込むことができるようにする。

【解決手段】 制御手段60が、読み込み処理のときに、ビットストリーム・ポインタ10に記憶されたメモリ上の基準位置、及び、ビットストリーム・カウンタ30に記憶されたビット列データのビット数に基づいて、ビットストリーム・バッファ20に記憶されたビット列データを介し、メモリ上に格納されている読み込みデータをレジスタへ格納し、書き込み処理のときに、ビットストリーム・ポインタ10に記憶されたメモリ上の基準位置、及び、ビットストリーム・カウンタ30に記憶されたビット列データのビット数に基づいて、ビットストリーム・バッファ20に記憶されたビット列データを介し、レジスタに格納されている書き込みデータをメモリに格納するようにする。

(もっと読む)

データ演算装置

【課題】 プロセッサの処理効率を向上し、プログラムコストおよび製造コストを低減するのに好適なデータ演算装置を提供する。

【解決手段】 データ演算部12は、複数のレジスタからなるレジスタファイル200と、レジスタファイル200のデータを用いて演算を行う演算器202とを備え、レジスタファイル200とデータメモリ10との間のデータアクセスを、4つのレジスタからなるグループレジスタ単位で行う。また、2つのグループレジスタをレジスタブロックとしてグループ化したときに、レジスタブロック内のデータの位置を指定するエレメントインデックスデータを記憶するインデックスレジスタファイル208と、インデックスレジスタファイル208のエレメントインデックスデータに基づいて、レジスタブロックのレジスタのなかからいずれか1つのレジスタのデータを選択して演算器202に出力するセレクタ204,206とを備える。

(もっと読む)

1 - 10 / 10

[ Back to top ]