Fターム[5B045EE18]の内容

Fターム[5B045EE18]の下位に属するFターム

テストアンドセット方式 (3)

トークンによるもの (3)

Fターム[5B045EE18]に分類される特許

1 - 11 / 11

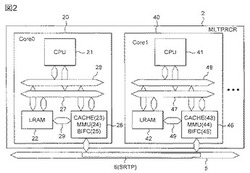

データプロセッサ

【課題】プロセッサコアのローカルメモリや共有メモリの所要のアドレスに対して小さな回路規模で排他制御を行うことができるデータプロセッサを提供する。

【解決手段】要求に従ってバスロック設定と解除が可能にされるシステムバス(5)を共有する複数個のプロセッサコア(20,40)が相互に互いの内部リソース(22,42)を共有するデータプロセッサ(1)において、プロセッサコアが内部リソースの第1アドレス(ロック変数割り当てアドレス)へアクセスを行うときバスロックの要求を伴って当該アクセス要求をシステムバスに出力することによりシステムバスにバスをロックさせると共にシステムバスから当該プロセッサコアに帰還されるのを待って当該アクセス要求を処理し、プロセッサコアが内部の第2アドレスへアクセスを行うとき当該アクセス要求をプロセッサコアの内部で処理する。

(もっと読む)

記憶装置への情報蓄積制御方法

【課題】 キューのオーバフローを防止する情報蓄積制御方法を提案する。

【解決手段】 処理要求を順次記憶する第1の記憶手段と、前記第1の記憶手段に記憶可能な処理要求の数を超えない値に設定されたセマフォ変数を記憶する第2の記憶手段と、前記第1の記憶手段に記憶された処理要求についての処理完了に応じて処理結果に関するデータを順次記憶する記憶手段であって、前記第1の記憶手段に記憶可能な処理要求の数以上の数の前記データを格納可能な第3の記憶手段と、前記処理要求の前記第1の記憶手段への記憶に応じて、前記セマフォ変数を1減少させ、前記第3の記憶手段からの前記データの読み出しに応じて前記セマフォ変数を1増加させる処理を行う処理手段とを備え、前記第1の記憶手段への更なる処理要求の記憶は、前記セマフォ変数の値が正であることを条件に行われる、ことを特長とする情報処理装置。

(もっと読む)

マルチプロセッサ間通信方法

【課題】各プロセッサ間での共有リソースの送受を比較的簡易で汎用性のある形態で実現する共有リソースのプロセッサ間通信方法を提供する。

【解決手段】複数のプロセッサによって共通に使用される共有リソース領域と該共有リソース領域を管理する共有リソース管理領域とを有する共有メモリを備え、前記複数のプロセッサ相互で排他制御が必要な共有リソースの送受を前記共有メモリを経由して行うマルチプロセッサ間通信方法において、前記共有リソース領域に、前記複数のプロセッサ相互のタスク(スレッド)にてリード/ライトの制御種別で分類した共有リソースに対し、各共有リソース毎にリングバッファによるバッファ機能を持たせて多重化を可能とすると共に、前記共有リソースのリード/ライトの制御時に参照と更新処理が可能な前記共有リソースに対する前記リングバッファのインデックスを簡易的な排他制御管理領域として設けた。

(もっと読む)

共有メモリのアクセス監視方法及び装置

【課題】マルチプロセッサシステムの型式に関わらず、任意のプロセッサからの共有メモリに対するアクセス情報を監視することが可能な共有メモリのアクセス監視方法及び装置を提供する。

【解決手段】共有メモリボード100のバスインタフェース部110は、複数のプロセッサ210_1〜210_nの内の任意の要求元プロセッサ210_1から、プロセッサの識別子(210_1)及び共有メモリSMに対するアクセス権の獲得要求RQ1(又は解放要求)が設定されたリクエストパケットRPを受信する。そして、バスインタフェース部110は、アクセス権の獲得要求RQ1(又は解放要求)に応じて、共有メモリSMに要求元プロセッサの識別子(210_1)を設定(又は解除)すると共に要求元プロセッサの識別子(210_1)の設定(又は解除)に対応してアクセス権の獲得ACK1(又は解放)を示すアンサパケットAPを生成し、全てのプロセッサ210_1〜210_nにブロードキャストする。

(もっと読む)

デバイスシステム

【課題】ループバスの初期化のためにいずれかのノードをマスタノードとすると、構成変更によりマスタノードがなくなってしまう。そこで、全てのノードが初期化を実行可能な構成とすると、デバイスシステムの製造コストが跳ね上がる。

【解決手段】デバイスシステムであって、少なくとも2以上のデバイスはプロセッサで構成されており、通信経路は第1のノードと、少なくとも1つの第2のノードと、を順に接続することによりループ状に形成され、複数のパケット要素から成るパケットを一方向に巡回させることができ、各ノードは他のノードと略同期して、パケットをパケット要素単位で順次入力し、パケット要素単位で順次送出し、第2のノードはパケットをパケット要素単位で送出する際に、ヘッダ部であることを示すフラグまたはペイロード部であることを示すフラグのうち、送出する順序に応じて、いずれかのフラグを第1のフラグとしてパケット要素に付加する。

(もっと読む)

非対称型異種マルチプロセッサ環境でアトミック更新プリミティブを提供するための方法

【課題】 DMA転送との共有メモリを有する、非対称型単一チップ異種マルチプロセッサ・コンピュータ・システムに、アトミック更新のプリミティブを提供すること。

【解決手段】 予約付きゲット・ロック・ライン・コマンド、条件付きプット・ロック・ライン・コマンド、および無条件プット・ロック・ライン・コマンドを有するセットから、少なくとも1つのロック・ライン・コマンドが生成される。

(もっと読む)

マルチプロセッサシステム、及びマルチプロセッサシステムのメッセージ伝達方法

【課題】

プロセッサ間通信のスループットを向上させ、送受信するメッセージの優先順位に基づいたプロセッサ間通信を実行する。

【解決手段】

複数のプロセッサ2−1〜2−nと、メモリ3とを具備するマルチプロセッサシステムを用いる。メモリ3は、複数のプロセッサ2−1〜2−nの各々にバス4を介して接続されている。メモリ3は、複数のプロセッサ2−1〜2−nの各々から他のものへ送信されるメッセージを格納している。メモリ3は、メッセージを受信する側としての複数のプロセッサ2−1〜2−nに対応した複数の第1バッファ領域8−1〜8−nを備えている。

(もっと読む)

マルチプロセッサシステム及びロックフラグ操作方法

【課題】 本発明は、排他制御に必要な処理時間が短いマルチプロセッサシステムを提供することを目的とする。

【解決手段】 マルチプロセッサシステムは、複数のプロセッサと、複数のプロセッサに共通に結合される共有バスと、共有バスに結合され複数のプロセッサにより共有されるリソースと、複数のプロセッサに共通に結合されリソースの排他的使用のためのロック/ロック解除を示すロックフラグを有する排他制御機構を含み、複数のプロセッサの各々は排他制御機構に結合される特殊用途レジスタ・インターフェースを含み、特殊用途レジスタ・インターフェースを介した特殊用途レジスタアクセスによりロックフラグにアクセスするよう構成されることを特徴とする。

(もっと読む)

プロセッサ

【課題】簡潔な構成で、処理能力の大幅な低下を招くことなく、他のプロセッサの動作や割り込み処理に対するアトミック性を確保する。

【解決手段】アドレス格納部131はアトミックオペレーションでアクセスされるメインメモリ3のアドレスを格納する。データ格納部132にはメインメモリ3から読み込まれたデータやCPU100によるアトミックオペレーションの処理結果のデータを格納する。割り込み検出フラグ134は割り込み復帰命令が実行されたときにセットされる。メモリアクセス制御部133は、アトミックオペレーションが終了するときに、割り込み検出フラグ134等に応じて判定回路139から出力されるアトミック性保証信号に基づき、処理結果データのメインメモリ3への書き込みを停止する。

(もっと読む)

メモリシステム制御装置およびメモリシステム制御方法

【課題】プロセッサ毎にキャッシュメモリを有するマルチプロセッサシステムにおいて主記憶とのトランザクションを減少させること。

【解決手段】メモリシステム制御装置200が、プロセッサ100a〜100dから書込みを前提としたリード要求を受け、そのデータを要求元のプロセッサに送出した場合に、スヌープキャッシュ更新部233は、スヌープキャッシュにそのデータが「強い更新状態」であることを記憶させる。データ取得手順選択部232は、「強い更新状態」でスヌープキャッシュに存在するデータをプロセッサ100a〜100dから要求された場合には、主記憶300に対して投機リードをおこなわずに、プロセッサのキャッシュメモリからデータを取得する。

(もっと読む)

メモリ排他制御装置、画像処理装置、及び画像形成装置

【課題】複数のCPUそれぞれへの不要な割り込み処理を排除するとともに共有メモリ領域への排他制御を行う。

【解決手段】モード毎に動作するCPUが異なる複数のCPU1,2と、これら複数のCPU1,2が共通で使用するメモリ5と、前記各CPU1,2に対応してそれぞれ設けられたASIC3,4のうち後者のASIC4に搭載され、前記各CPU1,2から前記メモリ5をアクセスするためのアクセス権を要求するアクセス権要求回路と、アクセス権の要求があったとき、他のCPUがアクセス権を取得していない場合にアクセス権を設定するアクセス権管理回路と、2以上の前記アクセス権要求回路が同時にアクセス権要求を行った場合に、前記アクセス権要求回路の要求を調停する調停手段とを備えた。

(もっと読む)

1 - 11 / 11

[ Back to top ]