Fターム[5B047EA10]の内容

Fターム[5B047EA10]に分類される特許

1 - 11 / 11

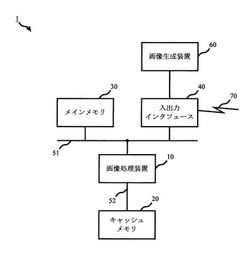

画像処理装置、画像処理システム及び画像処理方法

【課題】シングルポートのSRAMを用いて画像処理装置の処理効率を改善する。

【解決手段】画像処理装置10は、複数の変換前画素値を記憶するメインメモリ30と、複数のキャッシュブロックを有するキャッシュメモリ20とに接続される。カウンタと、座標決定部と、メモリコントローラと、キャッシュアクセス部と、画素値計算部と、出力部とを備える。メモリコントローラは、メインメモリ30に記憶された複数の変換前画素値をそれぞれ、変換前座標に応じたキャッシュブロックへ転送する。キャッシュアクセス部は、複数のキャッシュブロックから、変換後画素値の計算に必要な全ての変換前画素値を1回のキャッシュアクセスで読み出す。画素値計算部は、キャッシュアクセス部が読み出した変換前画素値を参照して、変換後画素値を計算する。出力部は、変換後画素値を出力する。

(もっと読む)

画像変形装置および命令付加装置

【課題】キャッシュミスのないアクセスを可能にする。

【解決手段】画像変形装置10は、画像を格納するフレームメモリ12と、フレームメモリ12に格納された画像に施す変形処理パラメータP1にプリフェッチ命令P2が付加されたプリフェッチ命令付変形処理パラメータP3を格納するパラメータメモリ13と、フレームメモリ12に格納された画像の画素データの一部を一時的に格納することで、フレームメモリ12からの画素データ読み込み効率を向上させるキャッシュメモリ14と、パラメータメモリ13に格納されたプリフェッチ命令P2に従ってフレームメモリ12からキャッシュメモリ14に画素データをロードするプリフェッチ制御部15と、パラメータメモリ13に格納された変形処理パラメータP1を使用してキャッシュメモリ14に格納された画像に変形処理を施す変形処理部16とを備える。

(もっと読む)

画像処理装置およびその制御方法

【課題】外部サーバーがなくても、機器のパフォーマンスをできるだけ落とさない画像処理装置およびその制御方法を提供すること。

【解決手段】画像処理装置は、アクセススピードが速く揮発性であるメモリと、中速度で不揮発性でありデータ破損のリスクがやや高いメモリと、中速度で不揮発性でありデータ破損のリスクがさらに高いメモリと、低速度で不揮発性でありデータ破損リスクがほとんどないメモリをもち、動作状況管理手段にもとづき、データ配置手段でデータを再配置することにより、データ転送性能低下に起因する全体的な動作性能の低下を少なくする。

(もっと読む)

画像処理装置

【課題】不揮発メモリ7に各種データを集約して格納する場合、ブート時にクリアしたいデータとしたくないデータとを使い分ける画像処理装置を提供する。

【解決手段】不揮発メモリ7の領域Aに、ブートプログラム、OS、アプリケーションプログラムを格納し、領域Bにイメージデータを格納し、領域Cに機器設定値等データを格納し、領域Dにデータ変数等を格納する。領域Bをクリアしたいデータ領域、領域A、C、Dをクリアしたくないデータ領域に設定すれば、ブート時に領域Dのデータはクリアされることなく、再利用することができる。領域Dに格納されるデータ変数等は、クリアするかしないかを選択できる書き換え可能なデータであり、領域A、C、Dに格納されるプログラムデータ、機器設定値等は、通常はクリアしないで再利用するデータである。

(もっと読む)

画像データ記憶装置

【課題】 不揮発性記憶媒体の不正な取り外しが生じた場合においても、盗難先で有効な情報を再現できないようにする。

【解決手段】 メモリ/HDD制御部214は、画像処理部213によって画像処理が施された1ページ分の画像データがページメモリ215に蓄積される度に、その画像データを読み出し、HDD218と蓄積メモリ217に分けて転送して書き込む。このとき、1ワード(転送単位)の画像データを最上位ビットから最下位ビットまでD15からD0とすると、最上位ビットD15(所定ビット)を蓄積メモリ217に転送すべき画像データとして処理する。また、残りのデータ(15ビットD14〜D0)を16ビットデータとして再構成し、それをHDD218に転送すべきデータとして処理する。

(もっと読む)

半導体装置およびデータ処理装置

【課題】アドレス制御を容易に実現でき、かつアドレス制御のための回路を簡素化でき、階層構造を持つ異なる解像度の画像データの容量を低減しながら、画像データのアクセスを容易に実現できる半導体装置及び画像データ処理装置を提供する。

【解決手段】メモリセルアレイ10に、画素データと当該画素に対応付けられた付加情報データ、例えば、動きベクトルを示すデータを含む複合データが格納される。読み出しのとき、指定された画素データ及びそれに対応付けられた動きベクトルが読み出され、当該動きベクトルに応じて探索領域が適宜予測され、設定され、例えば、ブロックマッチング法によって動き推定が行われるので、等価的に大きな探索領域において動き推定を行うことができ、動き推定の高速化、効率化を実現でき、動き推定の精度を改善できる。

(もっと読む)

画像入力装置

【課題】固定順位の調停方式と変動順位の調停方式とを組み合わせることにより、画像メモリの1ポートに対して、さまざまなメモリアクセスが発生した場合でも、装置が破綻しないように調停する画像入力装置を提供する。

【解決手段】画像入力装置2は、ホスト機器1との通信はカードバス16経由で行い、取り込み画像サイズ等を設定する内部レジスタ10と、画像データを格納する画像メモリ12と、ホスト機器1での間引き表示を行う画像処理部11aとメモリアクセスの調停を行なうメモリアクセス調停部11bとを有するメモリ制御部11と、ターゲット機器3の画像データインターフェース3aと接続する画像入力インターフェース14と、その各チャンネルに取り込み量をカウントできるFIFO制御部13と、を備えている。尚、FIFO制御部13はそれぞれFIFO(バッファメモリ)を備えている。

(もっと読む)

DDR−SDRAMのアクセス制御方法およびその方法を採用した画像処理装置

【課題】画像処理装置において、DDR−SDRAMを画像メモリとして採用した場合に、CPUアクセスの負担の軽減や画像メモリ上のデータのセキュリティの向上が望まれていた。

【解決手段】DDR−SDRAMの記憶領域を、データ格納領域41とテーブル格納領域42とに分ける。テーブル格納領域42のテーブル情報に、モジュールがデータ格納領域をリードアクセスした後の、データ格納領域に対する処理情報を記憶させておく。モジュールは、データ格納領域41のデータをリードアクセスしてデータ処理を行った後、アクセスしたデータ格納領域41に対して、処理情報に従った処理をする。たとえばデータ格納領域を白塗りしたり、ランダムデータで上書きする。これにより、使用後のデータが消去されるので、データ格納領域におけるデータ記憶のセキュリティが向上する。また、上記データ格納領域の開放は、CPUを介さずに行われるので、CPUアクセスの負担が軽減される。

(もっと読む)

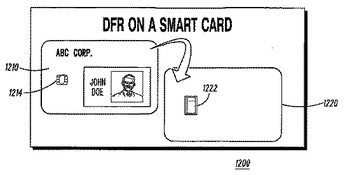

指紋に基づくスマートカード

導電面(22)を通して、指紋接触面(13)を有するエポキシ内に配置されている導電球体(21)に結合されている複数の電荷蓄積デバイス(12)、すなわち共有メモリを有する指紋捕捉デバイス(10)と共有するプロセッサ・デバイスおよびメモリを含むスマートカード回路を含む単一の埋め込まれたICチップ1222を含むスマートカード・デバイス1200。対象物(26)の凸部がいくつかの導電球体(21)と適切に接触すると、対応する電荷蓄積デバイス(12)が、アースしている導電面に接続されている別の導電球体を通して放電する。この放電は、対象物の凹凸フィーチャを感知すると同時に、その感知した情報も記憶する働きをする。  (もっと読む)

(もっと読む)

指紋照合装置

【目的】 指紋照合装置において、採取された指紋データが予め登録されている指紋データと一致しなかった場合には、採取された指紋データをメモリに記録し、誤作動発生時における故障判定に利用する。

【解決手段】 指紋採取部19から出力された指紋パターン(画像データ)を指紋パターン一時記憶部12に保存する。照合部10において特徴点データの照合を行なった結果、特徴点データが一致しなかった場合には、書き込み処理部13によって指紋パターン一時記憶部12の指紋パターンをEEPROM等の記憶部14に記録する。

(もっと読む)

撮影条件管理装置、撮影装置、撮影条件管理システム及びコンピュータ読み取り可能な記憶媒体

【課題】 デジタルビデオカメラ(DVC)が撮影したときの撮影条件をPCに送って管理し、後の撮影で用いることができるようにする。

【解決手段】 PC101とDVC102とは1394シリアルバス103で接続されている。DVCが撮影を行うと、そのときの撮影条件が映像と共に記録される。再生された撮影条件情報は、PCに送られてメモリ111に記憶される。その際、撮影時の状況等の任意の情報を対応させて記憶することにより、撮影条件をライブラリ化することができ、これを後日の撮影に際して使用することができる。

(もっと読む)

1 - 11 / 11

[ Back to top ]