Fターム[5B054AA05]の内容

Fターム[5B054AA05]の下位に属するFターム

メモリのリードライト禁止 (1)

Fターム[5B054AA05]に分類される特許

1 - 3 / 3

画像形成装置、情報処理装置および機能モジュール

【課題】動作可能になるまでの所要時間を短くした情報処理装置等を提供する。

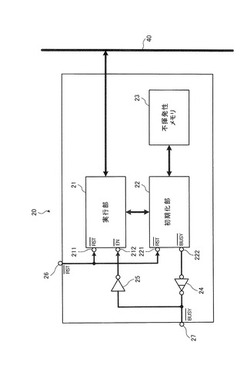

【解決手段】機能モジュール20は、予め定められた機能を実行する実行部21、実行部21を初期状態に設定する初期化部22、実行部21を初期化するためのデータを保持する不揮発性メモリ23、オープンドレインバッファ24、インバータ25を備えている。初期化信号51(/RST)がアサートになると、実行部21は動作状態から停止状態に移行し、初期化部22は停止状態から動作状態に移行する。そして、初期化信号51(/RST)がネゲートになると、初期化部22は、不揮発性メモリ23に保持されていたデータを読み出し、実行部21を初期化する。実行部21の初期化が完了すると、実行部21は停止状態から動作状態に移行する。

(もっと読む)

集積回路装置、マイクロコンピュータ及び電子機器

【課題】直接非同期リセットをいれても誤動作なく処理可能な集積回路の提供。

【解決手段】本集積回路装置10は、非同期リセット入力90が非同期入力に接続されるフィリップフロップ20を含んで構成されるCPU10と、非同期リセット入力90及びクロック入力80に基づき、非同期リセット入力解除後の最初のクロックでディセーブル状態からイネーブル状態に変化するライトディセーブル信号52を生成するライトディセーブル信号生成回路50を含み、CPU10は、ライトディセーブル信号52がディセーブル状態の間は前記フィリップフロップ20へ新たなデータが書き込まれるのを防止する書き込み防止回路60を含む。また非同期リセット入力解除に所定クロックだけ遅延させてディセーブル状態からイネーブル状態に変化するライトディセーブル信号を生成するようにしてもよい。

(もっと読む)

半導体集積回路

【課題】 投入された電源電圧が安定化するまでの間に回路の初期状態を保障し、所定のレジスタ値等を初期値にするとき、外部入出力バッファ回路の出力回路が誤動作する虞を解消する。

【解決手段】 電源検出回路(8D)は外部から供給される電源電圧(VDD,VCC)が所定の状態になったことを示す電源電圧検出信号(N3)を出力する。パワーオンリセット回路(8E)は、前記電源電圧検出信号を入力し、所定のタイミングで前記内部回路の初期設定動作を指示し、前記内部回路の初期設定動作の完了に応答して、外部入出力バッファ回路(8F)を高インピーダンス状態から動作可能な状態にする。これにより、外部入出力バッファ回路が動作可能になるときは既に内部回路の初期設定が完了する。

(もっと読む)

1 - 3 / 3

[ Back to top ]