画像形成装置、情報処理装置および機能モジュール

【課題】動作可能になるまでの所要時間を短くした情報処理装置等を提供する。

【解決手段】機能モジュール20は、予め定められた機能を実行する実行部21、実行部21を初期状態に設定する初期化部22、実行部21を初期化するためのデータを保持する不揮発性メモリ23、オープンドレインバッファ24、インバータ25を備えている。初期化信号51(/RST)がアサートになると、実行部21は動作状態から停止状態に移行し、初期化部22は停止状態から動作状態に移行する。そして、初期化信号51(/RST)がネゲートになると、初期化部22は、不揮発性メモリ23に保持されていたデータを読み出し、実行部21を初期化する。実行部21の初期化が完了すると、実行部21は停止状態から動作状態に移行する。

【解決手段】機能モジュール20は、予め定められた機能を実行する実行部21、実行部21を初期状態に設定する初期化部22、実行部21を初期化するためのデータを保持する不揮発性メモリ23、オープンドレインバッファ24、インバータ25を備えている。初期化信号51(/RST)がアサートになると、実行部21は動作状態から停止状態に移行し、初期化部22は停止状態から動作状態に移行する。そして、初期化信号51(/RST)がネゲートになると、初期化部22は、不揮発性メモリ23に保持されていたデータを読み出し、実行部21を初期化する。実行部21の初期化が完了すると、実行部21は停止状態から動作状態に移行する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像形成装置、情報処理装置および機能モジュールに関する。

【背景技術】

【0002】

情報処理装置は、論理演算または算術演算を実行する中央演算処理装置(CPU)と、ASIC(特定用途向け集積回路、Application Specific Integrated Circuit)などで構成されCPUの制御により予め定められた機能を実行する機能モジュールとを含んで構成されている。

【0003】

特許文献1には、情報処理装置内にCPU等に用いるシステムリセットとは独立した系統で動作するコントローラを持ち、そのコントローラがROMとRAMの間のデータ転送をシステムリセット期間中に行う機能を有する装置が記載されている。

特許文献2には、電源投入時に演算処理装置の初期化を行うリセット部からの入力によって周辺制御部用に設けた専用制御バスの動作を開始し、該周辺制御部の初期化を行うことによって、制御プログラムによる周辺制御ASIC初期化に要する時間を削除し、システム復帰時間を短縮することによって低消費電力化を実現し、ユーザの利便性を向上させる画像形成装置が記載されている。

特許文献3には、内部レジスタが不揮発性である不揮発回路と、内部レジスタが揮発性である一以上の揮発回路と、初期化要求機構とを備えた情報処理装置であって、前記初期化要求機構は、前記揮発回路を駆動する電源がオフになったことを検知する一以上の電源検知部と、前記電源がオフになったことを記録する初期化要求レジスタと、を備え、前記電源検知部は、前記電源がオフになったことを検知した場合、前記電源がオフになったことを示す第1情報を前記初期化要求レジスタに記録し、前記初期化要求機構は、前記初期化要求レジスタに少なくとも一以上の前記第1情報が記録されている場合、前記揮発回路の初期化が必要であることを前記不揮発回路に通知し、前記不揮発回路は、前記初期化要求機構から前記通知を受信した場合、前記不揮発回路の内部レジスタに保持されているプロセスの実行状態に合わせて、前記揮発回路の内部レジスタを設定し、前記内部レジスタの設定後に、前記揮発回路を起動する情報処理装置が記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003−337746号公報

【特許文献2】特開2003−223089号公報

【特許文献3】特開2010−170206号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、機能モジュールを備える情報処理装置では、動作可能な状態に立ち上げるためには機能モジュールについても初期化(リセット)を行うことが必要である。そして、機能モジュールの初期化を速やかに行い、情報処理装置が動作可能になるまでの所要時間(立ち上がり時間)を短くすることが求められている。

本発明は、動作可能になるまでの所要時間を短くした情報処理装置等を提供することを目的とする。

【課題を解決するための手段】

【0006】

請求項1に記載の発明は、画像を記録材に形成する画像形成部と、算術演算および論理演算を行う演算モジュールと、当該演算モジュールの演算結果に基づいて予め定められた機能を実行する実行手段と、初期化信号を受信すると当該実行手段による機能の実行を停止する停止手段と、当該初期化信号が解除されると当該実行手段を初期化する初期化手段とを備える機能モジュールと、前記初期化信号を送信する初期化信号送信手段とを備え、前記画像形成部を制御する制御部とを備える画像形成装置である。

請求項2に記載の発明は、論理演算または算術演算を実行する演算モジュールと、前記演算モジュールの演算結果に基づいて予め定められた機能を実行する実行手段と、初期化信号を受信すると当該実行手段による機能の実行を停止する停止手段と、当該初期化信号が解除されると当該実行手段を初期化する初期化手段とを備える機能モジュールと、前記初期化信号を送信する初期化信号送信手段とを備える情報処理装置である。

請求項3に記載の発明は、前記機能モジュールが、前記実行手段を初期化するためのデータを保持する記憶手段をさらに備えることを特徴とする請求項2に記載の情報処理装置である。

請求項4に記載の発明は、前記記憶手段が、MRAM、FeRAM、PRAM、ReRAM等の読み書き可能な不揮発性メモリであることを特徴とする請求項3に記載の情報処理装置である。

請求項5に記載の発明は、前記機能モジュールと前記演算モジュールとを接続するように設けられ、当該機能モジュールにおける前記実行手段の初期化が完了したことを当該演算モジュールに通報する通報信号線をさらに備えることを特徴とする請求項2ないし4のいずれか1項に記載の情報処理装置である。

請求項6に記載の発明は、前記機能モジュールの前記実行手段および前記演算モジュールは、当該機能モジュールが前記初期化信号を受信すると動作状態から停止状態に移行し、当該機能モジュールにおける当該実行手段の初期化が完了したことを前記通報信号線により通報されると停止状態から動作状態に移行することを特徴とする請求項5に記載の情報処理装置である。

請求項7に記載の発明は、前記実行手段が初期化によって設定される初期状態は、当該実行手段が初めて動作可能になったときの状態または当該実行手段の実行を再開するために実行が中断したときの状態であることを特徴とする請求項2ないし6のいずれか1項に記載の情報処理装置である。

請求項8に記載の発明は、前記演算モジュールが、命令を実行する命令実行手段と、前記初期化信号を受信すると当該命令実行手段を初期化する他の初期化手段とをさらに備え、前記演算モジュールと前記機能モジュールとを接続するように設けられ、当該演算モジュールにおける前記命令実行手段の初期化が完了し、且つ当該機能モジュールの前記実行手段の初期化が完了したとき、当該演算モジュールおよび当該機能モジュールの動作を許可する許可信号線をさらに備えることを特徴とする請求項2に記載の情報処理装置である。

請求項9に記載の発明は、予め定められた機能を実行する実行手段と、初期化信号を受信すると前記実行手段の動作を停止する停止手段と、前記初期化信号が解除されると前記実行手段を初期化する初期化手段とを備える機能モジュールである。

請求項10に記載の発明は、前記実行手段を初期化するためのデータを保持する記憶手段をさらに備えることを特徴とする請求項9に記載の機能モジュールである。

請求項11に記載の発明は、前記記憶手段が、MRAM、FeRAM、PRAM、ReRAM等の読み書き可能な不揮発性メモリであることを特徴とする請求項10に記載の機能モジュールである。

【発明の効果】

【0007】

請求項1の発明によれば、本構成を備えない場合に比べ、画像形成装置の立ち上げにかかる所要時間を短くできる。

請求項2の発明によれば、初期化手段を備えない場合に比べ、情報処理装置が動作可能になるまでの所要時間を短くできる。

請求項3、4の発明によれば、本構成を備えない場合に比べ、情報処理装置が動作可能になるまでの所要時間をさらに短くできる。

請求項5の発明によれば、本構成を備えない場合に比べ、情報処理装置の立ち上げにおける待ち時間を抑制できる。

請求項6の発明によれば、本構成を備えない場合に比べ、不安定な動作を抑制できる。

請求項7の発明によれば、本構成を備えない場合に比べ、動作を再開させる状態が選択できる。

請求項8の発明によれば、本構成を備えない場合に比べ、CPUと機能モジュールとを並行して初期化できる。

請求項9の発明によれば、本構成を備えない場合に比べ、機能モジュールが安定な状態で初期化できる。

請求項10、11の発明によれば、本構成を備えない場合に比べ、機能モジュールの初期化の所要時間を短くできる。

【図面の簡単な説明】

【0008】

【図1】第1の実施の形態が適用される情報処理装置の全体構成の一例を示した図である。

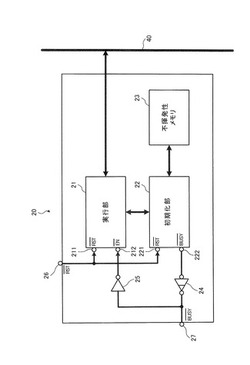

【図2】機能モジュールの構成の一例を示した図である。

【図3】機能モジュールの動作を説明するフローチャートである。

【図4】第1の実施の形態における情報処理装置の動作を説明するタイミングチャートである。

【図5】第2の実施の形態が適用される情報処理装置の全体構成の一例を示した図である。

【図6】第2の実施の形態が適用される情報処理装置の動作を説明するタイミングチャートである。

【図7】画像形成装置の構成の一例を示す図である。

【図8】画像形成装置と通信回線に接続された機器との関係を説明した図である。

【図9】第3の実施の形態が適用される情報処理装置の全体構成の一例を示した図である。

【図10】第3の実施の形態における機能モジュールの構成の一例を示した図である。

【図11】第4の実施の形態が適用される情報処理装置の全体構成の一例を示した図である。

【図12】第4の実施の形態におけるCPUの構成の一例を示した図である。

【図13】第4の実施の形態における情報処理装置の動作を説明するタイミングチャートである。

【図14】第5の実施の形態が適用される情報処理装置の全体構成の一例を示した図である。

【図15】第5の実施の形態における情報処理装置の動作を説明するタイミングチャートである。

【発明を実施するための形態】

【0009】

以下、添付図面を参照して、本発明の実施の形態について詳細に説明する。

[第1の実施の形態]

(情報処理装置1)

図1は、第1の実施の形態が適用される情報処理装置1の全体構成の一例を示した図である。

情報処理装置1は、論理演算および算術演算を行うALU(Alithmetic Logical Unit:論理算術演算ユニット)などを備えた演算モジュールの一例としての中央演算処理装置(以下ではCPUと表記する。)10、CPU10の演算結果に基づいて、予め定められた機能を実行する機能モジュール20、読み書き可能なメインメモリ30、データ、アドレス、命令(コマンド)などを転送するバス40、機能モジュール20を初期化する指示である初期化信号(/RST)を送信する初期化信号送信手段の一例としての初期化信号送信ユニット50を備えている。

【0010】

そして、初期化信号送信ユニット50は、初期化信号51(/RST)を送信する初期化信号送信端子51(/RST)を備えている。また、機能モジュール20は、初期化信号51(/RST)を受信する初期化信号受信端子26(/RST)およびビジー信号27(/BUSY)を発信するビジー信号送信端子27(/BUSY)を備えている。さらに、CPU10は、初期化信号11(/RST)を受信する初期化信号受信端子11(/RST)を備えている。

なお、「/RST」などの「/」は、そのあとに続く記号(アルファベットなど)の上にあるもの(アッパーバー)とし、記号(アルファベットなど)で示される信号が負論理であることを示す。また、端子(例えば、初期化信号送信端子51(/RST))とその端子に送受信される信号(例えば、初期化信号51(/RST))とを区別しないで同じ番号で表記する。

【0011】

機能モジュール20の例については、情報処理装置1を制御部とする装置の一例としての画像形成装置100(後述する図7)において説明する。

【0012】

次に、情報処理装置1における接続関係を説明する。

CPU10、機能モジュール20、メインメモリ30は、データ、アドレス、命令などを双方向に送受信可能なように、バス40に接続されている。すなわち、CPU10、機能モジュール20、メインメモリ30は、バス40に並列に接続され、バス40を介してデータ、アドレス、命令などを相互に送受信可能になっている。

【0013】

初期化信号送信ユニット50の初期化信号送信端子51(/RST)は、機能モジュール20の初期化信号受信端子26(/RST)に初期化信号線41を介して接続されている。つまり、初期化信号送信ユニット50が初期化信号送信端子51(/RST)から送信した初期化信号51(/RST)は、機能モジュール20の初期化信号受信端子26(/RST)によって受信される。

機能モジュール20のビジー信号送信端子27(/BUSY)とCPU10の初期化信号受信端子11(/RST)とは、通報信号線の一例としてのビジー信号線42で接続されている。つまり、機能モジュール20がビジー信号送信端子27(/BUSY)から送信したビジー信号(/BUSY)は、CPU10の初期化信号受信端子11(/RST)に初期化信号11(/RST)として受信される。また、ビジー信号線42は、電流制限抵抗Rを介して、電源電位Vddに接続されている。

なお、図1では、上記の信号の流れを矢印で示している。

【0014】

(機能モジュール20)

次に、機能モジュール20の構成を説明する。

図2は、機能モジュール20の構成の一例を示した図である。

機能モジュール20は、予め定められた機能を実行する実行手段の一例としての実行部21、実行部21を初期状態に設定する初期化手段の一例としての初期化部22、実行部21を初期状態に設定するためのデータを保持する記憶手段の一例としての不揮発性メモリ23を備えている。さらに、機能モジュール20は、オープンドレインバッファ24とインバータ25とを備えている。なお、実行部21は実行を停止する停止手段の一例でもある。

【0015】

実行部21、初期化部22は、シーケンサ、カウンタ、レジスタなどを含む論理回路から構成されている。実行部21は、初期化信号受信端子211(/RST)およびイネーブル信号受信端子212(/EN)を備えている。初期化部22は、初期化信号受信端子221(/RST)およびビジー信号送信端子222(/BUSY)を備えている。

不揮発性メモリ23は、“1”/“0”で表されたデータを記憶する機能を有している。そして、「不揮発性」とは、電力が供給されている間はもとより電力の供給がない場合であっても、データを保持することをいう。

なお、機能モジュール20の実行部21、初期化部22はレジスタなどを有し、電力が供給されているときはデータを保持するが、電力が供給されていないときはデータが失われる揮発性である。CPU10およびメインメモリ30も揮発性であるとする。

【0016】

そして、オープンドレインバッファ24は、入力信号が“0”(ここでは、後述する「L」に対応する。)の時には“0”(「L」)を出力し、入力信号が“1”(ここでは、後述する「H」に対応する。)の時にはハイ・インピーダンス(高抵抗)状態(「Hi−Z」と表記する。)になる。

一方、インバータ25は、入力信号と極性が反転した信号を出力する。

【0017】

機能モジュール20(実行部21、初期化部22、不揮発性メモリ23、オープンドレインバッファ24、インバータ25)は、シリコン等で構成された1つの半導体チップ(例えば、ASIC(特定用途向け集積回路、Application Specific Integrated Circuit))として構成されてもよい。また、実行部21、初期化部22、不揮発性メモリ23、オープンドレインバッファ24、インバータ25を組み合わせて構成した複数の半導体チップであってもよい。また、実行部21、初期化部22または不揮発性メモリ23が、分割されて構成されてもよい。

【0018】

機能モジュール20における接続関係を説明する。

機能モジュール20の実行部21と初期化部22とは、データ、アドレス、命令などを双方向に転送可能に接続されている。同様に、初期化部22と不揮発性メモリ23とは、データ、アドレス、命令などを双方向に転送可能に接続されている。

【0019】

そして、機能モジュール20の初期化信号受信端子26(/RST)は、実行部21の初期化信号受信端子211(/RST)と初期化部22の初期化信号受信端子221(/RST)とに並列に接続されている。つまり、初期化信号送信ユニット50から送信された初期化信号51(/RST)は、実行部21と初期化部22に並列に送信される。

一方、初期化部22のビジー信号送信端子222(/BUSY)は、オープンドレインバッファ24を介して、機能モジュール20のビジー信号送信端子27(/BUSY)に接続されている。すなわち、ビジー信号222(/BUSY)が“0”(「L」)のときは、ビジー信号27(/BUSY)も“0”(「L」)になる。しかし、ビジー信号222(/BUSY)が“1”(「H」)のときは、オープンドレインバッファ24の出力端子は「Hi−Z」になるので、ビジー信号27(/BUSY)はビジー信号線42の状態により設定される。

また、オープンドレインバッファ24の出力端子は、インバータ25を介して実行部21に設けられたイネーブル信号受信端子212(/EN)に接続されている。つまり、初期化部22から発信されたビジー信号222(/BUSY)が“0”(「L」)のときは、イネーブル信号212(/EN)は“1”(「H」)になり、初期化部22から発信されたビジー信号222(/BUSY)が“1”(「H」)のときは、イネーブル信号212(/EN)はビジー信号線42の状態により設定される。

なお、機能モジュール20では、実行部21がバス40と接続されている。

【0020】

情報処理装置1の機能モジュール20は、実行部21を初期状態に設定する初期化部22を備えている。すなわち、機能モジュール20は、CPU10による制御によらず、初期状態に設定できる機能を有している。

ここで、初期状態とは、実行部21が初めて動作可能になったときの状態(リセット後の状態)であってもよく、実行部21の実行が中断されたとき、動作を再開したい状態であってもよい。実行が中断されたときの例としては、情報処理装置1がオフになる直前の実行部21の状態が上げられる。

そして、機能モジュール20は、初期化信号送信ユニット50からの初期化信号51(/RST)を受信する(後述するようにネゲートからアサートになる)と、実行部21は動作状態から停止状態に移行し、初期化部22は実行部21を初期状態に設定するための処理を開始可能な状態に移行する。そして、初期化信号51(/RST)が解除される(アサートからネゲートに移行する)と、初期化部22は実行部21を初期状態に設定するための処理(初期化)を実行するようになっている。

【0021】

すなわち、初期化信号51(/RST)がアサートであるとき、機能モジュール20の実行部21は動作を停止している。

これは、電源が投入されて規定の電圧に上昇し切らない間に機能モジュール20が動作を開始することを抑制するためである。また、電源投入後に安定な動作状態になるまで暫く待たなければならない部品(例えば、水晶発振器)がある場合には、安定な動作状態になるまで待つためである。これにより、機能モジュール20の不安定な動作が抑制される。

CPU10でも同様である。

【0022】

また、初期化信号51(/RST)がアサートからネゲートになったときに行われる初期化は、機能モジュール20の実行部21を動作可能な状態にすることをいい、例えば、フリップフロップを予め定められた状態にセット(プリセット)すること、レジスタに予め定められたデータをセットするなどの処理が含まれる。また、位相同期回路(PLL、Phase Locked Loop)が含まれる場合には、PLLは電源の投入時に停止状態にあるので、停止状態を解除し、発振が安定(PLLロック)したらクロックドライバの出力をイネーブルにする。このように、初期化には、手順を踏んで動作可能な状態にする処理も含まれる。

【0023】

なお、初期化信号(/RST)がアサートであるとは、信号の極性によらず初期化信号(/RST)が有効な状態(アクティブ)にあることをいう。一方、初期化信号(/RST)が無効な状態(インアクティブ)にあることをネゲート(無効)という。他の信号においても同様で、信号の極性を問わないで、信号が有効であるときがアサート、信号が無効であるときがネゲートである。

ここでは、一例として電圧レベルが高い状態(「H」)をネゲートとし、低い状態(「L」)をアサートとする負論理で示す。また、“0”がアサートに対応し、“1”がネゲートに対応する。そして、電源電位Vddは「H」に対応する。

【0024】

次に、ビジー信号(/BUSY)およびイネーブル信号(/EN)について説明する。

ビジー信号(/BUSY)がアサートであるとは、ビジー信号(/BUSY)を送信する回路(初期化部22など)が他の回路(実行部21など)に、新たな動作の準備が整っていないことを示す。例えば、初期化部22からのビジー信号222(/BUSY)がアサートであると、初期化部22が実行部21への初期化を実行中で、初期化が完了していないことを示す。そして、ビジー信号222(/BUSY)がネゲートになると、初期化部22は実行部21の初期化を完了し、実行部21への新たな実行指示が受付可能な状態にあることを示す。

さらに、イネーブル信号(/EN)がアサートであるとは、イネーブル信号(/EN)を受信した回路が動作することを許可され、動作状態(イネーブル)になることを示す。例えば、実行部21が受信するイネーブル信号212(/EN)がアサートであると、実行部21は動作状態(イネーブル)にある。そして、イネーブル信号212(/EN)がネゲートであると、実行部21は停止状態(ディセーブル)になる。

【0025】

初期化部22がシーケンサなどのハードウエアで構成され、機能モジュール20の実行部21を初期状態に設定する初期化をハードウエア制御で行うと、初期化に要する時間が短くなる(所要時間が短い)。しかし、機能モジュール20の初期化をソフトウエアによる制御(ソフトウエア制御)で行ってもよい。

【0026】

(機能モジュール20の動作)

次に、機能モジュール20の動作を説明する。

図3は、機能モジュール20の動作を説明するフローチャートである。

ここでは、初期化信号送信ユニット50からの初期化信号51(/RST)がアサートになってからの機能モジュール20の動作を説明する。すなわち、“Reset”からの動作を説明する。

【0027】

以下、図1、2を参照しつつ、図3のフローチャートを説明する。

初期化信号51(/RST)がアサートになると、図1に示すように、機能モジュール20の初期化信号26(/RST)がアサートになる。そして、図2に示すように、機能モジュール20の実行部21の初期化信号211(/RST)および初期化部22の初期化信号221(/RST)がアサートになる。

すると、実行部21は動作状態から停止状態に移行し、初期化部22は実行部21を初期状態に設定するための処理を開始可能な状態に移行する(ステップ101)。

このとき、初期化部22のビジー信号222(/BUSY)がアサートになると、前述したように、イネーブル信号212(/EN)がネゲートになる。

【0028】

そして、初期化信号51(/RST)が解除される(アサートからネゲートに移行する)のを待つ(ステップ102)。

なお、初期化信号51(/RST)がアサートである期間は予め定められている。すなわち、前述したように、電源が投入されて規定の電圧に上昇しきらない間に機能モジュール20が動作を開始することを抑制したり、水晶発振器などが電源投入後に安定な動作状態になるまで待ったりするためである。

【0029】

次に、初期化信号51(/RST)が解除される(アサートからネゲートに移行する)と、初期化部22は実行部21を初期状態に設定するための処理(初期化)を実行する(ステップ103)。

そして、実行部21の初期化が終了するのを待つ(ステップ104)。

【0030】

実行部21の初期化が終了すると、初期化部22が動作を停止し、ビジー信号222(/BUSY)がアサートからネゲートに移行する。

すると、オープンドレインバッファ24の出力端子が「Hi−Z」になる。このとき、図1で示したように、ビジー信号線42は、電流制限抵抗Rを介して、電源電位Vddに接続されているので、ビジー信号27(/BUSY)はアサートからネゲートに移行する。よって、イネーブル信号212(/EN)はネゲートからアサートに移行する(ステップ105)。

【0031】

初期化信号送信ユニット50からの初期化信号51(/RST)がネゲートである間は、実行部21は実行を継続する。しかし、初期化信号51(/RST)がネゲートからアサートになると、ステップ101に戻る(ステップ106)。

【0032】

図4は、第1の実施の形態における情報処理装置1の動作を説明するタイミングチャートである。図4では、初期化信号51(/RST)、ビジー信号線42(図4の説明では/BUSYを付記する。)、機能モジュール20のイネーブル信号212(/EN)の出力レベル、機能モジュール20の実行部21およびCPU10の状態を示している。なお、初期化信号51(/RST)、ビジー信号線42(/BUSY)、イネーブル信号212(/EN)については、アサートの状態を「アサート」と表記した。表記していない部分は「ネゲート」である。

また、時刻t1から時刻t4へと時間が経過するとする。なお、時刻t3は後述する図6、13、15との整合を図るために設けている。

【0033】

以下、図1、2、3を参照しつつ、図4のタイミングチャートを説明する。

時刻t1において、初期化信号送信ユニット50からの初期化信号51(/RST)がネゲートからアサートになる(「H」から「L」になる)とする。

初めに、時刻t1の直前の状態を説明する。時刻t1の直前では、CPU10および機能モジュール20の実行部21は動作状態にあるとする。

この状態を説明する。時刻t1の直前では、初期化信号51(/RST)はネゲート(「H」)である。前述したように、初期化部22のビジー信号222(/BUSY)はネゲート(「H」)であるので、機能モジュール20のオープンドレインバッファ24の出力端子は「Hi−Z」となる。よって、機能モジュール20のビジー信号27(/BUSY)は「Hi−Z」である。しかし、ビジー信号線42(/BUSY)は、電流制限抵抗Rを介して、電源電位Vddに接続されている。これにより、イネーブル信号212(/EN)はアサート(「L」)になる。すなわち、機能モジュール20の実行部21は動作状態にある。

また、ビジー信号線42(/BUSY)は「H」であるので、CPU10の初期化信号11(/RST)もネゲートである。よって、CPU10も動作状態である。

【0034】

時刻t1において、初期化信号51(/RST)がネゲートからアサート(「H」から「L」)に移行すると、初期化部22のビジー信号222(/BUSY)がアサートになる(「H」から「L」になる)(図3のステップ101)。すると、オープンドレインバッファ24の出力端子が「L」になって、機能モジュール20のビジー信号27(/BUSY)が「Hi−Z」から「L」に移行する。すると、ビジー信号線42(/BUSY)が「H」から「L」に移行する。これにより、イネーブル信号212(/EN)がアサートからネゲートに移行する(「L」から「H」になる)。よって、機能モジュール20の実行部21は停止状態になる。

【0035】

ビジー信号線42(/BUSY)はCPU10の初期化信号受信端子11(/RST)に接続されている。ビジー信号線42(/BUSY)が「H」から「L」に移行すると、CPU10の初期化信号11(/RST)がネゲートからアサートに移行し、CPU10が動作状態から停止状態に移行する。

【0036】

次に、時刻t2において初期化信号51(/RST)がネゲート(「L」から「H」)になると、初期化部22による実行部21の初期化が開始される(ステップ103)。

そして、時刻t4で初期化部22による実行部21の初期化が完了すると、初期化部22の送信するビジー信号27(/BUSY)が「L」から「Hi−Z」に移行する。これにより、ビジー信号線42(/BUSY)が「L」から「H」に移行し、イネーブル信号212(/EN)がネゲートからアサート(「H」から「L」)に移行する(ステップ105)。そして、実行部21が停止状態から動作状態に移行する。

【0037】

さらに、ビジー信号線42が「L」から「H」に移行することで、CPU10の初期化信号11(/RST)もアサートからネゲートになる。これにより、CPU10の実行が許可され、動作状態になる。すなわち、情報処理装置1が動作可能な状態になる。

【0038】

ここで、不揮発性メモリ23について説明する。

不揮発性メモリ23は、実行部21が初めて動作可能になったときの状態(リセット後の状態)に設定するデータを保持してもよく、実行部21の実行が中断されたときの状態であって、その状態から動作を再開したい状態のデータを保持してもよい。例えば、不揮発性メモリ23は、情報処理装置1のオフになる直前における実行部21の状態のデータ(レジスタおよびカウンタなどのデータ、シーケンサ、フリップフロップなどの状態に関するデータ)を保持する。

初期化部22が、実行部21が初めて動作可能になったときの状態(リセット後の状態)に設定するデータを読み出して、実行部21を初期化する場合には、機能モジュール20(実行部21)は初めて動作可能になったときの状態(リセット後の状態)で動作可能になる。

一方、初期化部22が、情報処理装置1のオフになる直前における実行部21の状態のデータを読み出して、実行部21を初期化する場合には、機能モジュール20(実行部21)は情報処理装置1がオフになる直前の状態(実行が中断したときの状態)から動作が可能になる(実行を再開する)。

【0039】

なお、機能モジュール20を初期化状態に設定するデータの場合には、データは読み出せればよく、不揮発性メモリ23はROM(リードオンリーメモリ)で構成されていてもよい。

一方、機能モジュール20をオフになる直前の状態から再開させるには、不揮発性メモリ23は、オフになる直前の実行部21の状態を示すデータを保持(退避)し、オフになっても保持し続けていることが必要となる。よって、不揮発性メモリ23は、読み書き可能な「不揮発性」のメモリであることが必要となる。

ここで、「不揮発性」とは、電力の供給がある場合に加え、電力の供給がなくなった場合においても、情報(“1”/“0”)を保持する(保持し続ける)記憶機能をいう。

【0040】

そして、オフになる直前の実行部21の状態を示すデータの書き込み(退避)は、オフになる直前に行ってもよく、実行部21の状態が変化するタイミング毎に行ってもよい。実行部21の状態が変化するタイミング毎に行う場合には、オフにする直前に書き込みを行わないで、情報処理装置1をオフにしてよい。

しかし、実行部21の状態が変化するタイミング毎に行う場合には、読み書き可能な不揮発性メモリ23は、高速に読み書きできる不揮発性記憶素子を用いることが好ましい。これにより、書き込み時間による機能モジュール20や情報処理装置1の処理速度の低下が抑制される。

【0041】

高速に読み書きできる不揮発性記憶素子としては、磁気メモリ(magnetoresistive RAM:MRAMと表示する。)、強誘電体メモリ(ferroelectric RAM:FeRAMと表記する。)、相変化メモリ(phase change RAM:PRAMと表記する。)、抵抗メモリ(resistance RAM:ReRAMと表記する。)等がある。

MRAMは、2枚の磁性積層膜をトンネル磁気抵抗膜で挟み、重ねた磁性積層膜の磁化のなす相対角度によりトンネル磁気抵抗膜の抵抗が変化する磁気抵抗(magnetoresistive:MR)効果を用いて情報(“1”/“0”)を保持する。FeRAMは、PZT(Pb(Zr、Ti)O3)などの強誘電体の分極を用いて情報(“1”/“0”)を保持する。PRAMは、カルコゲナイドの相変化にともなう抵抗変化により情報(“1”/“0”)を保持する。ReRAMは、電圧の印加による電気抵抗の大きな変化(CER(colossal electro−resistance)効果)を利用し、抵抗変化により情報(“1”/“0”)を保持する。

【0042】

これらの不揮発性記憶素子(MRAM、FeRAM、PRAM、ReRAM)は、DRAM、SRAMと同様に半導体基板上にセルをマトリクス状に高密度に配置でき、一体形成された駆動回路により高速な読み書きができる。さらに、書き換え回数の制限が原理的にない、または書き換え可能な回数が極めて大きい(以下では、書き換え回数の制限が小さいと表記する)。

このため、これらの不揮発性記憶素子(MRAM、FeRAM、PRAM、ReRAM等)は、不揮発性メモリ23に適用しやすい。

【0043】

なお、不揮発性記憶素子には、MOSトランジスタのゲート電極(フローティングゲート)に蓄積した電荷の有無により情報(“1”/“0”)を保持するフラッシュメモリ、EEPROM(Electrically Erasable Programmable ROM)などもある。フラッシュメモリおよびEEPROMは、電気的に状態(“1”/“0”)の読み書きができるが、前述の不揮発性記憶素子(MRAM、FeRAM、PRAM、ReRAM等)に比べ、読み書きの速度、特に書き込みの速度が遅い。そして、フラッシュメモリ、EEPROMは、書き換え回数に制限がある。

これらのフラッシュメモリおよびEEPROMを、不揮発性メモリ23に適用してもよい。

【0044】

また、不揮発性メモリ23の代わりに、DRAM、SRAMなどの揮発性メモリを使用してもよい。揮発性メモリを使用する場合には、初期化の前に初期化に必要なデータを情報処理装置1のメインメモリ30から読み出して、書き込めばよい。

【0045】

以上説明したように、第1の実施の形態の情報処理装置1では、初期化信号送信ユニット50から送信された初期化信号51(/RST)がアサートになると、機能モジュール20が動作を停止(動作状態から停止状態へ移行)し、それに伴いCPU10も動作を停止(動作状態から停止状態へ移行)する。そして、機能モジュール20が、初期状態に初期化されると、CPU10が動作状態になる。これにより、CPU10、機能モジュール20を含む情報処理装置1が立ち上がる(停止状態から動作状態になる)。

そして、機能モジュール20のビジー信号27(/BUSY)をCPU10の初期化信号11(/RST)としているので、機能モジュール20の初期化が終わり、ビジー信号27(/BUSY)がネゲートになると、CPU10が動作状態になる。これにより、機能モジュール20の初期化の終了とCPU10の動作開始との間に不要な待ち時間(オーバヘッド)が発生することが抑制される。すなわち、情報処理装置1は、初期化信号51(/RST)がアサートになってから動作可能になるまでの立ち上げに要する時間が短い。

また、機能モジュール20は初期化部22を備えているので、機能モジュール20の初期化にCPU10の制御を必要としない。そして、機能モジュール20の初期化部22による実行部21の初期化をハードウエア制御で行うと、ソフトウエアを用いたソフトウエア制御で行う場合に比べ、機能モジュール20の初期化に要する所要時間をさらに短くすることができる。

【0046】

なお、初期化信号送信ユニット50からの初期化信号51(/RST)の送信は、情報処理装置1がオンになった(電源が投入された)ときに、送信されるようにするのが好ましい。このとき、初期状態への設定またはオフになる直前の状態からの再開のいずれかを選択できるようにしてもよい。

また、ボタン等が押されることで、初期化信号送信ユニット50から初期化信号51(/RST)が送信されてもよい。このときも、初期状態への設定またはボタン等が押される直前の状態からの再開のいずれかを選択できるようにしてもよい。

【0047】

[第2の実施の形態]

第1の実施の形態の情報処理装置1は、機能モジュール20を1つ備えていた。第2の実施の形態の情報処理装置1は、複数の機能モジュール20−1〜20−n(nは整数)を備えている。

【0048】

(情報処理装置1)

図5は、第2の実施の形態が適用される情報処理装置1の全体構成の一例を示した図である。

情報処理装置1は、CPU10、機能モジュール20−1〜20−n、メインメモリ30、バス40、初期化信号送信ユニット50を備えている。

なお、機能モジュール20−1〜20−nをそれぞれ区別しないときは、機能モジュール20と表記する。

【0049】

機能モジュール20−1〜20−nは、バス40にデータ、アドレス、命令などを双方向に送受信可能に並列に接続されている。

また、初期化信号送信ユニット50の初期化信号送信端子51(/RST)は、初期化信号線41を介して、機能モジュール20−1〜20−nのそれぞれの初期化信号受信端子26(/RST)に並列に接続されている。

そして、機能モジュール20−1〜20−nのそれぞれのビジー信号送信端子27(/BUSY)は、ビジー信号線42に並列に接続されている。そして、ビジー信号線42の一端は、CPU10の初期化信号受信端子11(/RST)に接続されている。また、ビジー信号線42の他端は、電流制限抵抗Rを介して、電源電位Vddに接続されている。

【0050】

第2の実施の形態の機能モジュール20−1〜20−nは、図2に示した第1の実施の形態の機能モジュール20と同様の構成を有し、図3のフローチャートで示したのと同様に動作する。よって、機能モジュール20−1〜20−nについての説明を省略する。

【0051】

次に、第2の実施の形態が適用される情報処理装置1の動作を説明する。

図6は、第2の実施の形態が適用される情報処理装置1の動作を説明するタイミングチャートである。ここでは、第1の実施の形態の図4と同様に、時刻t1において初期化信号送信ユニット50が初期化信号51(/RST)をネゲートからアサートにする場合について説明する。

図6では、初期化信号51(/RST)、ビジー信号線42(図6の説明では/BUSYを付記する。)の出力レベル、機能モジュール20−1〜20−nのそれぞれの実行部21の状態およびビジー信号27(/BUSY)の出力レベル、CPU10の状態を示している。

なお、時刻t1から時刻t4へと時間が経過するとする。この時刻t1〜時刻t4は図4と同じである。

【0052】

時刻t1の直前の状態は、第1の実施の形態と同様に、CPU10および機能モジュール20−1〜20−nの実行部21は動作状態にある。一方、機能モジュール20−1〜20−nのそれぞれの初期化部22は停止状態にある。

初期化信号送信ユニット50から機能モジュール20−1〜20−nのそれぞれの初期化信号受信端子26(/RST)に送信される初期化信号51(/RST)はネゲート(「H」)である。このとき、機能モジュール20−1〜20−nの初期化部22のビジー信号222(/BUSY)は「H」である。よって、オープンドレインバッファ24の出力端子は「Hi−Z」である。これにより、機能モジュール20−1〜20−nのそれぞれのビジー信号27(/BUSY)はともに「Hi−Z」である。しかし、ビジー信号線42(/BUSY)は、電流制限抵抗Rを介して電源電位Vddに接続されているので、ネゲートであり、機能モジュール20−1〜20−nのそれぞれのイネーブル信号212(/EN)はアサートである。

そして、ビジー信号線42(/BUSY)の一端が接続されたCPU10の初期化信号11(/RST)も「H」(ネゲート)になっている。また、機能モジュール20の実行部21のイネーブル信号212(/EN)は「L」(アサート)になっている。

すなわち、時刻t1の直前においては、CPU10、および機能モジュール20−1〜20−nのそれぞれの実行部21は動作状態にある。そして、機能モジュール20−1〜20−nの初期化部22は停止状態にある。

【0053】

さて、時刻t1で、初期化信号送信ユニット50からの初期化信号51(/RST)がネゲートからアサートになる(「H」から「L」になる)と、機能モジュール20−1〜20−nの実行部21が動作状態から停止状態に移行する。

そして、機能モジュール20−1〜20−nのそれぞれのビジー信号27(/BUSY)が「Hi−Z」から「L」に移行する。これにより、ビジー信号線42(/BUSY)が「H」から「L」に移行する。

そして、CPU10の初期化信号11(/RST)が「H」から「L」に移行して、ネゲートからアサートになり、CPU10が動作状態から停止状態に移行する。

【0054】

次に、時刻t2において初期化信号51(/RST)がアサートからネゲート(「L」から「H」)になると、それぞれの機能モジュール20−1〜20−nにおいて初期化部22による実行部21の初期化が並行して開始される。

そして、時刻t3で、最も初期化の所要時間が短い機能モジュール20−1の初期化が完了する。すると、図2において説明したように、機能モジュール20−1の初期化部22のビジー信号222(/BUSY)がネゲート(「H」)になる。これにより、機能モジュール20−1のオープンドレインバッファ24の出力端子が「L」から「Hi−Z」になって、ビジー信号27(/BUSY)は「Hi−Z」になる。しかし、他の機能モジュール20−2〜20−nは初期化が完了していないため、機能モジュール20−2〜20−nのビジー信号27(/BUSY)は「L」である。このため、ビジー信号線42(/BUSY)が「L」に維持され、機能モジュール20−1のビジー信号27(/BUSY)は「H」になることができず「L」を維持する。すると、機能モジュール20−1のイネーブル信号212(/EN)も「H」でネゲートを維持する。

つまり、機能モジュール20−1の実行部21は、時刻t3で初期化が完了するが、時刻t3から後述する時刻t4までの間は停止状態にある。

【0055】

ビジー信号線42(/BUSY)は、機能モジュール20−1〜20−nのうち1つでも初期化状態であると「L」に設定されるようになっている。すなわち、機能モジュール20−1〜20−nが1つでも初期化状態にあると、「L」を出力するビジー信号送信端子27(/BUSY)がビジー信号線42を「L」に引き込むようになっている。

【0056】

時刻t3において、他の機能モジュール20−2〜20−nは、初期化を継続している。そして、CPU10は停止状態を継続する。

【0057】

そして、時刻t4で、最も初期化の所要時間が長い機能モジュール20−2の初期化が完了する。すると、機能モジュール20−2の機能モジュール20−2のビジー信号27(/BUSY)が「Hi−Z」になる。これまで、機能モジュール20−2のビジー信号27(/BUSY)が「L」であることで、ビジー信号線42(/BUSY)を「L」に引き込んでいた。しかし、機能モジュール20−2の初期化の完了とともに「L」に引き込まなくなり、ビジー信号線42(/BUSY)が「L」から「H」に移行する。これにより、すべての機能モジュール20−1〜20−nのビジー信号27(/RST)が「Hi−Z」に移行し、ビジー信号線42(/BUSY)が「L」から「H」に移行する。そして、すべての機能モジュール20−1〜20−nのイネーブル信号212(/EN)がネゲートからアサートに移行して、すべての機能モジュール20−1〜20−nが動作状態になる。

【0058】

また、時刻t4において、ビジー信号線42(/BUSY)が「L」から「H」に移行すると、CPU10の初期化信号11(/RST)が「L」から「H」に移行し、アサートからネゲートになる。そして、CPU10が停止状態から動作状態に移行する。

これにより、情報処理装置1が動作可能な状態になる。

【0059】

以上説明したように、複数の機能モジュール20−1〜20−nを備える第2の実施の形態の情報処理装置1では、初期化信号送信ユニット50からの初期化信号51(/RST)がアサートになる(図6の時刻t1)と、CPU10および機能モジュール20−1〜20−nが並行して停止状態になり、初期化信号51(/RST)がネゲートになる(時刻t2)と、機能モジュール20−1〜20−nの初期化が並行して開始される。そして、すべての機能モジュール20−1〜20−nの初期化が完了するタイミング(時刻t4)で、CPU10および機能モジュール20−1〜20−nが停止状態から動作状態に移行する。

【0060】

機能モジュール20−1〜20−nは、それぞれが実行部21、初期化部22、不揮発性メモリ23を備えているので、初期化信号受信端子26の初期化信号51(/RST)がネゲートからアサートになると、動作状態から停止状態に移行し、初期化信号51(/RST)がアサートからネゲートになるとそれぞれが個別に初期化を実行する。すなわち、機能モジュール20−1〜20−nの初期化は、CPU10の制御を必要とせず、並行して行われる。

一方、機能モジュール20−1〜20−nのそれぞれが初期化部22と実行部21を初期化するデータを保持する不揮発性メモリ23とを備えない場合には、機能モジュール20−1〜20−nのそれぞれの初期化は、ソフトウエア処理によりCPU10がシーケンシャル(順)に行うことになる。

すなわち、第2の実施の形態の情報処理装置1は、機能モジュール20−1〜20−nが初期化部22および不揮発性メモリ23を備えず、初期化をソフトウエア処理により順に行う情報処理装置1に比べ、初期化を短い時間で行うことができる。

【0061】

そして、第2の実施の形態の情報処理装置1では、ビジー信号線42(/BUSY)がネゲートになることにより、最も初期化の所要時間が長い機能モジュール20−x(1≦x≦nの整数)の初期化の完了とともに、CPU10が動作状態になる。このことにより、機能モジュール20−1〜20−nの初期化終了とCPU10の動作開始との間に不要な待ち時間(オーバヘッド)が生じることを抑制している。

一方、機能モジュール20−1〜20−nのそれぞれの初期化の終了をCPU10から問い合わせ(ポーリング)する場合には、機能モジュール20−xの初期化が終了してから、CPU10がポーリングを実行するまでの時間が不要な待ち時間(オーバヘッド)となってしまう。

すなわち、第2の実施の形態の情報処理装置1では、機能モジュール20−1〜20−nは並行して初期化が行われるとともに、機能モジュール20−1〜20−nの初期化の終了とともにCPU10が動作状態になる。よって、初期化信号51(/RST)がアサートになってから動作可能になるまでの立ち上がり時間が短い。

【0062】

なお、初期化信号51(/RST)および不揮発性メモリ23の保持するデータについては、第1の実施の形態で説明したのと同様であるので説明を省略する。

【0063】

(画像形成装置100)

次に、第2の実施の形態の情報処理装置1を画像形成装置100の制御部として構成する場合を説明する。

図7は、画像形成装置100の構成の一例を示す図である。

画像形成装置100は、制御部としての情報処理装置1と、ボタンなどユーザが指示を与えるためのUI(ユーザインターフェイス)部120、プリンタなどの画像形成部130、スキャナなどの画像読取部140、通信回線200(後述する図8参照)とデータなどの送受信を行う送受信部150を備えている。

【0064】

そして、制御部としての情報処理装置1は、4つの機能モジュール20−1〜20−4を備えている。機能モジュール20−1はUI部120を制御する機能を有するUI制御モジュール、機能モジュール20−2は画像形成部130を制御する機能を有する画像形成制御モジュール、機能モジュール20−3は画像読取部140を制御する機能を有する画像読取制御モジュール、機能モジュール20−4は送受信部150を制御する機能を有する送受信制御モジュールである。画像形成装置100の説明においては、機能モジュール20−1〜20−4を、それぞれUI制御モジュール20−1、画像形成制御モジュール20−2、画像読取制御モジュール20−3、送受信制御モジュール20−4と読み替える。

【0065】

UI部120はUI制御モジュール20−1に、画像形成部130は画像形成制御モジュール20−2に、画像読取部140は画像読取制御モジュール20−3に、送受信部150は送受信制御モジュール20−4に、それぞれデータ、命令などを送受信可能に接続されている。

【0066】

UI部120は、例えばボタンやタッチパネルなどで構成された入力機器であって、ユーザからの指示が入力される。そして、UI制御モジュール20−1は、UI部120に入力されたユーザの指示をCPU10に送信し、CPU10からの命令を受信し、UI部120がユーザの指示に対応した応答(入力画面などの切り替え)をするように制御する。

画像形成部130は、LEDなどにより感光体ドラムに潜像を書き込み、潜像をトナーで現像して紙などの記録材に転写する方式のプリンタでもよく、インクジェットなどで記録材に像を形成する方式のプリンタであってもよい。そして、画像形成制御モジュール20−2は、メインメモリ30内の画像データを画像形成部130に送信したり、画像形成部130から動作状態に関するデータを受信してCPU10に送信したりする。

画像読取部140は、画像が記録された記録材に対向させた受光素子アレイをスキャンさせる方式の画像読取機器であってもよく、CCDなどの撮像素子で画像を読み取る方式の撮像機器であってもよい。そして、画像読取制御モジュール20−3は、CPU10と画像読取部140との間にあって、CPU10から画像読取部140の読み取り条件などを設定するデータを受信して画像読取部140に送信したり、画像読取部140が読み取った画像データを受信してメインメモリ30に送信したりする。

送受信部150は、通信回線200を介してコンピュータ300またはファクシミリ装置400から送信された画像などのデータを受信する(後述する図8参照)。送受信制御モジュール20−4は、送受信部150が受信したデータをCPU10やメインメモリ30に送信する。また、送受信部150は、通信回線200に接続されたコンピュータ300またはファクシミリ装置400に、画像読取部140が読み取った画像などのデータを、送受信制御モジュール20−4を介して送信する。

【0067】

図8は、画像形成装置100と通信回線200に接続された機器との関係を説明した図である。

画像形成装置100は、送受信部150を介して、インターネット、電話網などの通信回線200に接続されている。そして、通信回線200には、コンピュータ300、ファクシミリ装置400、サーバ500などが接続されている。

【0068】

図7および図8を参照して、画像形成装置100の基本的な動作を説明する。

画像形成装置100は、画像読取部140から読み取った画像を、画像形成部130により記録材に印刷する。

また、画像形成装置100は、通信回線200を介して、画像形成装置100の外部に置かれたコンピュータ300、ファクシミリ装置400またはサーバ500から送信された画像などのデータを画像形成部130により記録材に印刷する。

一方、画像形成装置100は、画像読取部140が読み取った画像などのデータを、送受信部150から通信回線200を介して画像形成装置100の外部に置かれたコンピュータ300および/またはファクシミリ装置400に送信する。

【0069】

このような画像形成装置100は、使用されないときは通電されていないことが好ましい。例えば、電源からの電力の供給が全くない完全停止状態または節電のために一部の機能を停止させた待機(スリープ)状態に設定される。そして、使用しようとするときに、これらの完全停止状態または待機状態から、速やかに動作可能(動作状態)になることが望ましい。また、使用している間に、不具合が認められたとき、速やかに初期(リセット)状態に設定されることが望ましい。

このため、図7に示すように、第2の実施の形態における情報処理装置1を、画像形成装置100の制御部とすると、UI制御モジュール20−1、画像形成制御モジュール20−2、画像読取制御モジュール20−3、送受信制御モジュール20−4は、初期化信号51(/RST)を並行して受信し(アサートになり)、初期化信号51(/RST)が解除される(ネゲートになる)と並行して実行部21の初期化を実行するので、順に初期化がされる場合に比べ、初期化信号51(/RST)を受信してから(アサートになってから)短い時間で動作可能な状態になる。

【0070】

[第3の実施の形態]

第1の実施の形態および第2の実施の形態の情報処理装置1では、機能モジュール20(20−1〜20−n)が不揮発性メモリ23を備えていた。

第3の実施の形態では、機能モジュール20(20−1〜20−n)が不揮発性メモリ23を備えず、機能モジュール20(20−1〜20−n)の外部に不揮発性メモリ63を備えている。

【0071】

(情報処理装置1)

図9は、第3の実施の形態が適用される情報処理装置1の全体構成の一例を示した図である。

第3の実施の形態の情報処理装置1では、CPU10、機能モジュール60−1〜60−n、メインメモリ30、不揮発性メモリ63および初期化信号送信ユニット50を備えている。不揮発性メモリ63は、バス40にデータが送受信可能なように接続されている。

不揮発性メモリ63を除いて、他の構成は、第1の実施の形態の情報処理装置1と同様であるので、説明を省略する。

【0072】

図10は、機能モジュール60−1〜60−nの構成の一例を示した図である。

機能モジュール60−1〜60−nは、図2に示した第1の実施の形態の機能モジュール20から不揮発性メモリ23を除いた構成である。そして、実行部21および初期化部22がバス40にデータなどを入出力可能に接続されている。

他の構成は、第1の実施の形態における機能モジュール20と同様であるので、詳細な説明を省略する。

なお、機能モジュール60−1〜60−nをそれぞれ区別しないときは、機能モジュール60と表記する。

【0073】

次に、図9および図10を参照して、機能モジュール60の動作を説明する。

第3の実施の形態の機能モジュール60は、第1の実施の形態で説明した図3のフローチャートのステップ103の初期化部22による実行部21の初期化の手順が異なる。

第1の実施の形態で説明した機能モジュール20では、初期化部22は機能モジュール20の不揮発性メモリ23から実行部21の初期化に用いるデータを読み出して、実行部21を初期化していた。

これに対して、第3の実施の形態における機能モジュール60−1〜60−nでは、バス40に接続された不揮発性メモリ63から、機能モジュール60−1〜60−nのそれぞれの実行部21を初期化するデータを、バス40を介して読み出す。このため、機能モジュール60−1〜60−nの初期化部22は、バス40に接続されている。

なお、不揮発性メモリ63は、機能モジュール60−1〜60−nのそれぞれに対応するデータを異なるアドレスの領域に保持し、アドレスによってデータを選択するようになっている。

【0074】

上記した事項を除くと、第3の実施の形態における情報処理装置1は、第2の実施の形態で説明したのと同様であるので、説明を省略する。

【0075】

なお、図9では、情報処理装置1はn個の機能モジュール60−1〜60−nを備えるとしたが、第1の実施の形態の情報処理装置1と同様に1個の機能モジュール60を備えてもよい。

そして、すべての機能モジュール60−1〜60−nの実行部21を初期化するデータを不揮発性メモリ63に保持するとしたが、一部の機能モジュール60であってもよい。また、機能モジュール60を複数の組に分け、それぞれの組に対応した複数の不揮発性メモリ63を備えてもよい。

そして、不揮発性メモリ23を備えた機能モジュール20(図2参照)と不揮発性メモリ23を備えない機能モジュール60とを混在させてもよい。

【0076】

さらに、図9のメインメモリ30に破線で示すように、メインメモリ30が不揮発性メインメモリ31と揮発性メインメモリ32とで構成され、不揮発性メインメモリ31のすべてまたは一部を、機能モジュール60−1〜60−nの実行部21を初期化するデータを保持する不揮発性メモリ63としてもよい。

【0077】

ここで、不揮発性メインメモリ31がオペレーションシステム(OS)、プログラム、テキスト、定数、変数などを保持し、揮発性メインメモリ32が作業領域(ワークエリア)として一時的に使用するデータなどを保持すると、情報処理装置1をオフにしたのち再びオンになったとき、OS、プログラムなどを再度ロードする必要がない。よって、情報処理装置1は、短い時間で動作状態になる。

なお、OSを必要としない場合もある。

【0078】

また、メインメモリ30が不揮発性メインメモリ31で構成され、揮発性メインメモリ32を備えないとしてもよい。

なお、不揮発性メインメモリ31は、前述した高速な読み書きができ、書き換え回数の制限が小さい不揮発性記憶素子(MRAM、FeRAM、PRAM、ReRAM等)で構成されているのが好ましい。

また、第3の実施の形態における情報処理装置1を制御部として、第2の実施の形態で説明した画像形成装置に用いてもよい。

【0079】

第3の実施の形態の情報処理装置1では機能モジュール60−1〜60−nに不揮発性メモリ23を含まないことにより、機能モジュール60−1〜60−nが製造しやすい。

【0080】

[第4の実施の形態]

第1の実施の形態、第2の実施の形態、第3の実施の形態における情報処理装置1(図1、図5、図9)では、機能モジュール20(または60)のビジー信号(/BUSY)が、CPU10の初期化信号受信端子11(/RST)に送信されていた。このため、図4、図6のタイミングチャートに示したように、すべての機能モジュール20の実行部21の設定が完了したのちに、CPU10が動作状態になる。

ここで、CPU10も初期化が必要な場合には、機能モジュール20の実行部21の初期化が完了してから、CPU10の初期化を行うことになる。すなわち、機能モジュール20の実行部21の初期化とCPU10の初期化とがシーケンシャルで(順に)行われることになる。

これに対して、第4の実施の形態の情報処理装置1では、CPU10の初期化と機能モジュール20の実行部21の初期化とを並行して行う。

【0081】

(情報処理装置1)

図11は、第4の実施の形態が適用される情報処理装置1の全体構成の一例を示した図である。

情報処理装置1は、CPU10、機能モジュール20、メインメモリ30、バス40、初期化信号送信ユニット50を備えている。

CPU10は、初期化信号送信ユニット50からの初期化信号51(/RST)を受信する初期化信号受信端子11(/RST)と、ビジー信号を送信するビジー信号送信端子12(/BUSY)とを備えている。

【0082】

そして、初期化信号送信ユニット50の初期化信号送信端子51(/RST)が、初期化信号線41を介して、CPU10の初期化信号受信端子11(/RST)と、機能モジュール20の初期化信号受信端子26(/RST)とに並列に接続されている。

さらに、CPU10のビジー信号送信端子12(/BUSY)と、機能モジュール20のビジー信号送信端子27(/BUSY)とが、許可信号線の一例としてのビジー信号線42に接続されている。そして、ビジー信号線42は、電流制限抵抗Rを介して電源電位Vddに接続されている。

【0083】

図12は、第4の実施の形態におけるCPU10の構成を示した図である。

CPU10は、命令処理部や読み出し/書き込み実行部や算術演算部などからなり、命令を実行する命令実行手段の一例としての命令実行部13、命令実行部13を初期状態に設定する他の初期化手段の一例としての初期化部14、命令実行部13を初期状態に設定するためのデータを保持する不揮発性メモリ15を備えている。さらに、CPU10は、オープンドレインバッファ16とインバータ17とを備えている。

【0084】

命令実行部13、初期化部14は、シーケンサ、カウンタ、レジスタなどを含む論理回路から構成されている。命令実行部13は、初期化信号受信端子131(/RST)およびイネーブル信号受信端子132(/EN)を備えている。初期化部14は、初期化信号受信端子141(/RST)およびビジー信号送信端子142(/BUSY)を備えている。

不揮発性メモリ15、オープンドレインバッファ16、インバータ17は、図2の不揮発性メモリ23、オープンドレインバッファ24、インバータ25と同様であるので説明を省略する。

【0085】

CPU10における接続関係を説明する。

CPU10の命令実行部13と初期化部14とは、データ、アドレス、命令などを双方向に転送可能に接続されている。同様に、初期化部14と不揮発性メモリ15とは、データ、アドレス、命令などを双方向に転送可能に接続されている。

【0086】

そして、CPU10の初期化信号受信端子11(/RST)は、命令実行部13の初期化信号受信端子131(/RST)と初期化部14の初期化信号受信端子141(/RST)とに並列に接続されている。つまり、初期化信号送信ユニット50から送信された初期化信号51(/RST)は、命令実行部13と初期化部14に並列に送信される。

一方、初期化部14のビジー信号送信端子142(/BUSY)は、オープンドレインバッファ16を介して、CPU10のビジー信号送信端子12(/BUSY)に接続されている。

また、オープンドレインバッファ16の出力端子は、インバータ17を介して命令実行部13に設けられたイネーブル信号受信端子132(/EN)に接続されている。つまり、初期化部14から発信されたビジー信号142(/BUSY)がアサート(「L」)のときは、オープンドレインバッファ16の出力端子が「L」であって、CPU10のビジー信号12(/BUSY)がアサート(「L」)になる。また、ビジー信号142(/BUSY)がネゲート(「H」)のときは、オープンドレインバッファ16の出力端子は「Hi−Z」であって、CPU10のビジー信号12(/BUSY)は「Hi−Z」になる。

なお、CPU10では、命令実行部13がバス40と接続されている。

【0087】

以上説明したように、第4の実施の形態におけるCPU10の構成は、図2で説明した機能モジュール20と同様であって、機能モジュール20の実行部21を命令実行部13に、初期化部22を初期化部14に、不揮発性メモリ23を不揮発性メモリ15に、オープンドレインバッファ24をオープンドレインバッファ16に、インバータ25をインバータ17に置き換えたものである。他の符号についても同様である。よって、初期化信号送信ユニット50から送信される初期化信号51(/RST)がアサートになってからのCPU10の初期化は、図3に示した機能モジュール20の初期化と同様である。よって、詳細な説明を省略する。

一方、機能モジュール20は、第1の実施の形態において図2で示した構成と同様である。

【0088】

次に、第4の実施の形態における情報処理装置1の動作を説明する。

図13は第4の実施の形態における情報処理装置1の動作を説明するタイミングチャートである。ここでは、第1の実施の形態の図4と同様に、時刻t1において初期化信号送信ユニット50が送信する初期化信号51(/RST)がアサートになる場合について説明する。

図13では、初期化信号51(/RST)、ビジー信号線42(図13の説明では/BUSYを付記する。)の出力レベル、機能モジュール20の実行部21の状態およびビジー信号27(/BUSY)の出力レベル、CPU10の命令実行部13の状態およびビジー信号12(/BUSY)の出力レベルを示している。

なお、時刻t1から時刻t4へと時間が経過するとする。この時刻t1〜時刻t4は図4と同じである。

【0089】

時刻t1の直前の状態は、CPU10の命令実行部13および機能モジュール20の実行部21は動作状態にある。すなわち、初期化信号送信ユニット50からCPU10の初期化信号受信端子11ならびに機能モジュール20の初期化信号受信端子26(/RST)に送信される初期化信号51(/RST)、CPU10の送信するビジー信号12(/BUSY)ならびに機能モジュール20の送信するビジー信号27(/BUSY)はともに「Hi−Z」である。しかし、ビジー信号線42(/BUSY)は、電流制限抵抗Rを介して電源電位Vddに接続されているので、「H」である。これにより、CPU10におけるイネーブル信号132(/EN)ならびに機能モジュール20におけるイネーブル信号212(/EN)はアサートである。

すなわち、時刻t1の直前においては、CPU10の命令実行部13および機能モジュール20の実行部21は動作状態にあって、機能モジュール20の初期化部22は停止状態にある。

【0090】

さて、時刻t1で、初期化信号送信ユニット50からの初期化信号51(/RST)がネゲートからアサート(「H」から「L」)になると、CPU10の命令実行部13および機能モジュール20の実行部21が動作状態から停止状態に移行する。

そして、CPU10のビジー信号12(/BUSY)および機能モジュール20のビジー信号27(/BUSY)がネゲートからアサート(「Hi−Z」から「L」)になる。さらに、ビジー信号線42が「H」から「L」になる。

【0091】

次に、時刻t2において初期化信号51(/RST)がアサートからネゲート(「L」から「H」)になると、CPU10における初期化部14による命令実行部13の初期化と機能モジュール20における初期化部22による実行部21の初期化とが並行して開始される。

そして、時刻t3で、機能モジュール20の初期化が完了すると、図2において説明したように、機能モジュール20の初期化部22のビジー信号送信端子222(/BUSY)がネゲート(「H」)になる。これにより、機能モジュール20のビジー信号27(/BUSY)が「Hi−Z」になる。しかし、CPU10の命令実行部13は初期化が完了していないため、ビジー信号12(/BUSY)は「L」に維持される。このため、ビジー信号線42が「L」に維持されたままとなる。すると、機能モジュール20のイネーブル信号212(/EN)も「H」でネゲートを維持する。

つまり、機能モジュール20の実行部21は、時刻t3で初期化が完了するが、イネーブル信号212(/EN)がネゲートであるので、時刻t3から後述する時刻t4までの間は停止状態にある。

【0092】

そして、時刻t4において、CPU10の命令実行部13の初期化が完了すると、CPU10の初期化部14のビジー信号142(/BUSY)が「L」から「H」になる。そして、CPU10のビジー信号12(/BUSY)が「L」から「Hi−Z」になる。すると、CPU10のビジー信号12(/BUSY)および機能モジュール20のビジー信号27(/BUSY)がともに「Hi−Z」になって、ビジー信号線42(/BUSY)が「H」になる。

これにより、CPU10の命令実行部13のイネーブル信号132(/EN)および機能モジュール20の実行部21のイネーブル信号212(/EN)がネゲートからアサート(「H」から「L」)になる。そして、CPU10の命令実行部13および機能モジュール20の実行部21が停止状態から動作状態に移行する。すなわち、情報処理装置1が動作可能な状態になる。

【0093】

ここでは、機能モジュール20の実行部21の初期化の所要時間が、CPU10の命令実行部13の初期化の所要時間より短いとしたが、逆の場合であっても同様である。

すなわち、CPU10または機能モジュール20の一方が初期化中であると、ビジー信号線42は、「L」に引き込まれた状態となって、初期化が終わっていても他方は停止状態となる。そして、CPU10および機能モジュール20の両方の初期化が完了したタイミングで、CPU10および機能モジュール20の両方が並行して停止状態から動作状態に移行する。

【0094】

第4の実施の形態の情報処理装置1では、CPU10の命令実行部13の初期化と機能モジュール20の実行部21の初期化とが並行して実施されるので、機能モジュール20の実行部21の初期化の完了後にCPU10の初期化が行われる場合に比べ、情報処理装置1の初期化信号51(/RST)がネゲートになってから動作可能になるまでの所要時間が短くなる。

また、CPU10の初期化と機能モジュール20の実行部21の初期化とのうち、所要時間が長い方の初期化が完了すると、ビジー信号線42(/BUSY)が「L」から「H」になって、CPU10および機能モジュール20の動作が開始する。よって、CPU10の初期化と機能モジュール20の実行部21の初期化の完了と、CPU10および機能モジュール20の動作の開始との間に、不要な待ち時間(オーバヘッド)が発生するのが抑制される。

【0095】

なお、第3の実施の形態と同様に、機能モジュール20が不揮発性メモリ23を備えない機能モジュール60であって、バス40にデータなどが入出力可能に接続された不揮発性メモリ63を備えていてもよい。また、メインメモリ30に不揮発性メインメモリ31を備えて、不揮発性メモリ63と兼ねていてもよい。

【0096】

[第5の実施の形態]

第4の実施の形態の情報処理装置1は、機能モジュール20を1つ備えていた。

第5の実施の形態の情報処理装置1では、第2の実施の形態と同様に、複数の機能モジュール20−1〜20−nを備えている。

【0097】

(情報処理装置1)

図14は、第5の実施の形態が適用される情報処理装置1の全体構成の一例を示した図である。

情報処理装置1は、CPU10、機能モジュール20−1〜20−n、メインメモリ30、バス40、初期化信号送信ユニット50を備えている。

CPU10は、第4の実施の形態において図12に示した構成と同様である。

機能モジュール20は、第1の実施の形態において図2に示した構成と同様である。

【0098】

そして、初期化信号送信ユニット50の初期化信号送信端子51(/RST)が、初期化信号線41に接続されている。そして、CPU10の初期化信号受信端子11(/RST)と、機能モジュール20−1〜20−nの初期化信号受信端子26(/RST)とが並列に初期化信号線41に接続されている。

さらに、CPU10のビジー信号送信端子12(/BUSY)と、機能モジュール20−1〜20−nのビジー信号送信端子27(/BUSY)とが、ビジー信号線42に接続されている。そして、ビジー信号線42は、電流制限抵抗Rを介して、電源電位Vddに接続されている。

【0099】

次に、第5の実施の形態における情報処理装置1の動作を説明する。

図15は第5の実施の形態における情報処理装置1の動作を説明するタイミングチャートである。ここでは、第2の実施の形態の図6と同様に、時刻t1において初期化信号送信ユニット50が初期化信号51(/RST)をネゲートからアサートにする場合について説明する。

図15では、初期化信号51(/RST)、ビジー信号線42(図15の説明では/BUSYを付記する。)、機能モジュール20−1〜20−nの実行部21の状態およびビジー信号27(/BUSY)の出力レベル、CPU10の命令実行部13の状態およびビジー信号12(/BUSY)の出力レベルを示している。

なお、時刻t1から時刻t4へと時間が経過するとする。この時刻t1〜時刻t4は図6と同じである。

【0100】

時刻t1の直前の状態は、第1の実施の形態と同様に、CPU10の命令実行部13および機能モジュール20−1〜20−nのそれぞれの実行部21は動作状態にある。

すなわち、初期化信号送信ユニット50からの初期化信号51(/RST)はネゲート(「H」)であるので、CPU10の初期化信号11(/RST)ならびに機能モジュール20−1〜20−nの初期化信号26(/RST)は「H」である。すると、CPU10の初期化部14のビジー信号12(/BUSY)および機能モジュール20−1〜20−nのそれぞれの初期化部22のビジー信号27(/BUSY)は、「Hi−Z」になっている。

ビジー信号線42(/BUSY)は、電流制限抵抗Rを介して電源電位Vddに接続されているので、CPU10におけるイネーブル信号132(/EN)(図12参照)および機能モジュール20−1〜20−nにおけるイネーブル信号212(/EN)(図2参照)は「L」(アサート)になっている。

すなわち、時刻t1の直前においては、CPU10の命令実行部13および機能モジュール20−1〜20−nのそれぞれの実行部21は動作状態にあって、CPU10の初期化部14および機能モジュール20−1〜20−nの初期化部22は停止状態にある。

【0101】

さて、時刻t1で、初期化信号送信ユニット50からの初期化信号51(/RST)がネゲートからアサート(「H」から「L」)になる)と、CPU10の命令実行部13および機能モジュール20−1〜20−nの実行部21が動作状態から停止状態に移行する。

そして、CPU10のビジー信号12(/BUSY)および機能モジュール20−1〜20−nのそれぞれのビジー信号27(/BUSY)が「Hi−Z」から「L」になる。そして、ビジー信号線42が「H」から「L」になる。すると、CPU10におけるイネーブル信号132(/EN)および機能モジュール20−1〜20−nにおけるイネーブル信号212(/EN)はアサートからネゲート(「L」から「H」)に移行する。これにより、CPU10の命令実行部13および機能モジュール20−1〜20−nのそれぞれの実行部21は動作状態から停止状態になる。

【0102】

次に、時刻t2において初期化信号(/RST)が解除される(ネゲート(「L」から「H」)になる)と、CPU10の命令実行部13の初期化と機能モジュール20−1〜20−nにおける初期化部22による実行部21の初期化とが並行して開始される。

そして、時刻t3で、初期化の所要時間が最も短い機能モジュール20−1の初期化が完了すると、図2において説明したように、機能モジュール20−1の初期化部22のビジー信号222(/BUSY)がネゲートになる。これにより、機能モジュール20−1のビジー信号27(/BUSY)が「L」から「Hi−Z」になる。しかし、CPU10および他の機能モジュール20−2〜20−nは初期化が完了していないため、CPU10のビジー信号12(/BUSY)および機能モジュール20−2〜20−nのビジー信号27(/BUSY)は「L」に維持される。このため、ビジー信号線42(/BUSY)は「L」に維持されたままとなる。すると、機能モジュール20−1のイネーブル信号212(/EN)も「H」でネゲートを維持する。

つまり、機能モジュール20−1の実行部21は、時刻t3で初期化が完了するが、イネーブル信号222(/EN)がネゲートであるので、時刻t3から後述する時刻t4までの間は停止状態にある。

【0103】

そして、時刻t4において、設定時間の最も長い機能モジュール20−2の初期化が完了する。

なお、CPU10の命令実行部13は、時刻t3と時刻t4との間の時刻において、初期化が完了し、機能モジュール20−1と同様に停止状態になっている。他の機能モジュール20−3〜20−nも同様である。

【0104】

さて、設定時間の最も長い機能モジュール20−2の初期化が完了すると、CPU10のビジー信号12(/BUSY)および機能モジュール20−1〜20−nのいずれのビジー信号27(/BUSY)も「Hi−Z」となる。これにより、ビジー信号線42(/BUSY)が「L」から「H」になる。そして、CPU10のイネーブル信号132(/EN)および機能モジュール20−1〜20−nのそれぞれのイネーブル信号212(/EN)がアサートになる。これにより、CPU10および機能モジュール20−1〜20−nが停止状態から動作状態に移行する。すなわち、情報処理装置1が動作可能な状態になる。

【0105】

ここでは、機能モジュール20−1の実行部21の初期化の所要時間が最も短く、機能モジュール20−2の実行部21の初期化の所要時間が最も長いとした。CPU10の命令実行部13の初期化の所要時間が最も短くてもよく、最も長くてもよい。

すなわち、CPU10の命令実行部13または機能モジュール20−1〜20−nの実行部21いずれかが初期化中であると、ビジー信号線42(/BUSY)は、「L」に引き込まれた状態となっている。このため、CPU10または機能モジュール20−1〜20−nのいずれかの初期化が終わっていても停止状態となっている。そして、CPU10および機能モジュール20−1〜20−nのすべての初期化が完了した時点で、CPU10および機能モジュール20−1〜20−nのすべてが並行して動作状態に移行する。

【0106】

第5の実施の形態の情報処理装置1では、CPU10の命令実行部13の初期化と機能モジュール20−1〜20−nのそれぞれの実行部21の初期化とが並行して実施されるので、機能モジュール20−1〜20−nの実行部21のすべての初期化の完了後にCPU10の初期化が行われる場合に比べ、情報処理装置1が動作可能になるまでの所要時間(立ち上がり時間)が短くなる。

また、CPU10の命令実行部13の初期化と機能モジュール20−1〜20−nのそれぞれの実行部21の初期化とのうち、最も所要時間が長い初期化が完了すると、ビジー信号線42が「L」から「H」になる。これにより、CPU10および機能モジュール20−1〜20−nの動作が開始するので、不要な待ち時間(オーバヘッド)の発生が抑制されている。

【0107】

なお、第3の実施の形態と同様に、機能モジュール20−1〜20−nが不揮発性メモリ23を備えない機能モジュール60−1〜60−nであって、バス40にデータなどが入出力可能に接続された不揮発性メモリ63を備えていてもよい。また、メインメモリ30に不揮発性メインメモリ31を備えて、不揮発性メモリ63と兼ねていてもよい。

【0108】

さらに、第5の実施の形態の情報処理装置1を第2の実施の形態で示した画像形成装置100の制御部として用いてもよい。

【0109】

なお、第5の実施の形態の情報処理装置1において、CPU10のビジー信号送信端子12(/BUSY)をIOポート(不図示)に接続した構成としてもよい。CPU10のIOポートは、機能モジュール20−1〜20−nのIOポート(不図示)と接続されている。

初期化信号51(/RST)が解除された(アサートからネゲートになった)とき、CPU10がソフトウエアを起動する。そして、ソフトウエアの起動が完了すると、IOポートへのビジー信号(/BUSY)を解除(ネゲート)し、機能モジュール20−1〜20−nへのアクセスを許可すると同時に、ソフトウエアがIOポートのビジー信号(/BUSY)の状態を監視し、ビジー信号(/BUSY)が解除(ネゲート)されるのを確認してから機能モジュール20−1〜20−nを使用するソフトウエアを起動するように構成する。このようにすることで、ソフトウエアを起動する時間が短縮される。

【符号の説明】

【0110】

1…情報処理装置、10…CPU、13…命令実行部、14、22…初期化部、15、23、63…不揮発性メモリ、20、20−1〜20−n、60、60−1〜60−n…機能モジュール、21…実行部、16、24…オープンドレインバッファ、17、25…インバータ、30…メインメモリ、31…不揮発性メインメモリ、32…揮発性メインメモリ、40…バス、41…初期化信号線、42…ビジー信号線、50…初期化信号送信ユニット、100…画像形成装置、120…UI部、130…画像形成部、140…画像読取部、150…送受信部、200…通信回線、300…コンピュータ、400…ファクシミリ装置、500…サーバ

【技術分野】

【0001】

本発明は、画像形成装置、情報処理装置および機能モジュールに関する。

【背景技術】

【0002】

情報処理装置は、論理演算または算術演算を実行する中央演算処理装置(CPU)と、ASIC(特定用途向け集積回路、Application Specific Integrated Circuit)などで構成されCPUの制御により予め定められた機能を実行する機能モジュールとを含んで構成されている。

【0003】

特許文献1には、情報処理装置内にCPU等に用いるシステムリセットとは独立した系統で動作するコントローラを持ち、そのコントローラがROMとRAMの間のデータ転送をシステムリセット期間中に行う機能を有する装置が記載されている。

特許文献2には、電源投入時に演算処理装置の初期化を行うリセット部からの入力によって周辺制御部用に設けた専用制御バスの動作を開始し、該周辺制御部の初期化を行うことによって、制御プログラムによる周辺制御ASIC初期化に要する時間を削除し、システム復帰時間を短縮することによって低消費電力化を実現し、ユーザの利便性を向上させる画像形成装置が記載されている。

特許文献3には、内部レジスタが不揮発性である不揮発回路と、内部レジスタが揮発性である一以上の揮発回路と、初期化要求機構とを備えた情報処理装置であって、前記初期化要求機構は、前記揮発回路を駆動する電源がオフになったことを検知する一以上の電源検知部と、前記電源がオフになったことを記録する初期化要求レジスタと、を備え、前記電源検知部は、前記電源がオフになったことを検知した場合、前記電源がオフになったことを示す第1情報を前記初期化要求レジスタに記録し、前記初期化要求機構は、前記初期化要求レジスタに少なくとも一以上の前記第1情報が記録されている場合、前記揮発回路の初期化が必要であることを前記不揮発回路に通知し、前記不揮発回路は、前記初期化要求機構から前記通知を受信した場合、前記不揮発回路の内部レジスタに保持されているプロセスの実行状態に合わせて、前記揮発回路の内部レジスタを設定し、前記内部レジスタの設定後に、前記揮発回路を起動する情報処理装置が記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003−337746号公報

【特許文献2】特開2003−223089号公報

【特許文献3】特開2010−170206号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、機能モジュールを備える情報処理装置では、動作可能な状態に立ち上げるためには機能モジュールについても初期化(リセット)を行うことが必要である。そして、機能モジュールの初期化を速やかに行い、情報処理装置が動作可能になるまでの所要時間(立ち上がり時間)を短くすることが求められている。

本発明は、動作可能になるまでの所要時間を短くした情報処理装置等を提供することを目的とする。

【課題を解決するための手段】

【0006】

請求項1に記載の発明は、画像を記録材に形成する画像形成部と、算術演算および論理演算を行う演算モジュールと、当該演算モジュールの演算結果に基づいて予め定められた機能を実行する実行手段と、初期化信号を受信すると当該実行手段による機能の実行を停止する停止手段と、当該初期化信号が解除されると当該実行手段を初期化する初期化手段とを備える機能モジュールと、前記初期化信号を送信する初期化信号送信手段とを備え、前記画像形成部を制御する制御部とを備える画像形成装置である。

請求項2に記載の発明は、論理演算または算術演算を実行する演算モジュールと、前記演算モジュールの演算結果に基づいて予め定められた機能を実行する実行手段と、初期化信号を受信すると当該実行手段による機能の実行を停止する停止手段と、当該初期化信号が解除されると当該実行手段を初期化する初期化手段とを備える機能モジュールと、前記初期化信号を送信する初期化信号送信手段とを備える情報処理装置である。

請求項3に記載の発明は、前記機能モジュールが、前記実行手段を初期化するためのデータを保持する記憶手段をさらに備えることを特徴とする請求項2に記載の情報処理装置である。

請求項4に記載の発明は、前記記憶手段が、MRAM、FeRAM、PRAM、ReRAM等の読み書き可能な不揮発性メモリであることを特徴とする請求項3に記載の情報処理装置である。

請求項5に記載の発明は、前記機能モジュールと前記演算モジュールとを接続するように設けられ、当該機能モジュールにおける前記実行手段の初期化が完了したことを当該演算モジュールに通報する通報信号線をさらに備えることを特徴とする請求項2ないし4のいずれか1項に記載の情報処理装置である。

請求項6に記載の発明は、前記機能モジュールの前記実行手段および前記演算モジュールは、当該機能モジュールが前記初期化信号を受信すると動作状態から停止状態に移行し、当該機能モジュールにおける当該実行手段の初期化が完了したことを前記通報信号線により通報されると停止状態から動作状態に移行することを特徴とする請求項5に記載の情報処理装置である。

請求項7に記載の発明は、前記実行手段が初期化によって設定される初期状態は、当該実行手段が初めて動作可能になったときの状態または当該実行手段の実行を再開するために実行が中断したときの状態であることを特徴とする請求項2ないし6のいずれか1項に記載の情報処理装置である。

請求項8に記載の発明は、前記演算モジュールが、命令を実行する命令実行手段と、前記初期化信号を受信すると当該命令実行手段を初期化する他の初期化手段とをさらに備え、前記演算モジュールと前記機能モジュールとを接続するように設けられ、当該演算モジュールにおける前記命令実行手段の初期化が完了し、且つ当該機能モジュールの前記実行手段の初期化が完了したとき、当該演算モジュールおよび当該機能モジュールの動作を許可する許可信号線をさらに備えることを特徴とする請求項2に記載の情報処理装置である。

請求項9に記載の発明は、予め定められた機能を実行する実行手段と、初期化信号を受信すると前記実行手段の動作を停止する停止手段と、前記初期化信号が解除されると前記実行手段を初期化する初期化手段とを備える機能モジュールである。

請求項10に記載の発明は、前記実行手段を初期化するためのデータを保持する記憶手段をさらに備えることを特徴とする請求項9に記載の機能モジュールである。

請求項11に記載の発明は、前記記憶手段が、MRAM、FeRAM、PRAM、ReRAM等の読み書き可能な不揮発性メモリであることを特徴とする請求項10に記載の機能モジュールである。

【発明の効果】

【0007】

請求項1の発明によれば、本構成を備えない場合に比べ、画像形成装置の立ち上げにかかる所要時間を短くできる。

請求項2の発明によれば、初期化手段を備えない場合に比べ、情報処理装置が動作可能になるまでの所要時間を短くできる。

請求項3、4の発明によれば、本構成を備えない場合に比べ、情報処理装置が動作可能になるまでの所要時間をさらに短くできる。

請求項5の発明によれば、本構成を備えない場合に比べ、情報処理装置の立ち上げにおける待ち時間を抑制できる。

請求項6の発明によれば、本構成を備えない場合に比べ、不安定な動作を抑制できる。

請求項7の発明によれば、本構成を備えない場合に比べ、動作を再開させる状態が選択できる。

請求項8の発明によれば、本構成を備えない場合に比べ、CPUと機能モジュールとを並行して初期化できる。

請求項9の発明によれば、本構成を備えない場合に比べ、機能モジュールが安定な状態で初期化できる。

請求項10、11の発明によれば、本構成を備えない場合に比べ、機能モジュールの初期化の所要時間を短くできる。

【図面の簡単な説明】

【0008】

【図1】第1の実施の形態が適用される情報処理装置の全体構成の一例を示した図である。

【図2】機能モジュールの構成の一例を示した図である。

【図3】機能モジュールの動作を説明するフローチャートである。

【図4】第1の実施の形態における情報処理装置の動作を説明するタイミングチャートである。

【図5】第2の実施の形態が適用される情報処理装置の全体構成の一例を示した図である。

【図6】第2の実施の形態が適用される情報処理装置の動作を説明するタイミングチャートである。

【図7】画像形成装置の構成の一例を示す図である。

【図8】画像形成装置と通信回線に接続された機器との関係を説明した図である。

【図9】第3の実施の形態が適用される情報処理装置の全体構成の一例を示した図である。

【図10】第3の実施の形態における機能モジュールの構成の一例を示した図である。

【図11】第4の実施の形態が適用される情報処理装置の全体構成の一例を示した図である。

【図12】第4の実施の形態におけるCPUの構成の一例を示した図である。

【図13】第4の実施の形態における情報処理装置の動作を説明するタイミングチャートである。

【図14】第5の実施の形態が適用される情報処理装置の全体構成の一例を示した図である。

【図15】第5の実施の形態における情報処理装置の動作を説明するタイミングチャートである。

【発明を実施するための形態】

【0009】

以下、添付図面を参照して、本発明の実施の形態について詳細に説明する。

[第1の実施の形態]

(情報処理装置1)

図1は、第1の実施の形態が適用される情報処理装置1の全体構成の一例を示した図である。

情報処理装置1は、論理演算および算術演算を行うALU(Alithmetic Logical Unit:論理算術演算ユニット)などを備えた演算モジュールの一例としての中央演算処理装置(以下ではCPUと表記する。)10、CPU10の演算結果に基づいて、予め定められた機能を実行する機能モジュール20、読み書き可能なメインメモリ30、データ、アドレス、命令(コマンド)などを転送するバス40、機能モジュール20を初期化する指示である初期化信号(/RST)を送信する初期化信号送信手段の一例としての初期化信号送信ユニット50を備えている。

【0010】

そして、初期化信号送信ユニット50は、初期化信号51(/RST)を送信する初期化信号送信端子51(/RST)を備えている。また、機能モジュール20は、初期化信号51(/RST)を受信する初期化信号受信端子26(/RST)およびビジー信号27(/BUSY)を発信するビジー信号送信端子27(/BUSY)を備えている。さらに、CPU10は、初期化信号11(/RST)を受信する初期化信号受信端子11(/RST)を備えている。

なお、「/RST」などの「/」は、そのあとに続く記号(アルファベットなど)の上にあるもの(アッパーバー)とし、記号(アルファベットなど)で示される信号が負論理であることを示す。また、端子(例えば、初期化信号送信端子51(/RST))とその端子に送受信される信号(例えば、初期化信号51(/RST))とを区別しないで同じ番号で表記する。

【0011】

機能モジュール20の例については、情報処理装置1を制御部とする装置の一例としての画像形成装置100(後述する図7)において説明する。

【0012】

次に、情報処理装置1における接続関係を説明する。

CPU10、機能モジュール20、メインメモリ30は、データ、アドレス、命令などを双方向に送受信可能なように、バス40に接続されている。すなわち、CPU10、機能モジュール20、メインメモリ30は、バス40に並列に接続され、バス40を介してデータ、アドレス、命令などを相互に送受信可能になっている。

【0013】

初期化信号送信ユニット50の初期化信号送信端子51(/RST)は、機能モジュール20の初期化信号受信端子26(/RST)に初期化信号線41を介して接続されている。つまり、初期化信号送信ユニット50が初期化信号送信端子51(/RST)から送信した初期化信号51(/RST)は、機能モジュール20の初期化信号受信端子26(/RST)によって受信される。

機能モジュール20のビジー信号送信端子27(/BUSY)とCPU10の初期化信号受信端子11(/RST)とは、通報信号線の一例としてのビジー信号線42で接続されている。つまり、機能モジュール20がビジー信号送信端子27(/BUSY)から送信したビジー信号(/BUSY)は、CPU10の初期化信号受信端子11(/RST)に初期化信号11(/RST)として受信される。また、ビジー信号線42は、電流制限抵抗Rを介して、電源電位Vddに接続されている。

なお、図1では、上記の信号の流れを矢印で示している。

【0014】

(機能モジュール20)

次に、機能モジュール20の構成を説明する。

図2は、機能モジュール20の構成の一例を示した図である。

機能モジュール20は、予め定められた機能を実行する実行手段の一例としての実行部21、実行部21を初期状態に設定する初期化手段の一例としての初期化部22、実行部21を初期状態に設定するためのデータを保持する記憶手段の一例としての不揮発性メモリ23を備えている。さらに、機能モジュール20は、オープンドレインバッファ24とインバータ25とを備えている。なお、実行部21は実行を停止する停止手段の一例でもある。

【0015】

実行部21、初期化部22は、シーケンサ、カウンタ、レジスタなどを含む論理回路から構成されている。実行部21は、初期化信号受信端子211(/RST)およびイネーブル信号受信端子212(/EN)を備えている。初期化部22は、初期化信号受信端子221(/RST)およびビジー信号送信端子222(/BUSY)を備えている。

不揮発性メモリ23は、“1”/“0”で表されたデータを記憶する機能を有している。そして、「不揮発性」とは、電力が供給されている間はもとより電力の供給がない場合であっても、データを保持することをいう。

なお、機能モジュール20の実行部21、初期化部22はレジスタなどを有し、電力が供給されているときはデータを保持するが、電力が供給されていないときはデータが失われる揮発性である。CPU10およびメインメモリ30も揮発性であるとする。

【0016】

そして、オープンドレインバッファ24は、入力信号が“0”(ここでは、後述する「L」に対応する。)の時には“0”(「L」)を出力し、入力信号が“1”(ここでは、後述する「H」に対応する。)の時にはハイ・インピーダンス(高抵抗)状態(「Hi−Z」と表記する。)になる。

一方、インバータ25は、入力信号と極性が反転した信号を出力する。

【0017】

機能モジュール20(実行部21、初期化部22、不揮発性メモリ23、オープンドレインバッファ24、インバータ25)は、シリコン等で構成された1つの半導体チップ(例えば、ASIC(特定用途向け集積回路、Application Specific Integrated Circuit))として構成されてもよい。また、実行部21、初期化部22、不揮発性メモリ23、オープンドレインバッファ24、インバータ25を組み合わせて構成した複数の半導体チップであってもよい。また、実行部21、初期化部22または不揮発性メモリ23が、分割されて構成されてもよい。

【0018】

機能モジュール20における接続関係を説明する。

機能モジュール20の実行部21と初期化部22とは、データ、アドレス、命令などを双方向に転送可能に接続されている。同様に、初期化部22と不揮発性メモリ23とは、データ、アドレス、命令などを双方向に転送可能に接続されている。

【0019】

そして、機能モジュール20の初期化信号受信端子26(/RST)は、実行部21の初期化信号受信端子211(/RST)と初期化部22の初期化信号受信端子221(/RST)とに並列に接続されている。つまり、初期化信号送信ユニット50から送信された初期化信号51(/RST)は、実行部21と初期化部22に並列に送信される。

一方、初期化部22のビジー信号送信端子222(/BUSY)は、オープンドレインバッファ24を介して、機能モジュール20のビジー信号送信端子27(/BUSY)に接続されている。すなわち、ビジー信号222(/BUSY)が“0”(「L」)のときは、ビジー信号27(/BUSY)も“0”(「L」)になる。しかし、ビジー信号222(/BUSY)が“1”(「H」)のときは、オープンドレインバッファ24の出力端子は「Hi−Z」になるので、ビジー信号27(/BUSY)はビジー信号線42の状態により設定される。

また、オープンドレインバッファ24の出力端子は、インバータ25を介して実行部21に設けられたイネーブル信号受信端子212(/EN)に接続されている。つまり、初期化部22から発信されたビジー信号222(/BUSY)が“0”(「L」)のときは、イネーブル信号212(/EN)は“1”(「H」)になり、初期化部22から発信されたビジー信号222(/BUSY)が“1”(「H」)のときは、イネーブル信号212(/EN)はビジー信号線42の状態により設定される。

なお、機能モジュール20では、実行部21がバス40と接続されている。

【0020】

情報処理装置1の機能モジュール20は、実行部21を初期状態に設定する初期化部22を備えている。すなわち、機能モジュール20は、CPU10による制御によらず、初期状態に設定できる機能を有している。

ここで、初期状態とは、実行部21が初めて動作可能になったときの状態(リセット後の状態)であってもよく、実行部21の実行が中断されたとき、動作を再開したい状態であってもよい。実行が中断されたときの例としては、情報処理装置1がオフになる直前の実行部21の状態が上げられる。

そして、機能モジュール20は、初期化信号送信ユニット50からの初期化信号51(/RST)を受信する(後述するようにネゲートからアサートになる)と、実行部21は動作状態から停止状態に移行し、初期化部22は実行部21を初期状態に設定するための処理を開始可能な状態に移行する。そして、初期化信号51(/RST)が解除される(アサートからネゲートに移行する)と、初期化部22は実行部21を初期状態に設定するための処理(初期化)を実行するようになっている。

【0021】

すなわち、初期化信号51(/RST)がアサートであるとき、機能モジュール20の実行部21は動作を停止している。

これは、電源が投入されて規定の電圧に上昇し切らない間に機能モジュール20が動作を開始することを抑制するためである。また、電源投入後に安定な動作状態になるまで暫く待たなければならない部品(例えば、水晶発振器)がある場合には、安定な動作状態になるまで待つためである。これにより、機能モジュール20の不安定な動作が抑制される。

CPU10でも同様である。

【0022】

また、初期化信号51(/RST)がアサートからネゲートになったときに行われる初期化は、機能モジュール20の実行部21を動作可能な状態にすることをいい、例えば、フリップフロップを予め定められた状態にセット(プリセット)すること、レジスタに予め定められたデータをセットするなどの処理が含まれる。また、位相同期回路(PLL、Phase Locked Loop)が含まれる場合には、PLLは電源の投入時に停止状態にあるので、停止状態を解除し、発振が安定(PLLロック)したらクロックドライバの出力をイネーブルにする。このように、初期化には、手順を踏んで動作可能な状態にする処理も含まれる。

【0023】

なお、初期化信号(/RST)がアサートであるとは、信号の極性によらず初期化信号(/RST)が有効な状態(アクティブ)にあることをいう。一方、初期化信号(/RST)が無効な状態(インアクティブ)にあることをネゲート(無効)という。他の信号においても同様で、信号の極性を問わないで、信号が有効であるときがアサート、信号が無効であるときがネゲートである。

ここでは、一例として電圧レベルが高い状態(「H」)をネゲートとし、低い状態(「L」)をアサートとする負論理で示す。また、“0”がアサートに対応し、“1”がネゲートに対応する。そして、電源電位Vddは「H」に対応する。

【0024】

次に、ビジー信号(/BUSY)およびイネーブル信号(/EN)について説明する。

ビジー信号(/BUSY)がアサートであるとは、ビジー信号(/BUSY)を送信する回路(初期化部22など)が他の回路(実行部21など)に、新たな動作の準備が整っていないことを示す。例えば、初期化部22からのビジー信号222(/BUSY)がアサートであると、初期化部22が実行部21への初期化を実行中で、初期化が完了していないことを示す。そして、ビジー信号222(/BUSY)がネゲートになると、初期化部22は実行部21の初期化を完了し、実行部21への新たな実行指示が受付可能な状態にあることを示す。

さらに、イネーブル信号(/EN)がアサートであるとは、イネーブル信号(/EN)を受信した回路が動作することを許可され、動作状態(イネーブル)になることを示す。例えば、実行部21が受信するイネーブル信号212(/EN)がアサートであると、実行部21は動作状態(イネーブル)にある。そして、イネーブル信号212(/EN)がネゲートであると、実行部21は停止状態(ディセーブル)になる。

【0025】

初期化部22がシーケンサなどのハードウエアで構成され、機能モジュール20の実行部21を初期状態に設定する初期化をハードウエア制御で行うと、初期化に要する時間が短くなる(所要時間が短い)。しかし、機能モジュール20の初期化をソフトウエアによる制御(ソフトウエア制御)で行ってもよい。

【0026】

(機能モジュール20の動作)

次に、機能モジュール20の動作を説明する。

図3は、機能モジュール20の動作を説明するフローチャートである。

ここでは、初期化信号送信ユニット50からの初期化信号51(/RST)がアサートになってからの機能モジュール20の動作を説明する。すなわち、“Reset”からの動作を説明する。

【0027】

以下、図1、2を参照しつつ、図3のフローチャートを説明する。

初期化信号51(/RST)がアサートになると、図1に示すように、機能モジュール20の初期化信号26(/RST)がアサートになる。そして、図2に示すように、機能モジュール20の実行部21の初期化信号211(/RST)および初期化部22の初期化信号221(/RST)がアサートになる。

すると、実行部21は動作状態から停止状態に移行し、初期化部22は実行部21を初期状態に設定するための処理を開始可能な状態に移行する(ステップ101)。

このとき、初期化部22のビジー信号222(/BUSY)がアサートになると、前述したように、イネーブル信号212(/EN)がネゲートになる。

【0028】

そして、初期化信号51(/RST)が解除される(アサートからネゲートに移行する)のを待つ(ステップ102)。

なお、初期化信号51(/RST)がアサートである期間は予め定められている。すなわち、前述したように、電源が投入されて規定の電圧に上昇しきらない間に機能モジュール20が動作を開始することを抑制したり、水晶発振器などが電源投入後に安定な動作状態になるまで待ったりするためである。

【0029】

次に、初期化信号51(/RST)が解除される(アサートからネゲートに移行する)と、初期化部22は実行部21を初期状態に設定するための処理(初期化)を実行する(ステップ103)。

そして、実行部21の初期化が終了するのを待つ(ステップ104)。

【0030】

実行部21の初期化が終了すると、初期化部22が動作を停止し、ビジー信号222(/BUSY)がアサートからネゲートに移行する。

すると、オープンドレインバッファ24の出力端子が「Hi−Z」になる。このとき、図1で示したように、ビジー信号線42は、電流制限抵抗Rを介して、電源電位Vddに接続されているので、ビジー信号27(/BUSY)はアサートからネゲートに移行する。よって、イネーブル信号212(/EN)はネゲートからアサートに移行する(ステップ105)。

【0031】

初期化信号送信ユニット50からの初期化信号51(/RST)がネゲートである間は、実行部21は実行を継続する。しかし、初期化信号51(/RST)がネゲートからアサートになると、ステップ101に戻る(ステップ106)。

【0032】

図4は、第1の実施の形態における情報処理装置1の動作を説明するタイミングチャートである。図4では、初期化信号51(/RST)、ビジー信号線42(図4の説明では/BUSYを付記する。)、機能モジュール20のイネーブル信号212(/EN)の出力レベル、機能モジュール20の実行部21およびCPU10の状態を示している。なお、初期化信号51(/RST)、ビジー信号線42(/BUSY)、イネーブル信号212(/EN)については、アサートの状態を「アサート」と表記した。表記していない部分は「ネゲート」である。

また、時刻t1から時刻t4へと時間が経過するとする。なお、時刻t3は後述する図6、13、15との整合を図るために設けている。

【0033】

以下、図1、2、3を参照しつつ、図4のタイミングチャートを説明する。

時刻t1において、初期化信号送信ユニット50からの初期化信号51(/RST)がネゲートからアサートになる(「H」から「L」になる)とする。

初めに、時刻t1の直前の状態を説明する。時刻t1の直前では、CPU10および機能モジュール20の実行部21は動作状態にあるとする。

この状態を説明する。時刻t1の直前では、初期化信号51(/RST)はネゲート(「H」)である。前述したように、初期化部22のビジー信号222(/BUSY)はネゲート(「H」)であるので、機能モジュール20のオープンドレインバッファ24の出力端子は「Hi−Z」となる。よって、機能モジュール20のビジー信号27(/BUSY)は「Hi−Z」である。しかし、ビジー信号線42(/BUSY)は、電流制限抵抗Rを介して、電源電位Vddに接続されている。これにより、イネーブル信号212(/EN)はアサート(「L」)になる。すなわち、機能モジュール20の実行部21は動作状態にある。

また、ビジー信号線42(/BUSY)は「H」であるので、CPU10の初期化信号11(/RST)もネゲートである。よって、CPU10も動作状態である。

【0034】

時刻t1において、初期化信号51(/RST)がネゲートからアサート(「H」から「L」)に移行すると、初期化部22のビジー信号222(/BUSY)がアサートになる(「H」から「L」になる)(図3のステップ101)。すると、オープンドレインバッファ24の出力端子が「L」になって、機能モジュール20のビジー信号27(/BUSY)が「Hi−Z」から「L」に移行する。すると、ビジー信号線42(/BUSY)が「H」から「L」に移行する。これにより、イネーブル信号212(/EN)がアサートからネゲートに移行する(「L」から「H」になる)。よって、機能モジュール20の実行部21は停止状態になる。

【0035】

ビジー信号線42(/BUSY)はCPU10の初期化信号受信端子11(/RST)に接続されている。ビジー信号線42(/BUSY)が「H」から「L」に移行すると、CPU10の初期化信号11(/RST)がネゲートからアサートに移行し、CPU10が動作状態から停止状態に移行する。

【0036】

次に、時刻t2において初期化信号51(/RST)がネゲート(「L」から「H」)になると、初期化部22による実行部21の初期化が開始される(ステップ103)。

そして、時刻t4で初期化部22による実行部21の初期化が完了すると、初期化部22の送信するビジー信号27(/BUSY)が「L」から「Hi−Z」に移行する。これにより、ビジー信号線42(/BUSY)が「L」から「H」に移行し、イネーブル信号212(/EN)がネゲートからアサート(「H」から「L」)に移行する(ステップ105)。そして、実行部21が停止状態から動作状態に移行する。

【0037】

さらに、ビジー信号線42が「L」から「H」に移行することで、CPU10の初期化信号11(/RST)もアサートからネゲートになる。これにより、CPU10の実行が許可され、動作状態になる。すなわち、情報処理装置1が動作可能な状態になる。

【0038】

ここで、不揮発性メモリ23について説明する。

不揮発性メモリ23は、実行部21が初めて動作可能になったときの状態(リセット後の状態)に設定するデータを保持してもよく、実行部21の実行が中断されたときの状態であって、その状態から動作を再開したい状態のデータを保持してもよい。例えば、不揮発性メモリ23は、情報処理装置1のオフになる直前における実行部21の状態のデータ(レジスタおよびカウンタなどのデータ、シーケンサ、フリップフロップなどの状態に関するデータ)を保持する。

初期化部22が、実行部21が初めて動作可能になったときの状態(リセット後の状態)に設定するデータを読み出して、実行部21を初期化する場合には、機能モジュール20(実行部21)は初めて動作可能になったときの状態(リセット後の状態)で動作可能になる。

一方、初期化部22が、情報処理装置1のオフになる直前における実行部21の状態のデータを読み出して、実行部21を初期化する場合には、機能モジュール20(実行部21)は情報処理装置1がオフになる直前の状態(実行が中断したときの状態)から動作が可能になる(実行を再開する)。

【0039】

なお、機能モジュール20を初期化状態に設定するデータの場合には、データは読み出せればよく、不揮発性メモリ23はROM(リードオンリーメモリ)で構成されていてもよい。

一方、機能モジュール20をオフになる直前の状態から再開させるには、不揮発性メモリ23は、オフになる直前の実行部21の状態を示すデータを保持(退避)し、オフになっても保持し続けていることが必要となる。よって、不揮発性メモリ23は、読み書き可能な「不揮発性」のメモリであることが必要となる。

ここで、「不揮発性」とは、電力の供給がある場合に加え、電力の供給がなくなった場合においても、情報(“1”/“0”)を保持する(保持し続ける)記憶機能をいう。

【0040】

そして、オフになる直前の実行部21の状態を示すデータの書き込み(退避)は、オフになる直前に行ってもよく、実行部21の状態が変化するタイミング毎に行ってもよい。実行部21の状態が変化するタイミング毎に行う場合には、オフにする直前に書き込みを行わないで、情報処理装置1をオフにしてよい。

しかし、実行部21の状態が変化するタイミング毎に行う場合には、読み書き可能な不揮発性メモリ23は、高速に読み書きできる不揮発性記憶素子を用いることが好ましい。これにより、書き込み時間による機能モジュール20や情報処理装置1の処理速度の低下が抑制される。

【0041】

高速に読み書きできる不揮発性記憶素子としては、磁気メモリ(magnetoresistive RAM:MRAMと表示する。)、強誘電体メモリ(ferroelectric RAM:FeRAMと表記する。)、相変化メモリ(phase change RAM:PRAMと表記する。)、抵抗メモリ(resistance RAM:ReRAMと表記する。)等がある。

MRAMは、2枚の磁性積層膜をトンネル磁気抵抗膜で挟み、重ねた磁性積層膜の磁化のなす相対角度によりトンネル磁気抵抗膜の抵抗が変化する磁気抵抗(magnetoresistive:MR)効果を用いて情報(“1”/“0”)を保持する。FeRAMは、PZT(Pb(Zr、Ti)O3)などの強誘電体の分極を用いて情報(“1”/“0”)を保持する。PRAMは、カルコゲナイドの相変化にともなう抵抗変化により情報(“1”/“0”)を保持する。ReRAMは、電圧の印加による電気抵抗の大きな変化(CER(colossal electro−resistance)効果)を利用し、抵抗変化により情報(“1”/“0”)を保持する。

【0042】

これらの不揮発性記憶素子(MRAM、FeRAM、PRAM、ReRAM)は、DRAM、SRAMと同様に半導体基板上にセルをマトリクス状に高密度に配置でき、一体形成された駆動回路により高速な読み書きができる。さらに、書き換え回数の制限が原理的にない、または書き換え可能な回数が極めて大きい(以下では、書き換え回数の制限が小さいと表記する)。

このため、これらの不揮発性記憶素子(MRAM、FeRAM、PRAM、ReRAM等)は、不揮発性メモリ23に適用しやすい。

【0043】

なお、不揮発性記憶素子には、MOSトランジスタのゲート電極(フローティングゲート)に蓄積した電荷の有無により情報(“1”/“0”)を保持するフラッシュメモリ、EEPROM(Electrically Erasable Programmable ROM)などもある。フラッシュメモリおよびEEPROMは、電気的に状態(“1”/“0”)の読み書きができるが、前述の不揮発性記憶素子(MRAM、FeRAM、PRAM、ReRAM等)に比べ、読み書きの速度、特に書き込みの速度が遅い。そして、フラッシュメモリ、EEPROMは、書き換え回数に制限がある。

これらのフラッシュメモリおよびEEPROMを、不揮発性メモリ23に適用してもよい。

【0044】

また、不揮発性メモリ23の代わりに、DRAM、SRAMなどの揮発性メモリを使用してもよい。揮発性メモリを使用する場合には、初期化の前に初期化に必要なデータを情報処理装置1のメインメモリ30から読み出して、書き込めばよい。

【0045】

以上説明したように、第1の実施の形態の情報処理装置1では、初期化信号送信ユニット50から送信された初期化信号51(/RST)がアサートになると、機能モジュール20が動作を停止(動作状態から停止状態へ移行)し、それに伴いCPU10も動作を停止(動作状態から停止状態へ移行)する。そして、機能モジュール20が、初期状態に初期化されると、CPU10が動作状態になる。これにより、CPU10、機能モジュール20を含む情報処理装置1が立ち上がる(停止状態から動作状態になる)。

そして、機能モジュール20のビジー信号27(/BUSY)をCPU10の初期化信号11(/RST)としているので、機能モジュール20の初期化が終わり、ビジー信号27(/BUSY)がネゲートになると、CPU10が動作状態になる。これにより、機能モジュール20の初期化の終了とCPU10の動作開始との間に不要な待ち時間(オーバヘッド)が発生することが抑制される。すなわち、情報処理装置1は、初期化信号51(/RST)がアサートになってから動作可能になるまでの立ち上げに要する時間が短い。

また、機能モジュール20は初期化部22を備えているので、機能モジュール20の初期化にCPU10の制御を必要としない。そして、機能モジュール20の初期化部22による実行部21の初期化をハードウエア制御で行うと、ソフトウエアを用いたソフトウエア制御で行う場合に比べ、機能モジュール20の初期化に要する所要時間をさらに短くすることができる。

【0046】

なお、初期化信号送信ユニット50からの初期化信号51(/RST)の送信は、情報処理装置1がオンになった(電源が投入された)ときに、送信されるようにするのが好ましい。このとき、初期状態への設定またはオフになる直前の状態からの再開のいずれかを選択できるようにしてもよい。

また、ボタン等が押されることで、初期化信号送信ユニット50から初期化信号51(/RST)が送信されてもよい。このときも、初期状態への設定またはボタン等が押される直前の状態からの再開のいずれかを選択できるようにしてもよい。

【0047】

[第2の実施の形態]

第1の実施の形態の情報処理装置1は、機能モジュール20を1つ備えていた。第2の実施の形態の情報処理装置1は、複数の機能モジュール20−1〜20−n(nは整数)を備えている。

【0048】

(情報処理装置1)

図5は、第2の実施の形態が適用される情報処理装置1の全体構成の一例を示した図である。

情報処理装置1は、CPU10、機能モジュール20−1〜20−n、メインメモリ30、バス40、初期化信号送信ユニット50を備えている。

なお、機能モジュール20−1〜20−nをそれぞれ区別しないときは、機能モジュール20と表記する。

【0049】

機能モジュール20−1〜20−nは、バス40にデータ、アドレス、命令などを双方向に送受信可能に並列に接続されている。

また、初期化信号送信ユニット50の初期化信号送信端子51(/RST)は、初期化信号線41を介して、機能モジュール20−1〜20−nのそれぞれの初期化信号受信端子26(/RST)に並列に接続されている。

そして、機能モジュール20−1〜20−nのそれぞれのビジー信号送信端子27(/BUSY)は、ビジー信号線42に並列に接続されている。そして、ビジー信号線42の一端は、CPU10の初期化信号受信端子11(/RST)に接続されている。また、ビジー信号線42の他端は、電流制限抵抗Rを介して、電源電位Vddに接続されている。

【0050】

第2の実施の形態の機能モジュール20−1〜20−nは、図2に示した第1の実施の形態の機能モジュール20と同様の構成を有し、図3のフローチャートで示したのと同様に動作する。よって、機能モジュール20−1〜20−nについての説明を省略する。

【0051】

次に、第2の実施の形態が適用される情報処理装置1の動作を説明する。

図6は、第2の実施の形態が適用される情報処理装置1の動作を説明するタイミングチャートである。ここでは、第1の実施の形態の図4と同様に、時刻t1において初期化信号送信ユニット50が初期化信号51(/RST)をネゲートからアサートにする場合について説明する。

図6では、初期化信号51(/RST)、ビジー信号線42(図6の説明では/BUSYを付記する。)の出力レベル、機能モジュール20−1〜20−nのそれぞれの実行部21の状態およびビジー信号27(/BUSY)の出力レベル、CPU10の状態を示している。

なお、時刻t1から時刻t4へと時間が経過するとする。この時刻t1〜時刻t4は図4と同じである。

【0052】

時刻t1の直前の状態は、第1の実施の形態と同様に、CPU10および機能モジュール20−1〜20−nの実行部21は動作状態にある。一方、機能モジュール20−1〜20−nのそれぞれの初期化部22は停止状態にある。

初期化信号送信ユニット50から機能モジュール20−1〜20−nのそれぞれの初期化信号受信端子26(/RST)に送信される初期化信号51(/RST)はネゲート(「H」)である。このとき、機能モジュール20−1〜20−nの初期化部22のビジー信号222(/BUSY)は「H」である。よって、オープンドレインバッファ24の出力端子は「Hi−Z」である。これにより、機能モジュール20−1〜20−nのそれぞれのビジー信号27(/BUSY)はともに「Hi−Z」である。しかし、ビジー信号線42(/BUSY)は、電流制限抵抗Rを介して電源電位Vddに接続されているので、ネゲートであり、機能モジュール20−1〜20−nのそれぞれのイネーブル信号212(/EN)はアサートである。

そして、ビジー信号線42(/BUSY)の一端が接続されたCPU10の初期化信号11(/RST)も「H」(ネゲート)になっている。また、機能モジュール20の実行部21のイネーブル信号212(/EN)は「L」(アサート)になっている。

すなわち、時刻t1の直前においては、CPU10、および機能モジュール20−1〜20−nのそれぞれの実行部21は動作状態にある。そして、機能モジュール20−1〜20−nの初期化部22は停止状態にある。

【0053】

さて、時刻t1で、初期化信号送信ユニット50からの初期化信号51(/RST)がネゲートからアサートになる(「H」から「L」になる)と、機能モジュール20−1〜20−nの実行部21が動作状態から停止状態に移行する。

そして、機能モジュール20−1〜20−nのそれぞれのビジー信号27(/BUSY)が「Hi−Z」から「L」に移行する。これにより、ビジー信号線42(/BUSY)が「H」から「L」に移行する。

そして、CPU10の初期化信号11(/RST)が「H」から「L」に移行して、ネゲートからアサートになり、CPU10が動作状態から停止状態に移行する。

【0054】

次に、時刻t2において初期化信号51(/RST)がアサートからネゲート(「L」から「H」)になると、それぞれの機能モジュール20−1〜20−nにおいて初期化部22による実行部21の初期化が並行して開始される。

そして、時刻t3で、最も初期化の所要時間が短い機能モジュール20−1の初期化が完了する。すると、図2において説明したように、機能モジュール20−1の初期化部22のビジー信号222(/BUSY)がネゲート(「H」)になる。これにより、機能モジュール20−1のオープンドレインバッファ24の出力端子が「L」から「Hi−Z」になって、ビジー信号27(/BUSY)は「Hi−Z」になる。しかし、他の機能モジュール20−2〜20−nは初期化が完了していないため、機能モジュール20−2〜20−nのビジー信号27(/BUSY)は「L」である。このため、ビジー信号線42(/BUSY)が「L」に維持され、機能モジュール20−1のビジー信号27(/BUSY)は「H」になることができず「L」を維持する。すると、機能モジュール20−1のイネーブル信号212(/EN)も「H」でネゲートを維持する。

つまり、機能モジュール20−1の実行部21は、時刻t3で初期化が完了するが、時刻t3から後述する時刻t4までの間は停止状態にある。

【0055】

ビジー信号線42(/BUSY)は、機能モジュール20−1〜20−nのうち1つでも初期化状態であると「L」に設定されるようになっている。すなわち、機能モジュール20−1〜20−nが1つでも初期化状態にあると、「L」を出力するビジー信号送信端子27(/BUSY)がビジー信号線42を「L」に引き込むようになっている。

【0056】

時刻t3において、他の機能モジュール20−2〜20−nは、初期化を継続している。そして、CPU10は停止状態を継続する。

【0057】

そして、時刻t4で、最も初期化の所要時間が長い機能モジュール20−2の初期化が完了する。すると、機能モジュール20−2の機能モジュール20−2のビジー信号27(/BUSY)が「Hi−Z」になる。これまで、機能モジュール20−2のビジー信号27(/BUSY)が「L」であることで、ビジー信号線42(/BUSY)を「L」に引き込んでいた。しかし、機能モジュール20−2の初期化の完了とともに「L」に引き込まなくなり、ビジー信号線42(/BUSY)が「L」から「H」に移行する。これにより、すべての機能モジュール20−1〜20−nのビジー信号27(/RST)が「Hi−Z」に移行し、ビジー信号線42(/BUSY)が「L」から「H」に移行する。そして、すべての機能モジュール20−1〜20−nのイネーブル信号212(/EN)がネゲートからアサートに移行して、すべての機能モジュール20−1〜20−nが動作状態になる。

【0058】

また、時刻t4において、ビジー信号線42(/BUSY)が「L」から「H」に移行すると、CPU10の初期化信号11(/RST)が「L」から「H」に移行し、アサートからネゲートになる。そして、CPU10が停止状態から動作状態に移行する。

これにより、情報処理装置1が動作可能な状態になる。

【0059】

以上説明したように、複数の機能モジュール20−1〜20−nを備える第2の実施の形態の情報処理装置1では、初期化信号送信ユニット50からの初期化信号51(/RST)がアサートになる(図6の時刻t1)と、CPU10および機能モジュール20−1〜20−nが並行して停止状態になり、初期化信号51(/RST)がネゲートになる(時刻t2)と、機能モジュール20−1〜20−nの初期化が並行して開始される。そして、すべての機能モジュール20−1〜20−nの初期化が完了するタイミング(時刻t4)で、CPU10および機能モジュール20−1〜20−nが停止状態から動作状態に移行する。

【0060】

機能モジュール20−1〜20−nは、それぞれが実行部21、初期化部22、不揮発性メモリ23を備えているので、初期化信号受信端子26の初期化信号51(/RST)がネゲートからアサートになると、動作状態から停止状態に移行し、初期化信号51(/RST)がアサートからネゲートになるとそれぞれが個別に初期化を実行する。すなわち、機能モジュール20−1〜20−nの初期化は、CPU10の制御を必要とせず、並行して行われる。

一方、機能モジュール20−1〜20−nのそれぞれが初期化部22と実行部21を初期化するデータを保持する不揮発性メモリ23とを備えない場合には、機能モジュール20−1〜20−nのそれぞれの初期化は、ソフトウエア処理によりCPU10がシーケンシャル(順)に行うことになる。

すなわち、第2の実施の形態の情報処理装置1は、機能モジュール20−1〜20−nが初期化部22および不揮発性メモリ23を備えず、初期化をソフトウエア処理により順に行う情報処理装置1に比べ、初期化を短い時間で行うことができる。

【0061】

そして、第2の実施の形態の情報処理装置1では、ビジー信号線42(/BUSY)がネゲートになることにより、最も初期化の所要時間が長い機能モジュール20−x(1≦x≦nの整数)の初期化の完了とともに、CPU10が動作状態になる。このことにより、機能モジュール20−1〜20−nの初期化終了とCPU10の動作開始との間に不要な待ち時間(オーバヘッド)が生じることを抑制している。

一方、機能モジュール20−1〜20−nのそれぞれの初期化の終了をCPU10から問い合わせ(ポーリング)する場合には、機能モジュール20−xの初期化が終了してから、CPU10がポーリングを実行するまでの時間が不要な待ち時間(オーバヘッド)となってしまう。

すなわち、第2の実施の形態の情報処理装置1では、機能モジュール20−1〜20−nは並行して初期化が行われるとともに、機能モジュール20−1〜20−nの初期化の終了とともにCPU10が動作状態になる。よって、初期化信号51(/RST)がアサートになってから動作可能になるまでの立ち上がり時間が短い。

【0062】

なお、初期化信号51(/RST)および不揮発性メモリ23の保持するデータについては、第1の実施の形態で説明したのと同様であるので説明を省略する。

【0063】

(画像形成装置100)

次に、第2の実施の形態の情報処理装置1を画像形成装置100の制御部として構成する場合を説明する。

図7は、画像形成装置100の構成の一例を示す図である。

画像形成装置100は、制御部としての情報処理装置1と、ボタンなどユーザが指示を与えるためのUI(ユーザインターフェイス)部120、プリンタなどの画像形成部130、スキャナなどの画像読取部140、通信回線200(後述する図8参照)とデータなどの送受信を行う送受信部150を備えている。

【0064】

そして、制御部としての情報処理装置1は、4つの機能モジュール20−1〜20−4を備えている。機能モジュール20−1はUI部120を制御する機能を有するUI制御モジュール、機能モジュール20−2は画像形成部130を制御する機能を有する画像形成制御モジュール、機能モジュール20−3は画像読取部140を制御する機能を有する画像読取制御モジュール、機能モジュール20−4は送受信部150を制御する機能を有する送受信制御モジュールである。画像形成装置100の説明においては、機能モジュール20−1〜20−4を、それぞれUI制御モジュール20−1、画像形成制御モジュール20−2、画像読取制御モジュール20−3、送受信制御モジュール20−4と読み替える。

【0065】

UI部120はUI制御モジュール20−1に、画像形成部130は画像形成制御モジュール20−2に、画像読取部140は画像読取制御モジュール20−3に、送受信部150は送受信制御モジュール20−4に、それぞれデータ、命令などを送受信可能に接続されている。

【0066】

UI部120は、例えばボタンやタッチパネルなどで構成された入力機器であって、ユーザからの指示が入力される。そして、UI制御モジュール20−1は、UI部120に入力されたユーザの指示をCPU10に送信し、CPU10からの命令を受信し、UI部120がユーザの指示に対応した応答(入力画面などの切り替え)をするように制御する。

画像形成部130は、LEDなどにより感光体ドラムに潜像を書き込み、潜像をトナーで現像して紙などの記録材に転写する方式のプリンタでもよく、インクジェットなどで記録材に像を形成する方式のプリンタであってもよい。そして、画像形成制御モジュール20−2は、メインメモリ30内の画像データを画像形成部130に送信したり、画像形成部130から動作状態に関するデータを受信してCPU10に送信したりする。

画像読取部140は、画像が記録された記録材に対向させた受光素子アレイをスキャンさせる方式の画像読取機器であってもよく、CCDなどの撮像素子で画像を読み取る方式の撮像機器であってもよい。そして、画像読取制御モジュール20−3は、CPU10と画像読取部140との間にあって、CPU10から画像読取部140の読み取り条件などを設定するデータを受信して画像読取部140に送信したり、画像読取部140が読み取った画像データを受信してメインメモリ30に送信したりする。

送受信部150は、通信回線200を介してコンピュータ300またはファクシミリ装置400から送信された画像などのデータを受信する(後述する図8参照)。送受信制御モジュール20−4は、送受信部150が受信したデータをCPU10やメインメモリ30に送信する。また、送受信部150は、通信回線200に接続されたコンピュータ300またはファクシミリ装置400に、画像読取部140が読み取った画像などのデータを、送受信制御モジュール20−4を介して送信する。

【0067】

図8は、画像形成装置100と通信回線200に接続された機器との関係を説明した図である。

画像形成装置100は、送受信部150を介して、インターネット、電話網などの通信回線200に接続されている。そして、通信回線200には、コンピュータ300、ファクシミリ装置400、サーバ500などが接続されている。

【0068】

図7および図8を参照して、画像形成装置100の基本的な動作を説明する。

画像形成装置100は、画像読取部140から読み取った画像を、画像形成部130により記録材に印刷する。

また、画像形成装置100は、通信回線200を介して、画像形成装置100の外部に置かれたコンピュータ300、ファクシミリ装置400またはサーバ500から送信された画像などのデータを画像形成部130により記録材に印刷する。

一方、画像形成装置100は、画像読取部140が読み取った画像などのデータを、送受信部150から通信回線200を介して画像形成装置100の外部に置かれたコンピュータ300および/またはファクシミリ装置400に送信する。

【0069】

このような画像形成装置100は、使用されないときは通電されていないことが好ましい。例えば、電源からの電力の供給が全くない完全停止状態または節電のために一部の機能を停止させた待機(スリープ)状態に設定される。そして、使用しようとするときに、これらの完全停止状態または待機状態から、速やかに動作可能(動作状態)になることが望ましい。また、使用している間に、不具合が認められたとき、速やかに初期(リセット)状態に設定されることが望ましい。

このため、図7に示すように、第2の実施の形態における情報処理装置1を、画像形成装置100の制御部とすると、UI制御モジュール20−1、画像形成制御モジュール20−2、画像読取制御モジュール20−3、送受信制御モジュール20−4は、初期化信号51(/RST)を並行して受信し(アサートになり)、初期化信号51(/RST)が解除される(ネゲートになる)と並行して実行部21の初期化を実行するので、順に初期化がされる場合に比べ、初期化信号51(/RST)を受信してから(アサートになってから)短い時間で動作可能な状態になる。

【0070】

[第3の実施の形態]

第1の実施の形態および第2の実施の形態の情報処理装置1では、機能モジュール20(20−1〜20−n)が不揮発性メモリ23を備えていた。

第3の実施の形態では、機能モジュール20(20−1〜20−n)が不揮発性メモリ23を備えず、機能モジュール20(20−1〜20−n)の外部に不揮発性メモリ63を備えている。

【0071】

(情報処理装置1)

図9は、第3の実施の形態が適用される情報処理装置1の全体構成の一例を示した図である。

第3の実施の形態の情報処理装置1では、CPU10、機能モジュール60−1〜60−n、メインメモリ30、不揮発性メモリ63および初期化信号送信ユニット50を備えている。不揮発性メモリ63は、バス40にデータが送受信可能なように接続されている。

不揮発性メモリ63を除いて、他の構成は、第1の実施の形態の情報処理装置1と同様であるので、説明を省略する。

【0072】

図10は、機能モジュール60−1〜60−nの構成の一例を示した図である。

機能モジュール60−1〜60−nは、図2に示した第1の実施の形態の機能モジュール20から不揮発性メモリ23を除いた構成である。そして、実行部21および初期化部22がバス40にデータなどを入出力可能に接続されている。

他の構成は、第1の実施の形態における機能モジュール20と同様であるので、詳細な説明を省略する。

なお、機能モジュール60−1〜60−nをそれぞれ区別しないときは、機能モジュール60と表記する。

【0073】

次に、図9および図10を参照して、機能モジュール60の動作を説明する。

第3の実施の形態の機能モジュール60は、第1の実施の形態で説明した図3のフローチャートのステップ103の初期化部22による実行部21の初期化の手順が異なる。

第1の実施の形態で説明した機能モジュール20では、初期化部22は機能モジュール20の不揮発性メモリ23から実行部21の初期化に用いるデータを読み出して、実行部21を初期化していた。

これに対して、第3の実施の形態における機能モジュール60−1〜60−nでは、バス40に接続された不揮発性メモリ63から、機能モジュール60−1〜60−nのそれぞれの実行部21を初期化するデータを、バス40を介して読み出す。このため、機能モジュール60−1〜60−nの初期化部22は、バス40に接続されている。

なお、不揮発性メモリ63は、機能モジュール60−1〜60−nのそれぞれに対応するデータを異なるアドレスの領域に保持し、アドレスによってデータを選択するようになっている。

【0074】

上記した事項を除くと、第3の実施の形態における情報処理装置1は、第2の実施の形態で説明したのと同様であるので、説明を省略する。

【0075】

なお、図9では、情報処理装置1はn個の機能モジュール60−1〜60−nを備えるとしたが、第1の実施の形態の情報処理装置1と同様に1個の機能モジュール60を備えてもよい。

そして、すべての機能モジュール60−1〜60−nの実行部21を初期化するデータを不揮発性メモリ63に保持するとしたが、一部の機能モジュール60であってもよい。また、機能モジュール60を複数の組に分け、それぞれの組に対応した複数の不揮発性メモリ63を備えてもよい。

そして、不揮発性メモリ23を備えた機能モジュール20(図2参照)と不揮発性メモリ23を備えない機能モジュール60とを混在させてもよい。

【0076】

さらに、図9のメインメモリ30に破線で示すように、メインメモリ30が不揮発性メインメモリ31と揮発性メインメモリ32とで構成され、不揮発性メインメモリ31のすべてまたは一部を、機能モジュール60−1〜60−nの実行部21を初期化するデータを保持する不揮発性メモリ63としてもよい。

【0077】

ここで、不揮発性メインメモリ31がオペレーションシステム(OS)、プログラム、テキスト、定数、変数などを保持し、揮発性メインメモリ32が作業領域(ワークエリア)として一時的に使用するデータなどを保持すると、情報処理装置1をオフにしたのち再びオンになったとき、OS、プログラムなどを再度ロードする必要がない。よって、情報処理装置1は、短い時間で動作状態になる。

なお、OSを必要としない場合もある。

【0078】

また、メインメモリ30が不揮発性メインメモリ31で構成され、揮発性メインメモリ32を備えないとしてもよい。

なお、不揮発性メインメモリ31は、前述した高速な読み書きができ、書き換え回数の制限が小さい不揮発性記憶素子(MRAM、FeRAM、PRAM、ReRAM等)で構成されているのが好ましい。

また、第3の実施の形態における情報処理装置1を制御部として、第2の実施の形態で説明した画像形成装置に用いてもよい。

【0079】

第3の実施の形態の情報処理装置1では機能モジュール60−1〜60−nに不揮発性メモリ23を含まないことにより、機能モジュール60−1〜60−nが製造しやすい。

【0080】

[第4の実施の形態]

第1の実施の形態、第2の実施の形態、第3の実施の形態における情報処理装置1(図1、図5、図9)では、機能モジュール20(または60)のビジー信号(/BUSY)が、CPU10の初期化信号受信端子11(/RST)に送信されていた。このため、図4、図6のタイミングチャートに示したように、すべての機能モジュール20の実行部21の設定が完了したのちに、CPU10が動作状態になる。

ここで、CPU10も初期化が必要な場合には、機能モジュール20の実行部21の初期化が完了してから、CPU10の初期化を行うことになる。すなわち、機能モジュール20の実行部21の初期化とCPU10の初期化とがシーケンシャルで(順に)行われることになる。

これに対して、第4の実施の形態の情報処理装置1では、CPU10の初期化と機能モジュール20の実行部21の初期化とを並行して行う。

【0081】

(情報処理装置1)

図11は、第4の実施の形態が適用される情報処理装置1の全体構成の一例を示した図である。

情報処理装置1は、CPU10、機能モジュール20、メインメモリ30、バス40、初期化信号送信ユニット50を備えている。

CPU10は、初期化信号送信ユニット50からの初期化信号51(/RST)を受信する初期化信号受信端子11(/RST)と、ビジー信号を送信するビジー信号送信端子12(/BUSY)とを備えている。

【0082】

そして、初期化信号送信ユニット50の初期化信号送信端子51(/RST)が、初期化信号線41を介して、CPU10の初期化信号受信端子11(/RST)と、機能モジュール20の初期化信号受信端子26(/RST)とに並列に接続されている。

さらに、CPU10のビジー信号送信端子12(/BUSY)と、機能モジュール20のビジー信号送信端子27(/BUSY)とが、許可信号線の一例としてのビジー信号線42に接続されている。そして、ビジー信号線42は、電流制限抵抗Rを介して電源電位Vddに接続されている。

【0083】

図12は、第4の実施の形態におけるCPU10の構成を示した図である。

CPU10は、命令処理部や読み出し/書き込み実行部や算術演算部などからなり、命令を実行する命令実行手段の一例としての命令実行部13、命令実行部13を初期状態に設定する他の初期化手段の一例としての初期化部14、命令実行部13を初期状態に設定するためのデータを保持する不揮発性メモリ15を備えている。さらに、CPU10は、オープンドレインバッファ16とインバータ17とを備えている。

【0084】

命令実行部13、初期化部14は、シーケンサ、カウンタ、レジスタなどを含む論理回路から構成されている。命令実行部13は、初期化信号受信端子131(/RST)およびイネーブル信号受信端子132(/EN)を備えている。初期化部14は、初期化信号受信端子141(/RST)およびビジー信号送信端子142(/BUSY)を備えている。

不揮発性メモリ15、オープンドレインバッファ16、インバータ17は、図2の不揮発性メモリ23、オープンドレインバッファ24、インバータ25と同様であるので説明を省略する。

【0085】

CPU10における接続関係を説明する。

CPU10の命令実行部13と初期化部14とは、データ、アドレス、命令などを双方向に転送可能に接続されている。同様に、初期化部14と不揮発性メモリ15とは、データ、アドレス、命令などを双方向に転送可能に接続されている。

【0086】

そして、CPU10の初期化信号受信端子11(/RST)は、命令実行部13の初期化信号受信端子131(/RST)と初期化部14の初期化信号受信端子141(/RST)とに並列に接続されている。つまり、初期化信号送信ユニット50から送信された初期化信号51(/RST)は、命令実行部13と初期化部14に並列に送信される。

一方、初期化部14のビジー信号送信端子142(/BUSY)は、オープンドレインバッファ16を介して、CPU10のビジー信号送信端子12(/BUSY)に接続されている。

また、オープンドレインバッファ16の出力端子は、インバータ17を介して命令実行部13に設けられたイネーブル信号受信端子132(/EN)に接続されている。つまり、初期化部14から発信されたビジー信号142(/BUSY)がアサート(「L」)のときは、オープンドレインバッファ16の出力端子が「L」であって、CPU10のビジー信号12(/BUSY)がアサート(「L」)になる。また、ビジー信号142(/BUSY)がネゲート(「H」)のときは、オープンドレインバッファ16の出力端子は「Hi−Z」であって、CPU10のビジー信号12(/BUSY)は「Hi−Z」になる。

なお、CPU10では、命令実行部13がバス40と接続されている。

【0087】

以上説明したように、第4の実施の形態におけるCPU10の構成は、図2で説明した機能モジュール20と同様であって、機能モジュール20の実行部21を命令実行部13に、初期化部22を初期化部14に、不揮発性メモリ23を不揮発性メモリ15に、オープンドレインバッファ24をオープンドレインバッファ16に、インバータ25をインバータ17に置き換えたものである。他の符号についても同様である。よって、初期化信号送信ユニット50から送信される初期化信号51(/RST)がアサートになってからのCPU10の初期化は、図3に示した機能モジュール20の初期化と同様である。よって、詳細な説明を省略する。

一方、機能モジュール20は、第1の実施の形態において図2で示した構成と同様である。

【0088】

次に、第4の実施の形態における情報処理装置1の動作を説明する。

図13は第4の実施の形態における情報処理装置1の動作を説明するタイミングチャートである。ここでは、第1の実施の形態の図4と同様に、時刻t1において初期化信号送信ユニット50が送信する初期化信号51(/RST)がアサートになる場合について説明する。

図13では、初期化信号51(/RST)、ビジー信号線42(図13の説明では/BUSYを付記する。)の出力レベル、機能モジュール20の実行部21の状態およびビジー信号27(/BUSY)の出力レベル、CPU10の命令実行部13の状態およびビジー信号12(/BUSY)の出力レベルを示している。

なお、時刻t1から時刻t4へと時間が経過するとする。この時刻t1〜時刻t4は図4と同じである。

【0089】

時刻t1の直前の状態は、CPU10の命令実行部13および機能モジュール20の実行部21は動作状態にある。すなわち、初期化信号送信ユニット50からCPU10の初期化信号受信端子11ならびに機能モジュール20の初期化信号受信端子26(/RST)に送信される初期化信号51(/RST)、CPU10の送信するビジー信号12(/BUSY)ならびに機能モジュール20の送信するビジー信号27(/BUSY)はともに「Hi−Z」である。しかし、ビジー信号線42(/BUSY)は、電流制限抵抗Rを介して電源電位Vddに接続されているので、「H」である。これにより、CPU10におけるイネーブル信号132(/EN)ならびに機能モジュール20におけるイネーブル信号212(/EN)はアサートである。

すなわち、時刻t1の直前においては、CPU10の命令実行部13および機能モジュール20の実行部21は動作状態にあって、機能モジュール20の初期化部22は停止状態にある。

【0090】

さて、時刻t1で、初期化信号送信ユニット50からの初期化信号51(/RST)がネゲートからアサート(「H」から「L」)になると、CPU10の命令実行部13および機能モジュール20の実行部21が動作状態から停止状態に移行する。

そして、CPU10のビジー信号12(/BUSY)および機能モジュール20のビジー信号27(/BUSY)がネゲートからアサート(「Hi−Z」から「L」)になる。さらに、ビジー信号線42が「H」から「L」になる。

【0091】

次に、時刻t2において初期化信号51(/RST)がアサートからネゲート(「L」から「H」)になると、CPU10における初期化部14による命令実行部13の初期化と機能モジュール20における初期化部22による実行部21の初期化とが並行して開始される。

そして、時刻t3で、機能モジュール20の初期化が完了すると、図2において説明したように、機能モジュール20の初期化部22のビジー信号送信端子222(/BUSY)がネゲート(「H」)になる。これにより、機能モジュール20のビジー信号27(/BUSY)が「Hi−Z」になる。しかし、CPU10の命令実行部13は初期化が完了していないため、ビジー信号12(/BUSY)は「L」に維持される。このため、ビジー信号線42が「L」に維持されたままとなる。すると、機能モジュール20のイネーブル信号212(/EN)も「H」でネゲートを維持する。

つまり、機能モジュール20の実行部21は、時刻t3で初期化が完了するが、イネーブル信号212(/EN)がネゲートであるので、時刻t3から後述する時刻t4までの間は停止状態にある。

【0092】

そして、時刻t4において、CPU10の命令実行部13の初期化が完了すると、CPU10の初期化部14のビジー信号142(/BUSY)が「L」から「H」になる。そして、CPU10のビジー信号12(/BUSY)が「L」から「Hi−Z」になる。すると、CPU10のビジー信号12(/BUSY)および機能モジュール20のビジー信号27(/BUSY)がともに「Hi−Z」になって、ビジー信号線42(/BUSY)が「H」になる。

これにより、CPU10の命令実行部13のイネーブル信号132(/EN)および機能モジュール20の実行部21のイネーブル信号212(/EN)がネゲートからアサート(「H」から「L」)になる。そして、CPU10の命令実行部13および機能モジュール20の実行部21が停止状態から動作状態に移行する。すなわち、情報処理装置1が動作可能な状態になる。

【0093】

ここでは、機能モジュール20の実行部21の初期化の所要時間が、CPU10の命令実行部13の初期化の所要時間より短いとしたが、逆の場合であっても同様である。

すなわち、CPU10または機能モジュール20の一方が初期化中であると、ビジー信号線42は、「L」に引き込まれた状態となって、初期化が終わっていても他方は停止状態となる。そして、CPU10および機能モジュール20の両方の初期化が完了したタイミングで、CPU10および機能モジュール20の両方が並行して停止状態から動作状態に移行する。

【0094】

第4の実施の形態の情報処理装置1では、CPU10の命令実行部13の初期化と機能モジュール20の実行部21の初期化とが並行して実施されるので、機能モジュール20の実行部21の初期化の完了後にCPU10の初期化が行われる場合に比べ、情報処理装置1の初期化信号51(/RST)がネゲートになってから動作可能になるまでの所要時間が短くなる。

また、CPU10の初期化と機能モジュール20の実行部21の初期化とのうち、所要時間が長い方の初期化が完了すると、ビジー信号線42(/BUSY)が「L」から「H」になって、CPU10および機能モジュール20の動作が開始する。よって、CPU10の初期化と機能モジュール20の実行部21の初期化の完了と、CPU10および機能モジュール20の動作の開始との間に、不要な待ち時間(オーバヘッド)が発生するのが抑制される。

【0095】

なお、第3の実施の形態と同様に、機能モジュール20が不揮発性メモリ23を備えない機能モジュール60であって、バス40にデータなどが入出力可能に接続された不揮発性メモリ63を備えていてもよい。また、メインメモリ30に不揮発性メインメモリ31を備えて、不揮発性メモリ63と兼ねていてもよい。

【0096】

[第5の実施の形態]

第4の実施の形態の情報処理装置1は、機能モジュール20を1つ備えていた。

第5の実施の形態の情報処理装置1では、第2の実施の形態と同様に、複数の機能モジュール20−1〜20−nを備えている。

【0097】

(情報処理装置1)

図14は、第5の実施の形態が適用される情報処理装置1の全体構成の一例を示した図である。

情報処理装置1は、CPU10、機能モジュール20−1〜20−n、メインメモリ30、バス40、初期化信号送信ユニット50を備えている。

CPU10は、第4の実施の形態において図12に示した構成と同様である。

機能モジュール20は、第1の実施の形態において図2に示した構成と同様である。

【0098】

そして、初期化信号送信ユニット50の初期化信号送信端子51(/RST)が、初期化信号線41に接続されている。そして、CPU10の初期化信号受信端子11(/RST)と、機能モジュール20−1〜20−nの初期化信号受信端子26(/RST)とが並列に初期化信号線41に接続されている。

さらに、CPU10のビジー信号送信端子12(/BUSY)と、機能モジュール20−1〜20−nのビジー信号送信端子27(/BUSY)とが、ビジー信号線42に接続されている。そして、ビジー信号線42は、電流制限抵抗Rを介して、電源電位Vddに接続されている。

【0099】

次に、第5の実施の形態における情報処理装置1の動作を説明する。

図15は第5の実施の形態における情報処理装置1の動作を説明するタイミングチャートである。ここでは、第2の実施の形態の図6と同様に、時刻t1において初期化信号送信ユニット50が初期化信号51(/RST)をネゲートからアサートにする場合について説明する。

図15では、初期化信号51(/RST)、ビジー信号線42(図15の説明では/BUSYを付記する。)、機能モジュール20−1〜20−nの実行部21の状態およびビジー信号27(/BUSY)の出力レベル、CPU10の命令実行部13の状態およびビジー信号12(/BUSY)の出力レベルを示している。

なお、時刻t1から時刻t4へと時間が経過するとする。この時刻t1〜時刻t4は図6と同じである。

【0100】

時刻t1の直前の状態は、第1の実施の形態と同様に、CPU10の命令実行部13および機能モジュール20−1〜20−nのそれぞれの実行部21は動作状態にある。

すなわち、初期化信号送信ユニット50からの初期化信号51(/RST)はネゲート(「H」)であるので、CPU10の初期化信号11(/RST)ならびに機能モジュール20−1〜20−nの初期化信号26(/RST)は「H」である。すると、CPU10の初期化部14のビジー信号12(/BUSY)および機能モジュール20−1〜20−nのそれぞれの初期化部22のビジー信号27(/BUSY)は、「Hi−Z」になっている。

ビジー信号線42(/BUSY)は、電流制限抵抗Rを介して電源電位Vddに接続されているので、CPU10におけるイネーブル信号132(/EN)(図12参照)および機能モジュール20−1〜20−nにおけるイネーブル信号212(/EN)(図2参照)は「L」(アサート)になっている。

すなわち、時刻t1の直前においては、CPU10の命令実行部13および機能モジュール20−1〜20−nのそれぞれの実行部21は動作状態にあって、CPU10の初期化部14および機能モジュール20−1〜20−nの初期化部22は停止状態にある。

【0101】

さて、時刻t1で、初期化信号送信ユニット50からの初期化信号51(/RST)がネゲートからアサート(「H」から「L」)になる)と、CPU10の命令実行部13および機能モジュール20−1〜20−nの実行部21が動作状態から停止状態に移行する。

そして、CPU10のビジー信号12(/BUSY)および機能モジュール20−1〜20−nのそれぞれのビジー信号27(/BUSY)が「Hi−Z」から「L」になる。そして、ビジー信号線42が「H」から「L」になる。すると、CPU10におけるイネーブル信号132(/EN)および機能モジュール20−1〜20−nにおけるイネーブル信号212(/EN)はアサートからネゲート(「L」から「H」)に移行する。これにより、CPU10の命令実行部13および機能モジュール20−1〜20−nのそれぞれの実行部21は動作状態から停止状態になる。

【0102】

次に、時刻t2において初期化信号(/RST)が解除される(ネゲート(「L」から「H」)になる)と、CPU10の命令実行部13の初期化と機能モジュール20−1〜20−nにおける初期化部22による実行部21の初期化とが並行して開始される。

そして、時刻t3で、初期化の所要時間が最も短い機能モジュール20−1の初期化が完了すると、図2において説明したように、機能モジュール20−1の初期化部22のビジー信号222(/BUSY)がネゲートになる。これにより、機能モジュール20−1のビジー信号27(/BUSY)が「L」から「Hi−Z」になる。しかし、CPU10および他の機能モジュール20−2〜20−nは初期化が完了していないため、CPU10のビジー信号12(/BUSY)および機能モジュール20−2〜20−nのビジー信号27(/BUSY)は「L」に維持される。このため、ビジー信号線42(/BUSY)は「L」に維持されたままとなる。すると、機能モジュール20−1のイネーブル信号212(/EN)も「H」でネゲートを維持する。

つまり、機能モジュール20−1の実行部21は、時刻t3で初期化が完了するが、イネーブル信号222(/EN)がネゲートであるので、時刻t3から後述する時刻t4までの間は停止状態にある。

【0103】

そして、時刻t4において、設定時間の最も長い機能モジュール20−2の初期化が完了する。

なお、CPU10の命令実行部13は、時刻t3と時刻t4との間の時刻において、初期化が完了し、機能モジュール20−1と同様に停止状態になっている。他の機能モジュール20−3〜20−nも同様である。

【0104】

さて、設定時間の最も長い機能モジュール20−2の初期化が完了すると、CPU10のビジー信号12(/BUSY)および機能モジュール20−1〜20−nのいずれのビジー信号27(/BUSY)も「Hi−Z」となる。これにより、ビジー信号線42(/BUSY)が「L」から「H」になる。そして、CPU10のイネーブル信号132(/EN)および機能モジュール20−1〜20−nのそれぞれのイネーブル信号212(/EN)がアサートになる。これにより、CPU10および機能モジュール20−1〜20−nが停止状態から動作状態に移行する。すなわち、情報処理装置1が動作可能な状態になる。

【0105】

ここでは、機能モジュール20−1の実行部21の初期化の所要時間が最も短く、機能モジュール20−2の実行部21の初期化の所要時間が最も長いとした。CPU10の命令実行部13の初期化の所要時間が最も短くてもよく、最も長くてもよい。

すなわち、CPU10の命令実行部13または機能モジュール20−1〜20−nの実行部21いずれかが初期化中であると、ビジー信号線42(/BUSY)は、「L」に引き込まれた状態となっている。このため、CPU10または機能モジュール20−1〜20−nのいずれかの初期化が終わっていても停止状態となっている。そして、CPU10および機能モジュール20−1〜20−nのすべての初期化が完了した時点で、CPU10および機能モジュール20−1〜20−nのすべてが並行して動作状態に移行する。

【0106】

第5の実施の形態の情報処理装置1では、CPU10の命令実行部13の初期化と機能モジュール20−1〜20−nのそれぞれの実行部21の初期化とが並行して実施されるので、機能モジュール20−1〜20−nの実行部21のすべての初期化の完了後にCPU10の初期化が行われる場合に比べ、情報処理装置1が動作可能になるまでの所要時間(立ち上がり時間)が短くなる。

また、CPU10の命令実行部13の初期化と機能モジュール20−1〜20−nのそれぞれの実行部21の初期化とのうち、最も所要時間が長い初期化が完了すると、ビジー信号線42が「L」から「H」になる。これにより、CPU10および機能モジュール20−1〜20−nの動作が開始するので、不要な待ち時間(オーバヘッド)の発生が抑制されている。

【0107】

なお、第3の実施の形態と同様に、機能モジュール20−1〜20−nが不揮発性メモリ23を備えない機能モジュール60−1〜60−nであって、バス40にデータなどが入出力可能に接続された不揮発性メモリ63を備えていてもよい。また、メインメモリ30に不揮発性メインメモリ31を備えて、不揮発性メモリ63と兼ねていてもよい。

【0108】

さらに、第5の実施の形態の情報処理装置1を第2の実施の形態で示した画像形成装置100の制御部として用いてもよい。

【0109】

なお、第5の実施の形態の情報処理装置1において、CPU10のビジー信号送信端子12(/BUSY)をIOポート(不図示)に接続した構成としてもよい。CPU10のIOポートは、機能モジュール20−1〜20−nのIOポート(不図示)と接続されている。

初期化信号51(/RST)が解除された(アサートからネゲートになった)とき、CPU10がソフトウエアを起動する。そして、ソフトウエアの起動が完了すると、IOポートへのビジー信号(/BUSY)を解除(ネゲート)し、機能モジュール20−1〜20−nへのアクセスを許可すると同時に、ソフトウエアがIOポートのビジー信号(/BUSY)の状態を監視し、ビジー信号(/BUSY)が解除(ネゲート)されるのを確認してから機能モジュール20−1〜20−nを使用するソフトウエアを起動するように構成する。このようにすることで、ソフトウエアを起動する時間が短縮される。

【符号の説明】

【0110】

1…情報処理装置、10…CPU、13…命令実行部、14、22…初期化部、15、23、63…不揮発性メモリ、20、20−1〜20−n、60、60−1〜60−n…機能モジュール、21…実行部、16、24…オープンドレインバッファ、17、25…インバータ、30…メインメモリ、31…不揮発性メインメモリ、32…揮発性メインメモリ、40…バス、41…初期化信号線、42…ビジー信号線、50…初期化信号送信ユニット、100…画像形成装置、120…UI部、130…画像形成部、140…画像読取部、150…送受信部、200…通信回線、300…コンピュータ、400…ファクシミリ装置、500…サーバ

【特許請求の範囲】

【請求項1】

画像を記録材に形成する画像形成部と、

算術演算および論理演算を行う演算モジュールと、当該演算モジュールの演算結果に基づいて予め定められた機能を実行する実行手段と、初期化信号を受信すると当該実行手段による機能の実行を停止する停止手段と、当該初期化信号が解除されると当該実行手段を初期化する初期化手段とを備える機能モジュールと、

前記初期化信号を送信する初期化信号送信手段と

を備え、前記画像形成部を制御する制御部と

を備える画像形成装置。

【請求項2】

論理演算または算術演算を実行する演算モジュールと、

前記演算モジュールの演算結果に基づいて予め定められた機能を実行する実行手段と、初期化信号を受信すると当該実行手段による機能の実行を停止する停止手段と、当該初期化信号が解除されると当該実行手段を初期化する初期化手段とを備える機能モジュールと、

前記初期化信号を送信する初期化信号送信手段と

を備える情報処理装置。

【請求項3】

前記機能モジュールが、前記実行手段を初期化するためのデータを保持する記憶手段をさらに備えることを特徴とする請求項2に記載の情報処理装置。

【請求項4】

前記記憶手段が、MRAM、FeRAM、PRAM、ReRAM等の読み書き可能な不揮発性メモリであることを特徴とする請求項3に記載の情報処理装置。

【請求項5】

前記機能モジュールと前記演算モジュールとを接続するように設けられ、当該機能モジュールにおける前記実行手段の初期化が完了したことを当該演算モジュールに通報する通報信号線をさらに備えることを特徴とする請求項2ないし4のいずれか1項に記載の情報処理装置。

【請求項6】

前記機能モジュールの前記実行手段および前記演算モジュールは、当該機能モジュールが前記初期化信号を受信すると動作状態から停止状態に移行し、当該機能モジュールにおける当該実行手段の初期化が完了したことを前記通報信号線により通報されると停止状態から動作状態に移行することを特徴とする請求項5に記載の情報処理装置。

【請求項7】

前記実行手段が初期化によって設定される初期状態は、当該実行手段が初めて動作可能になったときの状態または当該実行手段の実行を再開するために実行が中断したときの状態であることを特徴とする請求項2ないし6のいずれか1項に記載の情報処理装置。

【請求項8】

前記演算モジュールが、命令を実行する命令実行手段と、前記初期化信号を受信すると当該命令実行手段を初期化する他の初期化手段とをさらに備え、

前記演算モジュールと前記機能モジュールとを接続するように設けられ、当該演算モジュールにおける前記命令実行手段の初期化が完了し、且つ当該機能モジュールの前記実行手段の初期化が完了したとき、当該演算モジュールおよび当該機能モジュールの動作を許可する許可信号線を

さらに備えることを特徴とする請求項2に記載の情報処理装置。

【請求項9】

予め定められた機能を実行する実行手段と、

初期化信号を受信すると前記実行手段の動作を停止する停止手段と、

前記初期化信号が解除されると前記実行手段を初期化する初期化手段と

を備える機能モジュール。

【請求項10】

前記実行手段を初期化するためのデータを保持する記憶手段をさらに備えることを特徴とする請求項9に記載の機能モジュール。

【請求項11】

前記記憶手段が、MRAM、FeRAM、PRAM、ReRAM等の読み書き可能な不揮発性メモリであることを特徴とする請求項10に記載の機能モジュール。

【請求項1】

画像を記録材に形成する画像形成部と、

算術演算および論理演算を行う演算モジュールと、当該演算モジュールの演算結果に基づいて予め定められた機能を実行する実行手段と、初期化信号を受信すると当該実行手段による機能の実行を停止する停止手段と、当該初期化信号が解除されると当該実行手段を初期化する初期化手段とを備える機能モジュールと、

前記初期化信号を送信する初期化信号送信手段と

を備え、前記画像形成部を制御する制御部と

を備える画像形成装置。

【請求項2】

論理演算または算術演算を実行する演算モジュールと、

前記演算モジュールの演算結果に基づいて予め定められた機能を実行する実行手段と、初期化信号を受信すると当該実行手段による機能の実行を停止する停止手段と、当該初期化信号が解除されると当該実行手段を初期化する初期化手段とを備える機能モジュールと、

前記初期化信号を送信する初期化信号送信手段と

を備える情報処理装置。

【請求項3】

前記機能モジュールが、前記実行手段を初期化するためのデータを保持する記憶手段をさらに備えることを特徴とする請求項2に記載の情報処理装置。

【請求項4】

前記記憶手段が、MRAM、FeRAM、PRAM、ReRAM等の読み書き可能な不揮発性メモリであることを特徴とする請求項3に記載の情報処理装置。

【請求項5】

前記機能モジュールと前記演算モジュールとを接続するように設けられ、当該機能モジュールにおける前記実行手段の初期化が完了したことを当該演算モジュールに通報する通報信号線をさらに備えることを特徴とする請求項2ないし4のいずれか1項に記載の情報処理装置。

【請求項6】

前記機能モジュールの前記実行手段および前記演算モジュールは、当該機能モジュールが前記初期化信号を受信すると動作状態から停止状態に移行し、当該機能モジュールにおける当該実行手段の初期化が完了したことを前記通報信号線により通報されると停止状態から動作状態に移行することを特徴とする請求項5に記載の情報処理装置。

【請求項7】

前記実行手段が初期化によって設定される初期状態は、当該実行手段が初めて動作可能になったときの状態または当該実行手段の実行を再開するために実行が中断したときの状態であることを特徴とする請求項2ないし6のいずれか1項に記載の情報処理装置。

【請求項8】

前記演算モジュールが、命令を実行する命令実行手段と、前記初期化信号を受信すると当該命令実行手段を初期化する他の初期化手段とをさらに備え、

前記演算モジュールと前記機能モジュールとを接続するように設けられ、当該演算モジュールにおける前記命令実行手段の初期化が完了し、且つ当該機能モジュールの前記実行手段の初期化が完了したとき、当該演算モジュールおよび当該機能モジュールの動作を許可する許可信号線を

さらに備えることを特徴とする請求項2に記載の情報処理装置。

【請求項9】

予め定められた機能を実行する実行手段と、

初期化信号を受信すると前記実行手段の動作を停止する停止手段と、

前記初期化信号が解除されると前記実行手段を初期化する初期化手段と

を備える機能モジュール。

【請求項10】

前記実行手段を初期化するためのデータを保持する記憶手段をさらに備えることを特徴とする請求項9に記載の機能モジュール。

【請求項11】

前記記憶手段が、MRAM、FeRAM、PRAM、ReRAM等の読み書き可能な不揮発性メモリであることを特徴とする請求項10に記載の機能モジュール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2013−6323(P2013−6323A)

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願番号】特願2011−139659(P2011−139659)

【出願日】平成23年6月23日(2011.6.23)

【出願人】(000005496)富士ゼロックス株式会社 (21,908)

【Fターム(参考)】

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願日】平成23年6月23日(2011.6.23)

【出願人】(000005496)富士ゼロックス株式会社 (21,908)

【Fターム(参考)】

[ Back to top ]