Fターム[5B054BB11]の内容

Fターム[5B054BB11]に分類される特許

1 - 20 / 20

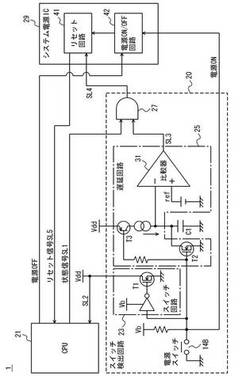

携帯情報端末

【課題】 リセット動作を制限する。

【解決手段】 携帯電話1は、アプリケーションプログラムを実行可能なCPU21と、電源をオンした状態とオフした状態とに切換える指示を受付けるための電源スイッチ14Bと、電源スイッチ14Bが所定時間閉ざされると、CPU21を再起動させるためのリセット信号を出力するリセット検出回路20とを備え、CPU21は、リセット可能な状態とリセット不可能な状態とのいずれかを示す状態信号SL1を出力し、リセット検出回路20は、状態信号SL1がリセット可能な状態を示すこことを条件に、ハイの信号S4(リセット信号)をリセット回路41に出力する論理積素子27を含む。リセット回路41は、リセット検出回路20からハイの信号S4(リセット信号)が入力されると、CPU21にローの信号SL5(リセット信号)を出力する。

(もっと読む)

電源制御回路及び電源制御方法

【課題】電源投入時に電源電位が安定するまでの待ち時間を改善する電源制御回路及び電源制御方法を提供する。

【解決手段】常時通電領域113と、少なくとも1つの電源遮断領域112とを有する半導体集積装置の電源制御回路200であって、検出部210と制御部220とを備える。検出部210は、電源遮断領域112の電源電位が、電源遮断領域の電源電位の安定を判定する下限の電源電位より低くなる回数をカウントする。そして、電源遮断領域112の電源電位が常時通電領域113の電源電位より高くなるときに、カウントした回数が増加していないことを検出する。制御部220は、検出部210がカウントした回数が増加していないことを検出した場合、電源遮断領域112のリセット状態を解除する。

(もっと読む)

シリアル通信装置及びその制御方法

【課題】内部回路との間で所定の同期クロックを用いて通信を行う送受信回路と、入力される基準クロックに基づいて上記同期クロックを発生するPLL回路とを備えたインターフェース回路を備えたシリアル通信装置において、インターフェース回路及び内部回路の誤動作を防止する

【解決手段】遅延回路5は、基準クロックREFCLKの周波数が100MHzで安定した後に発生されるリセット信号PERST#を、所定の遅延時間Δtだけ遅延させて内部リセット信号PERST2を発生し、リンクコントローラ31に出力する。PHY回路2は、リセット信号PERST#に応答してリセットされ、リンクコントローラ31は、内部リセット信号PERST2に応答してリセットされる。また、遅延時間Δtは、PLL回路23の回路仕様に基づいて予め計算されたロックアップ時間より長く設定される。

(もっと読む)

リセット装置

【課題】 従来より安価で簡単な回路構成で、確実に制御手段にリセット動作を実行させることができるリセット装置を提供する。

【解決手段】 制御手段にリセット信号を供給するリセット装置であって、ユーザによって操作可能である第1操作部及び第2操作部と、該第1操作部及び第2操作部が所定時間以上継続して同時に操作されているか否かを検出する検出部と、リセット信号を該制御手段に供給するリセット信号生成部とを備え、該第1操作部及び第2操作部が所定時間以上継続して同時に操作され、その後、同時に操作されなくなったときに、該リセット信号生成部がリセット信号を該制御手段に供給する。

(もっと読む)

制御装置の初期化方法

【課題】制御装置において初期化処理する回路の初期設定値に変更が必要になった場合にファームウェア自体を変更せずに初期化処理を変更可能とし、また、保存されている初期設定値に不測の誤りが生じた場合でも誤った設定値で該回路を初期化してしまうことを防ぐことができる制御装置の初期化方法を提供する。

【解決手段】制御装置の初期化方法は、初期化対象回路を初期化するための初期設定プログラムが記憶された第1の記憶部と前記初期化対象回路の初期設定値が記憶された第2の記憶部とを具備し、初期設定プログラムを実行するにあたり前記第2の記憶部から前記誤り検出符号を読み出して前記初期設定値の誤りの有無を検出し、誤りが検出されない場合に前記初期設定値を用いて前記初期化対象回路の初期化を行い、誤りが検出された場合に前記別の初期設定値を用いて前記初期化対象回路の初期化を行う。

(もっと読む)

リセット装置

【課題】 ユーザの誤操作によって制御手段が強制的にリセット動作を実行してしまうことを防止するリセット装置を提供すること。

【解決手段】 第1操作部2が操作され、リセット制御部に開始信号が供給されている間に、第2操作部5が操作され、パルス信号がリセット制御部に供給されることにより、リセット制御部は、パルス信号のハイレベルの回数をカウントする。ハイレベルの回数が所定回数に達すると、リセット制御部は、リセット信号をマイコン10に供給する。従って、第1操作部2、第2操作部5の少なくとも一方が操作されないとマイコン10にリセット信号が供給されないので、マイコン10をリセット動作させる意思がないにもかかわらず、誤操作によってマイコン10がリセット動作することを防止することができる。

(もっと読む)

リセット回路および電源制御用半導体集積回路

【課題】電源電圧が所定電圧より低い状態から上昇した場合に誤ってリセット解除信号が出力されてしまうのを回避することができるリセット回路およびそれを内蔵した電源制御用ICを提供する。

【解決手段】電源電圧に比例した電圧と参照電圧とを比較する電圧比較手段(CMP0)と、該電圧比較手段によって電源電圧が所定の電位以上になったことが検出された場合にその検出タイミングを遅らせて後段に伝える第1の遅延手段(DLY1)と、前記電圧比較手段によって電源電圧が所定の電位以下になったことが検出された場合にその検出タイミングを遅らせて後段に伝える第2の遅延手段(DLY2)と、を備えたリセット回路において、前記第2の遅延手段は、該遅延手段内部のノードの電位を論理しきい値で判定する第2判定回路(INV3)と、前記ノードに接続され電源電圧の上昇時に該ノードの電位を引き上げるプルアップ手段(SW3,GT1)とを設けるようにした。

(もっと読む)

リセット信号監視回路

【課題】バッファ回路の特性に因らず誤出力を防止し、また、回路構成の相違による異常出力信号がロックされることを防止する。

【解決手段】異なるリセット電圧を出力する第1、第2のリセット信号発生回路11、12と、出力動作がロックされる第1、第2のバッファ回路13,14を設け、第1のリセット信号発生回路11で発生したリセット電圧は、タイマー回路15に入力され、このタイマー回路15は、リセット信号が一定時間継続しているかを監視し、検出する。リセット信号が継続されていたなら、第2のバッファ回路14を介してフォトカプラ16からCPUが動作できない場合の装置異常の出力信号を送出する。第2のバッファ回路14は、制御端子14aのリセット電圧で出力動作がロックされ、電源入り切り時における電圧変動では、第2のリセット信号発生回路12はリセット電圧を発生しない。このため、第2のバッファ回路14はロックされない。

(もっと読む)

リセット回路およびリセット回路を備えたシステム

【課題】 パワーオン時にリセット信号を正常に出力する。

【解決手段】 パワーオン検出回路において第1分圧電圧が生成される第1接続ノードは、パワーダウン検出信号の活性化中に第2電源線に接続される。パワーダウン検出信号の非活性化タイミングは、パワーオン検出信号の活性化タイミングより早く設定される。このため、パワーオン期間の前半に、ゲートが第1接続ノードに接続される第1トランジスタを確実にオフでき、パワーオン検出信号がパワーオン期間に活性化されることを防止できる。また、第1トランジスタに流れるリーク電流を削減できる。パワーオン期間の後半には、第1分圧回路により生成される第1分圧電圧を用いてパワーオン検出信号を確実に生成できる。この結果、パワーオン時の電源電圧の挙動に関わりなく、リセット回路を誤操作することなく動作させ、リセット信号を正常に出力できる。

(もっと読む)

半導体集積回路

【課題】低消費電力状態の解除に伴う誤動作を解消する。

【解決手段】動作電源の供給と遮断が制御される内部回路と、動作モードに応じて記内部回路に対する動作電源の供給と遮断を制御する電源制御回路(30)とを有する。電源制御回路は、記憶回路(35,36)及び電源制御シーケンス回路(39)を有する。記憶回路は動作電源の供給と遮断を切換え指示する切換え指示データと動作電源の遮断及び解除の動作モードを決める低消費電力モードデータを入力して保持する。電源制御シーケンス回路は、前記記憶回路が保持する切換え指示データと低消費電力モードデータを参照して動作電源の遮断と供給の遷移制御を行い、低消費電力モードデータに応ずる動作電源の供給遮断状態において前記切換え指示データにより動作電源の供給遮断状態を解除するとき、動作電源の供給を受ける内部回路の動作が保証されるまで前記低消費電力モードデータの新たな参照を抑制する。

(もっと読む)

電源監視制御回路及びそれを用いた画像形成装置

【課題】 それぞれ別々の電源電圧で動作する少なくとも2つのICとリセット生成手段とが接続しているリセット回路において、一方の電源に異常が発生した場合でも、リセットとリセット解除との無限ループに陥ることのないリセット回路を提供する。

【解決手段】 電源監視制御回路は、電源電圧監視回路105から第2制御手段102を稼働する電源3.3Vの電源電圧の異常を示す信号が入力された場合、第1制御手段101が、リセット信号生成手段103に対して、ウォッチドッグタイマ機能を無効とし、リセット信号を出力しないように制御するウォッチドッグタイマ制御信号を出力することを特徴とする。

(もっと読む)

電子機器及び電子機器の再起動方法

【課題】部品や回路ブロックに動作異常が発生しても、複雑な外部処理を必要とすることなく、可能な限り復旧を試み、復旧不能の場合でもリセットを際限なく繰り返さないようにし得る電子機器を提供する。

【解決手段】プログラマブルデバイスによりリセットカウンタ回路を形成し、電源オフから電源オンとなった時にシステムリセットの回数値を自動的に初期値にセットするFPGA15を用い、LANインタフェース部11及び音声ビデオCODEC16といった信号処理部単位でデバイスリセットを実行し、一定回数のデバイスリセットを繰り返した後にシステムリセットを行い、FPGA15に保持されるシステムリセットの回数値がリセット設定回数値に達した場合には、システムの起動停止もしくは電源オフを行うようにしている。

(もっと読む)

携帯型情報処理装置のリセット装置

【課題】携帯型情報処理装置のより安全で確実なリセット操作を提供することを目的とする。

【解決手段】外部接続装置が接続されているかどうかを検出する外部装置検出手段15と、リセット指示を行なうリセット指示手段18と、外部装置検出手段15からの外部装置接続情報と、前記リセット指示手段のリセット指示に基づいてリセット操作を行うかの条件判定するリセット条件判定手段16と、リセット条件判定手段16の指示で携帯型情報処理装置のリセット操作を行なうリセット処理手段17と、を備えたことリセット装置であり、携帯型情報処理装置13が搬送、移動状態であると判断された場合には、搬送、移動中の誤動作によってリセットの指示がなされてもリセット操作の実行をしないようにすることでよりリセット誤操作防止をする。

(もっと読む)

拡張ユニットと接続可能な制御ユニット及び同制御ユニットのリセット解除方法

【課題】拡張ユニットがマザーボード等と接続されていないような不完全な接続状態で制御ユニットが動作するのを極力防止できるようにする。

【解決手段】接続検出回路123は、制御ユニット12のコネクタ121とマザーボード11とが接続されている第1の状態を検出する。リセット解除回路125は、接続検出回路123による第1の状態の検出に応じて制御ユニット12のリセット状態を解除する。リセット解除回路125は、拡張ユニット13とマザーボード11とが接続されている第2の状態の場合に特定論理状態となる信号134を拡張ユニット13から信号ピン122aを介して受け取る。リセット解除回路125は、信号ピン122aの論理状態が上記特定論理状態とは異なる論理状態の場合、接続検出回路123による第1の状態の検出の有無に無関係に制御ユニット12のリセット状態の解除を抑止する。

(もっと読む)

半導体集積回路

【課題】 電源電圧が低下した場合に、内部回路の誤動作を正確に検知して確実にリセット信号を生成することが可能な半導体集積回路を提供する。

【解決手段】 モニタ用ラッチ回路4a,4b,・・・は、周辺回路に含まれるラッチ回路と同等の構成を有する。瞬停時において、電源電位VCCが低下してモニタ用ラッチ回路4a,4b,・・・のうちのいずれかの保持データが反転すると、誤動作検出回路3からの副リセット信号/POR2が活性化レベルの「L」レベルにされ、論理回路2からのリセット信号/POR3が活性化レベルの「L」レベルにされる。したがって、周辺回路の誤動作を正確に検知して確実にリセット信号を生成することが可能となる。

(もっと読む)

信号処理装置のリセット方法

【課題】種々の回路異常によりリセット端子が受信するリセット信号の電圧波形が異常となって異常なリセット解除が生じるのを簡素な方式にて防止可能なデジタル信号処理装置のリセット方式を提供すること。

【解決手段】信号処理回路1のリセット信号デコード回路7は、リセット端子6にリセット解除信号が入力している場合に信号処理回路1のプログラム演算回路(ルーチン遂行回路)5にリセット解除を指令し、リセット端子6にリセット信号が入力している場合に信号処理回路1のプログラム演算回路(ルーチン遂行回路)5にリセットを指令する。リセット信号デコード回路7は、リセット端子に所定形態のパルス信号が入力する場合にそれをリセット解除信号と判定し、それ以外のリセット端子電圧波形をリセット信号とみなす。これにより、リセット電圧波形が異常(たとえば電位固定)となってもプログラム演算回路5のリセット状態が解除されて誤ってスタートし、外部に誤った信号が出力されることがない。

(もっと読む)

コンピュータシステム

【課題】 物理的な鍵などを必要とせずに必要な時にはすぐに強制オフ、強制リセットを実施可能なコンピュータシステムを提供する。

【解決手段】 強制電源オフ、システムリセットのパスワードを照合するパスワード照合モードを有し、パスワード照合モードへ移行するイベントの発生の有無を判断し、イベントが発生した場合キーボード10からのキー入力とパスワードを照合する機能を有するキーボードコントローラ9を備えたコンピュータシステム。

(もっと読む)

半導体装置、リセット制御システム及びメモリリセット方法

不揮発性メモリを搭載した半導体装置において、外部からリセット信号が供給されても、不揮発性メモリからのBUSY/READY信号が活性化されている間は、不揮発性メモリにリセット信号を供給しないリセット入力制御回路を設ける。リセット入力制御回路により、不揮発性メモリが消去処理を行なっている間リセットされることがなくなるため、不揮発性メモリの過消去を防止することができる。  (もっと読む)

(もっと読む)

シリアル通信装置、データ通信装置、複写機、複合機

【課題】 プロセッサ間のシリアル通信を利用して、安価に装置の状態を安全にイニシャルする方法を提供する。

【解決手段】 シリアル通信上のストローブ信号をクロック監視手段(ウオッチドッグタイマなど)のクロック入力端子に供給することにより、ストローブ信号にシリアル通信用のストローブ信号とウオッチドッグタイマ制御用のクロックの2つの機能持たせることができ信号線数の削減が可能となる。外来ノイズ等で不用意に各通信信号にノイズがのり電圧変動が生じた場合でも、長い時間のクロック停止には至らず、誤動作としてのリセットがなくなり信頼性の高い通信装置の構築が可能とする。

(もっと読む)

データ処理装置

【課題】マイクロコンピュータがEEPROMとデータの通信動作中、外部操作によるリセット信号を受付けなくするデータ処理装置を提供する。

【解決手段】マイクロコンピュータ1とEEPROM2は、I2Cバスによって接続され、クロック信号に同期してデータ通信する。リセット制御回路4は、クロック信号の有無を検出する検知部13と、検知部13の検出結果に基づいてリセットスイッチ3から出力されたリセット信号のマイクロコンピュータ1への入力の禁止または許可するように動作するスイッチ部12とを備え、データ通信中であればリセットスイッチ3からのリセット信号の入力を禁止する。

(もっと読む)

1 - 20 / 20

[ Back to top ]