Fターム[5B056BB26]の内容

Fターム[5B056BB26]に分類される特許

1 - 6 / 6

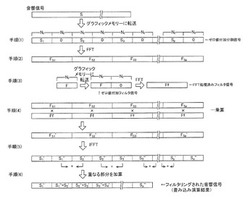

畳み込み演算システム及び畳み込み演算プログラム

【課題】コンピューターによる処理時間を大幅に短縮することが可能な畳み込み演算システムを提供する。

【解決手段】信号長がNsである所定信号と信号長がNfであるフィルタ信号の畳み込み演算システムであって、前記所定信号を信号長がNfのp個の信号に分割し信号長がNfである0値を付加する手段と、前記ゼロ値付加分割信号に対してフーリエ変換を生成する手段と、前記フィルタ信号に信号長がNfである0値を付加する手段と、前記ゼロ値付加フィルタ信号に対してフーリエ変換を施す手段と、前記p個のフーリエ変換処理済み分割信号のそれぞれに対してフーリエ変換処理済みフィルタ信号を乗算し、乗算済み分割信号を生成する手段と、逆フーリエ変換を施し、2p個の信号に分割し、分割された最初の信号と、最後の信号とを除いて、2番目の信号から順次隣り合う信号の加算を行い、畳み込み演算結果の信号を生成する手段と、を有する。

(もっと読む)

デコンボリューション装置、デコンボリューション方法およびプログラム

【課題】デコンボリューションをフーリエ空間で行う方式は、信号の値が小さい領域ではノイズの影響を受け易い。

【解決手段】信号入力部10は表現関数と重み関数とのふたつの関数で表されるふたつの信号の畳み込みによって表現される信号を解析対象の信号として入力を受け付ける。解析対象選択部12は解析対象の信号の種類を指定する。信号変換部14は解析対象選択部で指定された入力信号の種類に基づいて入力信号に所定の信号処理を施した後その信号をフーリエ領域の信号に変換する。微少量推定部16はフーリエ領域における信号の強度に対して所定の割合だけ小さな値の微小定数を推定する。重み関数取得部18は解析対象選択部で指定された入力信号の種類に基づいて重み関数のフーリエ表現である解析関数を取得する。デコンボリューション演算部20は信号変換部で変換された信号を微小定数と解析関数との和で除算することにより表現関数の信号を生成する。

(もっと読む)

コンボリューション演算回路、階層的コンボリューション演算回路及び物体認識装置

【課題】コンボリューション演算を簡易な構成で高速に実行することができるコンボリューション演算回路、階層的コンボリューション演算回路及び物体認識装置を提供する。

【解決手段】制御部101、記憶部102〜103、シフトレジスタ104〜106、複数の乗算器107、複数の累積加算器108及び非線形変換処理部109がCNN処理部に設けられている。CNN処理部は、列方向に並列処理を行う階層的コンボリューション演算回路として機能する。

(もっと読む)

複数のコンピュータ・プロセッサを用いる畳み込み計算システム

最初および最後のプロセッサを含む、プロセッサのアレイを利用して、フィルタ関数によるデータ関数の畳み込みを計算するシステム。フィルタ関数の微分(derivation)に基づく係数値と、データ関数を表すデータ値とが掛け合わされて、現在の中間値が生成される。最初のプロセッサ以外のプロセッサにおいて、前の中間値が現在の中間値に加算される。最後のプロセッサ以外のプロセッサにおいて、データ値および現在の中間値が次のプロセッサに送られる。次に、最後のプロセッサの、前の中間値(あれば)が、最後のプロセッサの現在の中間値に加算されて、フィルタ関数によるデータ関数の畳み込みを集合的に表す結果値が生成される。  (もっと読む)

(もっと読む)

演算回路および演算方法

【課題】2次元空間に配置されたデータに対して、従来よりも少ないサイクル数で畳み込み演算によるフィルタ処理を行うことができる演算回路および演算方法を提供する。

【解決手段】本発明は、2次元空間に配置されたデータの畳み込み演算を行うものである。初期化サイクルにおいて積和レジスタを初期化し、その後、第1〜Nサイクルにかけて順に、2次元空間のN列×N行の範囲の1〜N列目のデータ値をデータレジスタに保持し、前処理回路の1番目の積和演算器の演算結果を後処理回路の1番目の積和レジスタに保持するとともに、前処理回路のn番目(n=2〜N)の積和演算器の演算結果と、前サイクルで後処理回路のn−1番目の積和レジスタに保持された値との積算値を、後処理回路のn番目の積和レジスタに保持する。これにより、N番目の積和レジスタから、2次元空間のN列×N行の範囲の中心に位置する第1の演算対象点の畳み込み演算結果を出力する。

(もっと読む)

畳み込み積分演算装置

【課題】 多種の距離で初期位相が異なる再生点によって形成される再生像を再生することができる計算機ホログラムを高速に作成するのに好適な畳み込み積分演算装置を提供する。

【解決手段】 複数の要素プロセッサPEが実質的に縦続接続されている。各要素プロセッサPEは、座標値Zおよび初期位相値Pに基づいて発生した伝搬関数値を出力する定数発生部91Aと、この伝搬関数値と輝度値Iとを乗算して乗算値を出力する乗算器92と、この乗算値とホログラム時系列信号PDinとを加減算して加減算値を出力する加減算器93と、この加減算値を入力し保持してホログラム時系列信号PDoutとして出力するレジスタ94と、を備える。縦続接続された前段の要素プロセッサのレジスタ94から出力されたホログラム時系列信号PDoutは、後段の要素プロセッサの加減算器93にホログラム時系列信号PDinとして入力する。

(もっと読む)

1 - 6 / 6

[ Back to top ]