Fターム[5B060CD14]の内容

メモリシステム (7,345) | アクセス要求制御 (450) | アクセス競合制御 (325) | アクセス優先制御 (161) | 優先順位によるもの (121) | 優先順位可変のもの (64)

Fターム[5B060CD14]に分類される特許

1 - 20 / 64

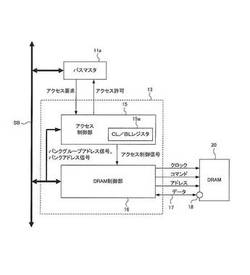

情報処理システム、制御システム及び半導体装置

【課題】制御システムがメモリシステムのバンクグループにアクセスする際の効率を高めることが可能な情報処理システムを提供する。

【解決手段】本発明の情報処理システムは、例えば、メモリシステム20と、アクセス制御部15を含む制御システム13とを備えている。メモリシステム20は、記憶領域が複数のバンクにより構成され、この複数のバンクが複数のバンクグループにグループ化されている。アクセス制御部15は、複数のプロセシングエンジンによるアクセスの優先順位に対応し、バンクグループ毎にレイテンシを含むアクセス情報を第1のレジスタ15aに保持し、バスマスタ11aを介してプロセシングエンジンからのアクセス要求を受けたとき、第1のレジスタ15aを参照し、その内容に基づいてアクセス対象のバンクグループに対するアクセスをフレキシブルに制御する。

(もっと読む)

バスアービタ、バスアービタシステム、バスアービタの処理方法

【課題】同程度の優先度の複数のバスマスタに対し、より優先度の高いバスマスタの使用効率を圧迫しないアービタを提供すること。

【解決手段】共通のバス12に接続されている複数のバスマスタ110からのバス獲得要求を、予め設定されている各バスマスタの優先度に基づき調停するバスアービタ100であって、優先度が最も高い第一のバスマスタからの第一のバス獲得要求、及び、前記第一のバスマスタと同等の優先度である第二のバスマスタからの第二のバス獲得要求を監視するバス獲得要求監視手段14と、前記バス獲得要求監視手段の監視結果を取得して、前記第一のバス獲得要求の頻度及び前記第二のバス獲得要求の頻度が予め定められた基準を満たす特定事象を検知する特定事象検知手段15と、前記特定事象検知手段から特定事象検知信号を取得して、前記第二のバス獲得要求の頻度を制限するバス獲得制御手段13と、を有することを特徴とする。

(もっと読む)

メモリアクセス制御装置、及びメモリアクセス制御方法

【課題】データメモリへのリクエストを優先順位に応じて調停する。

【解決手段】メモリアクセス制御装置に、メモリに対する複数の、それぞれ優先順位を有するリクエストを受け付ける受付部と、前記優先順位を有する複数のキャッシュと、第1の優先順位を有する第1のリクエストが受け付けられると、前記第1の優先順位を有する空き状態の第1のキャッシュに当該第1のリクエストを登録し、前記第1のキャッシュが検出されないときには、前記第1の優先順位より低い第2の優先順位を有する空き状態の第2キャッシュに前記第1のリクエストを登録し、当該第2のキャッシュの前記第2の優先順位を前記第1の優先順位に変更する管理部と、前記第1、または第2のキャッシュに登録された前記リクエストを実行する実行部とを設け、データメモリへのリクエストを優先順位に応じて調停する。

(もっと読む)

情報処理システム、調停方法

【課題】精度の良い調停を行うことができる情報処理システム、及び調停方法を提供する。

【解決手段】イニシエータIP1−1は、ターゲットIP5に対し、一定処理を行うために必要なデータ転送に応じて複数のアクセスリクエストを順次生成して発行する。算出装置2−1は、データ転送の総データ量と、予め設定された転送許容時間と、から第1の転送レートを算出する。算出装置2−1は、所定の設定タイミング毎に、イニシエータIP1−1に転送済みのデータ量と、イニシエータIP1−1がデータ転送を開始してからの経過時間と、から第2の転送レートを算出する。算出装置2−1は、第1の転送レートと、第2の転送レートと、の比較結果に基づいて、イニシエータIP1−1が発行前のアクセスリクエストに対応付ける重みづけを設定する。調停回路4は、アクセスリクエストに対応付けられた重みづけに基づいて、転送処理の調停を行う。

(もっと読む)

光ディスク記録再生用半導体集積回路およびその動作方法

【課題】特殊な記録動作や特殊な再生動作への対応を容易とすること。

【解決手段】半導体集積回路は、再生ECC回路18と記録ECC回路17とホストインターフェース回路19とメモリ制御回路20を具備して、メモリ制御回路20は調停回路200とカウント回路202を含む。事前設定の優先順位で調停回路200は、ECCアクセスをホスト機器2とのホストインターフェースのアクセスより高い優先順位で調停する。カウント回路202はECCリクエストの出力回数をカウントして、カウント出力回数が動作モードの所定の出力回数と一致すると、カウント回路202はカウント終了信号を生成する。調停回路200では優先順位の切り替えが実行され、ECCよりもホストを高い優先順位で調停される。所定の出力回数は、1個のECCブロック又はその整数倍のデータに関係して半導体メモリ22のアクセスに必要なECCアクセスリクエストの出力回数に対応する。

(もっと読む)

トランザクション制御装置

【課題】メモリの個数を削減することができ、半導体装置のチップ面積を削減することが可能なトランザクション制御装置を提供すること。

【解決手段】イニシエータ別トランザクション待ち行列管理部102は、受付制御部101によってキューイング可能と判定されたトランザクションをキューイングし、トランザクションに対応する許容待ち時間が完了するまでに、トランザクションのデータが大規模メモリに書き込まれるようにトランザクション待ち行列の管理を行なってデータの書き込み要求を行なう。優先順位制御部103は、受付制御部101によってキューイングが不可と判定されたトランザクションのデータおよびイニシエータ別トランザクション持ち行列管理部によって書き込み要求が行なわれたトランザクションのデータを優先順位に応じて大規模メモリに書き込む。したがって、メモリの個数を削減することができ、半導体装置のチップ面積を削減することが可能となる。

(もっと読む)

低電力メモリアクセスのためのバスアービトレーションの方法

アクセスレイテンシを低減するバスアービトレーション技法

インタフェース装置、画像形成装置

【課題】送信データの書き込み要求と、受信データの読み出し要求とが重複して発生しているときに、受信データによるメモリオーバーを起こすことなく、送信データの書き込みと受信データの読み出しとからなる一連の処理を行う時間を短縮することができるインタフェース装置を提供する。

【解決手段】調停部24は、送信データの書き込み要求と、受信データの読み出し要求とが重複して発生して、書き込み要求を読み出し要求に優先して有効としている間において、送信データ記憶部20に記憶されている送信データのデータ量が予め設定された第1データ量を超えており、且つ、受信データ記憶部22に記憶されている受信データのデータ量が、記憶容量未満の範囲で予め設定された第2データ量を超えているときには、書き込み要求を有効とすることを中断して、一時的に読み出し要求を書き込み要求に優先して有効とした後に、書き込み要求を有効とすることを再開する。

(もっと読む)

データ転送装置、データ転送方法、データ転送プログラム及び記録媒体

【課題】優先順位の異なる複数のDMACからのメモリへのアクセス要求を優先順を変更して適切に調停するデータ転送装置、データ転送方法、データ転送プログラム及び記録媒体を提供する。

【解決手段】ライン同期信号LSYNCと画像先端同期信号FSYNCに基づいて1ライン分の画像データをメモリから読み取って転送するRDMAC134を含む複数のDMAC123、124からのメモリへのリクエストを予め設定されている優先順位に基づいてリクエスト調停部112が調停する場合、画像処理部11の転送データ量監視部136が2つのラインバッファ132がフル状態か否か監視して、該監視結果に基づいて必要転送量計算部105が、上記優先順位の変更の要否を判定し、優先順位制御部111が該判定結果に基づいてリクエスト調停部112の優先順位を制御する。

(もっと読む)

調停装置

【課題】高速な連続データ転送を行うデータ転送回路にバスの使用権を優先的に付与し、データの転送時間を短縮する。

【解決手段】複数のデータ転送回路2からの要求に応じてSDRAM1のバス使用権の調停を行う調停装置3において、一のデータ転送回路2から転送要求信号211とともに連続要求信号212を入力したとき、該転送要求信号211に応じたデータ転送が終了した後、他のデータ転送回路2に優先して前記一のデータ転送回路2にバス使用権を継続して付与する。

(もっと読む)

電子機器、及びメモリー制御方法

【課題】優先順位が上位のモジュールの連続するメモリーアクセスの間に、優先順位が

下位のモジュールのメモリーアクセスが可能な優先制御方式において、上位のモジュール

の処理をより高速化する。

【解決手段】電子機器は、メモリーと、メモリーへのアクセス要求を1回受け付けた場

合に、当該アクセス要求のアクセス要求元の優先順位を最下位に設定し、次に受け付ける

アクセス要求を選択する優先制御により、メモリーへのアクセスを行うメモリー制御回路

と、メモリー制御回路のポートに接続され、アクセス要求を送る複数のモジュールと、を

備える。ここで、複数のモジュールのうち少なくとも1つの第1モジュールは、メモリー

制御回路の2つのポートに接続され、他のモジュールはそれぞれ1つのポートに接続され

ている。

(もっと読む)

トランザクションの優先レベルを設定するデータ処理装置および方法

【課題】トランザクションの優先レベルを設定するデータ処理装置および方法を提供する。

【解決手段】該データ処理装置は、トランザクションを処理する共有リソースと、該共有リソースへ該トランザクションを発行する少なくとも1つのマスタデバイスとを有する。該少なくとも1つのマスタデバイスは、該トランザクションの複数のソースを提供し、該トランザクションのそれぞれは、これに関連付けられた優先レベルを有する。アービトレーション回路は、該共有リソースへ発行された複数のトランザクションの中からあるトランザクションを選択するように、アービトレーションポリシーを適用するために使用され、該アービトレーションポリシーは、該選択を実行する際に、該複数のトランザクションのそれぞれに関連付けられた該優先レベルを使用する。

(もっと読む)

メモリシステム

【課題】リアルタイム性の要求が高い機能ブロックのリアルタイム性を確保するとともに、リアルタイム性の要求が低い機能ブロックの性能を低下しないようにする。

【解決手段】バスマスタとして動作し、所定の処理を行う複数の機能ブロックと、メモリコントローラと、前記複数の機能ブロックと前記メモリコントローラとを接続するバスとにより構成されるメモリシステムであって、前記機能ブロックは、メモリアクセスを発行する時に前記メモリアクセスが終了する時間情報を付加し、前記バスは、メモリアクセス情報に前記メモリアクセスが終了する時間情報を付加して転送する。さらに、前記メモリコントローラは、複数のメモリアクセスを保持し、前記バスマスタより受信したメモリアクセスが終了する時間情報に基づき、前記保持されたメモリアクセスの発行順序を制御する。

(もっと読む)

メモリシステム

【課題】アクセスパターンによらず、メモリアクセス性能を向上できるようにする。

【解決手段】複数のバスマスターと、前記複数のバスマスターからのアクセスを受け取り、DRAM700へのアクセスを行うメモリアクセス回路600と、前記複数のバスマスターとメモリアクセス回路600とを接続する共有バス400と、共有バス400において前記複数のバスマスターからのメモリアクセスを調停するアービタ500と、メモリアクセス回路600がアクセスするDRAM700とを有するメモリシステムであって、DRAM700のバンクごとにどのページがアクティブであるかの情報を備えたアクティブページテーブルを保持し、前記複数のバスマスターから出力されるアドレスと前記アクティブページテーブルの情報とに基づいて、アクティブなページへのアクセスをしているバスマスターを優先的に選択するバスマスター選択回路520を有する。

(もっと読む)

メモリ制御装置

【課題】優先度の高いメモリアクセスの効率を低下させることなく、優先度の低いメモリアクセスの並列処理を実現できるようにする。

【解決手段】メモリアクセス要求を分割してメモリアクセス要求の優先度を判定し、優先度の高いメモリアクセス要求を保持する高優先度コマンドバッファ105と、優先度の低いメモリアクセス要求を保持する低優先度コマンドバッファ106とに振り分ける。そして、優先度の高いメモリアクセス要求と、優先度の低いメモリアクセス要求とを比較し、メモリコマンドの実行順序を決定し、メモリコマンドの実行順序に従って、優先度の高いメモリアクセス要求と優先度の低いメモリアクセス要求とを選択して実行するよう制御する。

(もっと読む)

アクセス制御回路

【構成】ステータス管理回路26は、互いに異なる優先度を各々が有する複数のバッファ回路14a〜14cから発行された1または2以上のアクセス要求を受け付ける。デコーダ24は、ステータス管理回路26によって受け付けられた1または2以上のアクセス要求が緊急アクセス要求を含むか否かを繰り返し判別する。判別結果が否定的であれば、デコーダ24は、ステータス管理回路26によって受け付けられた1または2以上のアクセス要求のうちより上位の優先度に対応するアクセス要求を承認する。これに対して、判別結果が肯定的であれば、デコーダ24は緊急アクセス要求を承認する。

【効果】複数のアクセス要求の並列的な発行に起因するアクセス処理の破綻を回避することができる。

(もっと読む)

データ処理装置

【課題】FIFOのオーバーフローおよびアンダーフローを防止することが可能なデータ処理装置を提供すること。

【解決手段】演算エンジン2(21)は、RD用FIFO2(22)に記憶されたデータに対して演算処理を行ない、演算結果をWR用FIFO2(23)に格納する。REQ発行制御部24aは、RD用FIFO2(22)からのデータ読出要求と、WR用FIFO2(23)からのデータ書込要求とが発行されたときに、RD用FIFO2(22)に蓄積された有効データ数が優先制御条件設定レジスタ26に設定された下限値未満の場合に、データ読出要求を優先して発行する。また、WR用FIFO2(23)に蓄積された有効データ数が優先制御条件設定レジスタ26に設定された上限値を超える場合に、データ書込要求を優先して発行する。したがって、FIFOのオーバーフローおよびアンダーフローを防止することが可能となる。

(もっと読む)

メモリアクセス制御装置およびメモリアクセス制御方法

【課題】メモリとのデータの転送効率を向上させたメモリアクセス制御装置、メモリアクセス制御システムおよびメモリアクセス制御方法を提供する。

【解決手段】画像処理システム1において、第2のDRAMコントローラ20に、画像処理ユニット30のコマンドI/FとデータI/Fからの両方のデータが入力されるまで第1DRAMコントローラ10へ出力しないように制御するか、若しくは、コマンドI/Fにデータが入力された際にすぐさま第1DRAMコントローラ10に出力しその後に対応するデータI/Fからデータが入力されたときにデータI/Fのデータを出力するように制御するか、のいずれかのモードに切替えてその切り替えに応じたタイミングでデータを出力する調停回路21を備える。

(もっと読む)

データ処理装置、バス調停方法

【課題】トランザクションの調停を適切に処理して命令フェッチされた命令の枯渇等を抑制し、処理効率を向上させたデータ処理装置及びバス調停方法を提供すること。

【解決手段】命令フェッチ及びデータアクセスの各トランザクションに伴う優先度情報に従い各トランザクションを調停してリソースへ接続する接続処理部30と、を有するデータ処理装置100において、命令フェッチされ第1のバッファ31に記憶されている命令数を検出する第1の検出部28と、第1のバッファに記憶されている命令数に応じて、命令フェッチのトランザクションに伴う優先度情報を変更する第1の優先度情報変更部34と、第2のバッファに記憶されているデータの数を検出する第2の検出部と、データアクセスのトランザクションに伴う優先度情報を変更する第2の優先度情報変更部と、を有することを特徴とする。

(もっと読む)

1 - 20 / 64

[ Back to top ]