Fターム[5B060GA02]の内容

Fターム[5B060GA02]の下位に属するFターム

プレーン型メモリ構成 (1)

ピクセル型メモリ構成 (4)

Fターム[5B060GA02]に分類される特許

1 - 4 / 4

情報絞り込み検出機能を備えたメモリ、その使用方法、このメモリを含む装置。

【課題】

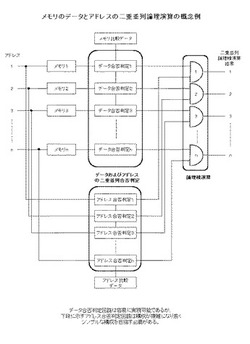

パターン認識など情報検出の最大の課題は検索時間でありメモリの逐次比較処理が不要な非ノイマン型情報検出メモリを実現する。

【解決方法】

メモリアドレスごとに情報を記憶しその情報を読み出し可能なメモリで、このメモリは、外部から与えられる第1のデータは記憶されたメモリのデータを比較するためのデータ、第2のデータはアドレス同士を比較するためのデータ、の双方の入力データの入力手段と、この入力手段から与えられた上記双方の入力データにより記憶された情報のデータと、そのアドレスと、の双方を二重並列に合否判定し、その双方の合否判定結果をさらに並列に論理演算する手段と、上記論理演算に合格するこのメモリの上記アドレスを出力する手段と、を具備することを特徴とする情報絞り込み検出機能を備えたメモリであるのでインテリジェンスな情報検索はもとより人工知能等に広く利用可能である。

(もっと読む)

メモリコントローラ、画像処理システムおよびメモリアクセスの制御方法

【課題】 画像データを読み書きする半導体メモリのアクセス効率を向上する。

【解決手段】 アクセスコスト計算部は、読み出しアクセスおよび書き込みアクセスの少なくともいずれかに必要なサイクル数をアクセスコストとして複数のメモリマップ毎に計算する。メモリマップ選択部は、メモリマップの中からアクセスコストが最も低いメモリマップを選択する。パラメータ変換部は、メモリマップ選択部が選択したメモリマップに基づいて、アクセスアドレスを変換する。アクセス制御部は、変換されたアクセスアドレスに基づいて半導体メモリにアクセスするための制御信号を生成する。アクセスコストの低いメモリマップを用いて半導体メモリにアクセスすることで、半導体メモリのアクセス効率を向上できる。

(もっと読む)

メモリ制御回路および画像処理装置

【課題】 フレームメモリにすでに書き込まれた直前のフレームを構成する画素の画素値を示すデータの出力を開始するまでの遅延時間の短縮化が図られたメモリ制御回路、および回路規模の削減化が図られた画像処理装置を提供する。

【解決手段】 垂直同期信号VSYNCの立ち下がりエッジをSDRAMコントローラ22で検知して、初期アドレスにクリアされたアドレス信号A,読み出しを指示するコマンドCを生成してSDRAM10に供給し、SDRAM10から所定の範囲の過去データを先読みして読み出し用FIFO23に格納しておき、現在データの入力が開始された後に読み出し用FIFO23から読み出して出力する。

(もっと読む)

データアクセス装置、データアクセス方法、プログラムおよび記録媒体

【課題】アクセスパターンの各設定位置で、そのパターンに対応した複数の画素データの同時取得を容易とする。

【解決手段】制御部120は、開始位置に設定されたパターンACPで特定されるN個の初期アクセス画素のデータが夫々異なるバンクに格納されるように、各画素データをN個のバンクに振り分けて格納する。パターンACPは、複数の中心画素とその周辺画素とからなるパターンである。制御部140は、パターンACPで特定されるN個のアクセス画素のデータをN個のバンクから同時に読み出し、またパターンACPの設定位置が画素列方向に移動した際に、N個のアクセス画素のデータが夫々異なるバンクに格納されているように、画素データを移動する。セレクタ160は、N個の画素データDo0〜Do(N-1)から、入出力の対応情報INFに基づいて、各中心画素に対応した各画素群に対応させて画素データD1a〜D1c,D2a〜D2cを出力する。

(もっと読む)

1 - 4 / 4

[ Back to top ]