Fターム[5B061BB03]の内容

バス制御 (3,799) | 調停のための制御方式(アービトレーション) (517) | 集中型調停 (434) | 調停制御装置の回路構成 (150) | 許可信号保持回路を有するもの (12)

Fターム[5B061BB03]に分類される特許

1 - 12 / 12

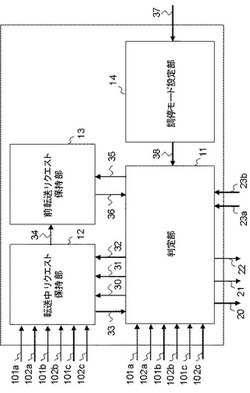

バス調停装置およびバス調停方法

【課題】複数のマスタからスレーブへ同一のアクセス要求が重複して発生した場合であっても、データ転送効率を維持しつつアクセス制御が可能なバス調停装置を得る。

【解決手段】バス調停装置10は、バス1に接続されたマスタ2a〜2cからスレーブ3a、3bへのアクセスを調停するものであって、マスタから送信中の第1のリクエストコマンド及び第1の宛先アドレスの情報を第1のリクエスト情報として保持する転送中リクエスト保持部12と、マスタからスレーブへ送信完了した第1のリクエスト情報を第2のリクエスト情報として保持する前転送リクエスト保持部13と、転送中リクエスト保持部12及び前転送リクエスト保持部13から第1及び第2のリクエスト情報を受信し、これらの情報を用いてマスタ2a〜2cを選択し、アクセス要求先のスレーブ3a、3bへアクセス可能なマスタと判定する判定部11と、を備える。

(もっと読む)

メモリアクセス制御回路、プリフェッチ回路、メモリ装置および情報処理システム

【課題】サイズの異なるラップアラウンドメモリアクセスリクエストを生成する際に、プロセッサストールサイクルが低減するように開始アドレスを変換する。

【解決手段】ヒット判定部230はプロセッサからのラップアラウンドメモリアクセスがプリフェッチバッファ210にヒットしているか否かを判定する。プリフェッチバッファ210においてミスヒットが検出されると、リクエスト生成部240はプロセッサからのメモリアクセスリクエストに従ってメモリへのリクエストを生成し、アドレス変換部250はプロセッサからのラップアラウンドメモリアクセスリクエストのバースト転送の開始アドレスを変換する。アドレス変換部250はプロセッサからの開始アドレスのうちそのバーストサイズに応じた長さの下位ビット部分をゼロ値に置換することによりアドレス変換を行う。

(もっと読む)

バス調停装置、バス調停方法

【課題】 バス調停装置がバス使用許可を与えようとした時に、バス使用要求信号を出力できなかったマスタは、予め設定したバス獲得回数の比率でバス使用権を精密に付与することが困難である。

【解決手段】 バススレーブの動作中は、予め設定したバス獲得回数の転送を行っていないバスマスタのバス使用要求信号が出力されるのを待つようにバス調停装置を動作させる。

(もっと読む)

アービタ、バス使用制御装置、及びバス使用制御方法。

【課題】無駄なトランザクションによるバスの占有を削減しつつ、データを遅滞なく読み出す。

【解決手段】アービタ14は、単機能しか有しないPCIデバイス11DからPCIバス12Bの使用が要求された場合、PCIバス12Aが使用中であれば、PCIバス12Bの使用を許可せず、PCIバス12Aが使用中でなければ、PCIバス12Bの使用を許可する。これに対して、複数機能を有するPCIデバイス11CからPCIバス12Bの使用が要求された場合には、PCIバス12Aが使用中であるか否かに関わらず、PCIバス12Bの使用を許可する。

(もっと読む)

アクセス競合試験におけるアクセス競合発生システム

【課題】アクセス競合試験において、アクセス信号の確実な競合が速やかに実現し得るように構成されたアクセス競合発生システムを提供する。

【解決手段】第1及び第2のインターフェースのそれぞれから出力されるべき実アクセス信号と同様な第1及び第2の擬似アクセス信号が格納手段に格納され、第1及び第2のインターフェースのそれぞれには第1及び第2のローカルバス制御手段が設けられる。第1及び第2の擬似アクセス信号は擬似アクセス信号送出手段により第1及び第2のローカルバス制御手段に順次送出される。アービトレーション部にはアクセス監視手段が設けられる。第1及び第2の擬似アクセス信号のそれぞれには、第1及び第2のローカルバス制御手段からアクセス監視手段に送出されるべき送出タイミング時間として同じ時間が含まれる。

(もっと読む)

制御装置及び制御方法

【課題】同一の信号線を介して、内部バスマスタと内部バススレーブに対して転送状態を示す信号を送信する処理回路において、内部バスマスタと外部バススレーブ間のデータ転送と、外部バスマスタと内部バススレーブ間のデータ転送とを適切に実行する制御装置及び制御方法を提供する。

【解決手段】本発明に係る制御装置は、内部バスマスタと外部バススレーブとの間の第1のデータ転送と、内部バススレーブと外部バスマスタとの間の第2のデータ転送とにおける状態信号を、内部バスマスタ及び内部バススレーブに接続される信号線を介して、内部バスマスタ及び内部バススレーブに送信する送信部と、第1のデータ転送又は第2のデータ転送の実行の要求を検出する要求検出部と、第1のデータ転送又は第2のデータ転送の一方の実行の要求が検出された場合、他方の第1のデータ転送又は第2のデータ転送の実行を禁止する通信管理部とを具備する。

(もっと読む)

情報処理装置およびアクセス制御方法

【課題】メモリなどへのアクセス処理にオーバーヘッドが生じる場合がある。

【解決手段】リクエスタはメモリコントローラへアクセス要求を発行する。発行されたアクセス要求はメモリコントローラにおけるコマンドキューに蓄積される。コマンドキューにおけるアクセス要求の蓄積量がしきい値以下であるとき、指定されたリクエスタにはフリーパス(FP)を与える。リクエスタはアクセス要求を発行する際、FPを取得してなければ(S30のN)、トークンを要求し(S32)、取得してから(S34)アクセス要求を発行する(S36)。FPを取得していればそのままアクセス要求を発行する(S36)。

(もっと読む)

情報処理システム及び情報処理システムの制御方法

【課題】 処理時間を短縮することができ、消費電力を容易に低減することができる情報処理システム及び情報処理システムの制御方法を提供する。

【解決手段】 情報処理システム1は、バス3と、USB用I/O30と、UART用I/O40と、DMAC20と、バス調停回路70と、クロック分周回路80とを備える。USB用I/O30及びUART用I/O40は、DMA要求信号を出力する。DMAC20は、DMA要求信号に基づいて、バス権要求第1信号を出力する。バス調停回路70は、バス権要求第1信号に基づいて、バス権許可第1信号を出力する。DMAC20は、バス権許可第1信号に基づいて、DMA許可信号を入出力デバイスに出力する。クロック分周回路80は、バス権許可第1信号とDMA許可信号とに基づいて、クロック周波数を決定する。

(もっと読む)

アクセス制御バス・システム

アクセス制御デバイスは、許可されないイニシエータとターゲットとのペア間において、バス上のデータ転送を禁止する。各々のターゲットに対する各々のイニシエータのアクセス許可を識別する許可マトリックスが維持される。アクセス・デバイスは、バスをモニタし、イニシエータ及び意図されたターゲットの識別情報を決定する。もしイニシエータがターゲットへの適切なアクセス権を有するならば、バス通信の発生が許可され、そうでなければ、通信は遮断され、エラー信号が発効する。更なるセキュリティを提供するために、アクセス制御デバイスに対してローカルであるイニシエータの識別子が、各々のイニシエータへの直接配線接続を介してアクセス制御デバイスへ通信される。  (もっと読む)

(もっと読む)

バス制御装置および情報処理システム

【課題】 マスタの処理負担が小さく、バス使用待ち時間の短縮とシステムの処理性能向上を実現できるバス制御装置を得る。

【解決手段】 バス制御装置40は、各マスタに転送許可を与える優先順位を格納する優先順位格納部402と、バス30が使用可能な状態の場合には、優先順位に基づいて転送許可を与えるマスタを決定し、そのマスタに対して転送許可を通知すると共に、バス30が当該マスタからの入力を受信するように切り替える使用権制御部403と、転送要求を出力している各マスタに転送許可が与えられるまでの待ち時間を算出し、それらのマスタから通知された待機可能な要求時間内に転送許可が与えられるか否かを判定し、判定結果を各マスタに通知する制限時間内転送判定部404を備える。

(もっと読む)

ストリーミングIDメソッドによるDMAC発行メカニズム

【課題】 DMA発行メカニズムを効率化するための方法及び/又は装置を提供する。

【解決手段】

プロセッシングエレメントからのストリーミングIDを用いたダイレクトメモリアクセスリクエストコマンドの発行システム100である。この発行システム100は、バス130と、メモリコントローラ122と、バスインターフェースユニット116,118,120を有し、BIU段は、前記バス手段と前記DMAC手段との間に接続される。また、メモリコントローラ122は、いずれのコマンドをコマンドバスリクエストとして展開するか否かを決定し、この決定は、スロット変更、ストリーミングID、及び前記コマンドの新旧の少なくとも一つを要素とする発行ポリシーの関数としてなされる。

(もっと読む)

バス要求制御回路

【課題】優先度が高いマスターのみがバス権を占有することがないようなバス権の制御を行うことができるバス要求制御回路を提供すること。

【解決手段】要求承認信号を受けてから所定のリクエストインターバルの期間をカウントするカウンタを設けておき、カウンタによるカウントが行われている間は、バッファメモリの空き状態によらずリクエスト信号の送信を禁止するようにする。また、カウンタのカウントが終了した後、バッファメモリに空きがあれば、アービタに対してリクエスト信号を送信するようにする。

(もっと読む)

1 - 12 / 12

[ Back to top ]