Fターム[5B061BB07]の内容

バス制御 (3,799) | 調停のための制御方式(アービトレーション) (517) | 集中型調停 (434) | 調停制御装置の回路構成 (150) | 要求マスク機構を有するもの (10)

Fターム[5B061BB07]に分類される特許

1 - 10 / 10

処理要求送信回路、及び情報処理装置

【課題】データ処理部において輻輳が発生するおそれを低減しつつ、システムの性能を引き出すことが容易な処理要求送信回路、及び情報処理装置を提供する。

【解決手段】被処理データ列を受け付ける要求受付部31と、受け付けられた被処理データ列をデータ処理部5へ送信する処理要求送信部32と、被処理データ列のデータ長を計数するデータ長計数部33と、計数されたデータ長のデータをデータ処理部5が処理するのにかかる処理時間を算出する処理時間算出部34とを備え、処理要求送信部32は、一の被処理データ列をデータ処理部5へ送信した後、次に被処理データ列をデータ処理部5へ送信するまでに、一の被処理データ列についてデータ長計数部33により計数されたデータ長に基づき処理時間算出部34によって算出された処理時間以上の間隔を空けるようにした。

(もっと読む)

データ転送制御装置およびデータ転送制御方法

【課題】共有バスに接続する複数のDMAチャネルがあって、SDRAM等のメモリにアクセスする際に、あらかじめ決められた優先順位を守りながら、高効率にメモリアクセスする調停手段を提供する。

【解決手段】マスターデバイスからのデータ転送要求を一定量保持する要求保持部と、保持されたデータ転送要求を優先順位及び予め定められた回数だけ連続するように並び替える要求並び替え部とを備え、前記データ転送要求を前記要求並び替え部が並び替えた順で発行することで、優先順位に応じて複数チャネルを並び替えるとともに同格の優先順位を持つ複数チャネルを平均的に連続させることができる。

(もっと読む)

モジュール、割り込みコントローラ、動作方法、画像処理装置、画像形成装置、プログラム及び記録媒体

【課題】複数の割り込み要因を持つモジュールからの割り込みが発生した後と、複数の割り込み要因を持つモジュールからの1割り込み要因クリア処理が終了した後の、割り込み処理を高速化するモジュール及び割り込みコントローラを提供する。

【解決手段】複数の割り込み要因を持ち、割り込み要因毎に割り込み通知マスクを設定する割り込み通知マスク手段を有したモジュールであって、割り込み通知マスク手段により割り込み通知マスク設定が解除された複数の割り込み要因のなかで、少なくとも1以上の割り込み要因が発生した場合にパルス信号を出力し、当該モジュールでの割り込み要因発生を割り込みコントローラに通知する割り込み通知手段と、通知した割り込み要因がクリアされる前に他の割り込み要因が発生した場合には、割り込み通知手段が割り込みコントローラに対して割り込み要因発生を通知することを遮断する通知遮断手段と、を有する。

(もっと読む)

バス調停回路及びバス調停方法

【課題】各バスマスタが複雑なバス要求をしたとしても、最適なバス使用許可期間を保証することができるバス調停回路を提供することである。

【解決手段】本発明にかかるバス調停回路1は、複数のバスマスタ4、5、6からのアクセス要求のうち優先度の高いバスマスタからのアクセス要求に対してバス使用権を許可する固定優先判定回路3と、複数のバスマスタからのアクセス要求を固定優先判定回路3へアサートするか否かを判定する判定調整回路2と、を備える。判定調整回路2は、バス使用権が許可されているバスマスタのアクセス要求とバス使用権が許可されていないバスマスタのアクセス要求とが競合した場合、バス使用権が許可されているバスマスタのアクセス要求を所定の期間マスクする。

(もっと読む)

DMA調停装置、DMA調停方法およびDMA調停用のプログラム

【課題】従来のDMA調停装置においては、セット動作の切り替えの過渡期間において複数DMAからの要求バンド幅総和がシステムの限界を上回ることがあると、セットの機能破綻が引き起こされるという課題があった。

【解決手段】複数マスタそれぞれのDMA要求を独立して発行するDMA要求生成部Y1〜Y4と、マスタそれぞれの要求バンド幅W1〜W4を個別に算出するDMA要求バンド幅算出部B1〜B4と、各要求バンド幅の総和σを求める要求バンド幅総和算出部21と、要求バンド幅総和σを限界バンド幅σ0 と比較するバンド幅比較部H0と、比較の結果、要求バンド幅総和σが限界バンド幅σ0 以下のときはDMA要求生成部Y1〜Y4それぞれのDMA要求を有効化し、要求バンド幅総和σが限界バンド幅σ0 を上回るときはDMA要求生成部Y1〜Y4のDMA要求を無効化するDMA要求処理手段P0とを備える。

(もっと読む)

データ転送制御装置、データ転送制御方法、データ転送制御プログラム及び記録媒体

【課題】本発明は、データ転送を効率的に行うデータ転送制御装置、データ転送制御方法、データ転送制御プログラム及び記録媒体に関する。

【解決手段】画像処理装置1は、メインCPU3を介したデータ転送要求が、複数のDMAC20a〜50aからあると、内部アービタ70が、該データ転送要求に対して公平に所定転送期間だけデータ転送を許可するデータ転送の許可/不許可を制御するとともに、許可したデータ転送が該転送期間を経過すると、該DMAC20a〜50aからのデータ転送要求をマスク期間だけマスクするマスク処理を制御する際に、メインCPU3の内部バッファのデータ量をフローコントロール処理時間毎に取得して、取得した内部バッファのデータ量に基づいてメインCPU3によるデータ転送状況を判定し、該判定結果に基づいてマスク処理を制御する。

(もっと読む)

資源要求調停装置、資源要求調停方法、及び、コンピュータプログラム

【課題】本発明は、予め固定された優先順位を用い、かつ当該優先順位の他には資源要求装置間の関係を関知することなく、各資源要求装置へのサービス品質を管理する資源要求調停装置を提供する。

【解決手段】本発明の資源要求調停装置において、リクエストマスク部50、51は、それぞれメモリアクセス要求部80、81が必要最小頻度を超えて発行したメモリアクセス要求REQをマスクし、調停部40は、リクエストマスク部50、51によってマスクされなかったメモリアクセス要求RREQの一つを、予め固定された優先順位に従って承認する。これにより、当該優先順位の他には各メモリアクセス要求部間の関係を関知することなく、しかも、固定優先順位のごく簡便な調停によって、各メモリアクセス要求部が必要とする資源要求の承認頻度が保証される。

(もっと読む)

バスアクセス要求の選択的除外

バスアクセス要求を選択的に除外するシステムおよび方法が開示される。実施形態では、方法はプロセッサの論理回路でバスユニット・アクセス設定を判定することを含む。この方法はバスユニット・アクセス設定に基づいてバスユニット・アクセス要求を選択的に除外することをさらに含む。  (もっと読む)

(もっと読む)

情報先行取得による調停方法および調停装置

【課題】複数のマスタで同一のメモリを共有するメモリ制御システムにおいて、例えば画像処理を行うマスタが一定の高いメモリ帯域を要求している場合には、その高いメモリ帯域確保を保証するために高優先でアクセスを行うため、プロセッサなどの低いメモリ帯域で、かつ素早い応答性が必要なマスタに対するアクセス応答性が悪くなってしまう。

【解決手段】一定のメモリ帯域を要求するマスタに対しては要求を前倒しに処理させ、なおかつ、プロセッサなどの内部にあるアクセス属性を調停部へと先行的に通知することで、その前倒しの処理に対して一時的にマスクし、プロセッサのメモリアクセス応答性を高めて、プロセッサの処理性能を向上することができる。

(もっと読む)

電子機器、制御方法及びコンピュータプログラム

【課題】 リアルタイムでの処理を行えるようにする。

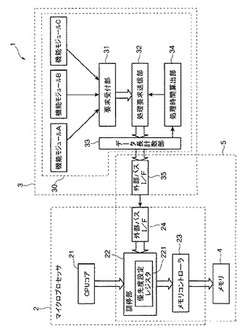

【解決手段】 リアルタイム性の高いバスマスタであって、撮像素子10からの撮像データをDMA伝送する第1のDMAコントローラ(第1のマスタ)16にデータバッファ100を設け、このデータバッファ100のデータ蓄積量と所定の閾値との大小判定から、バスバンド幅を推定し、バスバンド幅が足りないと推定された場合においては、他のバスマスタ22、26からの要求の一部あるいは全てを禁止することにより、第1のDMAコントローラ(第1のマスタ)16に多くのバンド幅を割り当てるようにして、撮像データをSDRAMに記録する処理をリアルタイムで行えることを保証できるようにする。

(もっと読む)

1 - 10 / 10

[ Back to top ]