Fターム[5B061FF00]の内容

バス制御 (3,799) | バスアダプタ(バス結合装置) (397)

Fターム[5B061FF00]の下位に属するFターム

バス間接続用バスアダプタの作用効果 (343)

バス分割用トライステートバッファの作用効果 (9)

トライステートバッファ回路の制御方法 (34)

Fターム[5B061FF00]に分類される特許

1 - 11 / 11

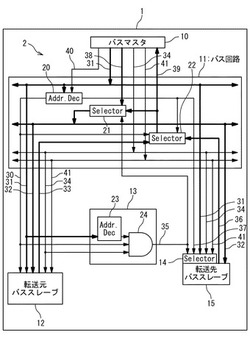

バス接続回路、半導体装置及びバス接続回路の動作方法

【課題】直接転送をする場合と直接転送をしない場合とが混在しても、MEMC設定等の追加の動作を行うことなく、1サイクル転送することを可能とする。

【解決手段】バス接続回路は、バスマスタ10と複数のバススレーブ12、15とを接続する。バス接続回路は、ミラー領域アクセス検出回路13と、処理回路21、22、14とを具備する。ミラー領域アクセス検出回路13は、バスマスタ10が複数のバススレーブ12、15のうちの第1バススレーブ12のミラー領域へアクセスすることを検出して、検出信号35を出力する。処理回路21、22、14は、検出結果35に基づいて、当該検出結果35に対応して予め設定されている処理を、アクセスの対象としての領域又はデータに対して実行する。

(もっと読む)

入出力制御装置、コンピュータ、及び制御方法

【課題】CPUの命令に応じてPCI Expressデバイスとメインメモリとの間のデータの入出力を制御すること。

【解決手段】外部のPCI ExpressデバイスDと接続されるホストバスアダプタHと、ホストバスアダプタHとメインメモリ300との間に接続されて、ホストバスアダプタHを介してPCI ExpressデバイスDとメインメモリ300との間においてデータを転送するデータ転送部120と、ホストバスアダプタH、及びデータ転送部120を含む入出力制御装置100の各部を制御するファームウェア制御部110とを備え、ファームウェア制御部110は、PCI ExpressデバイスDからメインメモリ300へ転送すべき全てのパケットの送出が完了したときに、その旨をCPU200へ通知する。

(もっと読む)

相互接続装置、および、その制御方法

【課題】バスシステムが許容するトランザクション数の最大値の増大に伴う記憶容量の増大を抑制する。

【解決手段】バッファ220は、トランザクション処理を識別するための識別情報とリクエストの各々の発行順序を特定するための順序情報とをレスポンスの各々の転送処理を制御するためのトランザクション情報に対応付けて管理情報として保持する。バッファ管理部230は、マスタからリクエストが発行された場合にリクエストに基づいて管理情報をバッファに格納し、スレーブからレスポンスが返送された場合にレスポンスに係る識別情報を含む管理情報内のトランザクション情報をトランザクション情報に対応する順序情報に従ってバッファから読み出す。相互接続部は、リクエストをスレーブへ転送し、順序情報に従って読み出されたトランザクション情報に基づいてレスポンスの各々をマスタへ転送する。

(もっと読む)

バックエンドでの通信の規格がSASであるストレージシステム

第1のコントローラ及び複数の記憶デバイス(PDEV)に接続された第1の通信経路と、第2のコントローラ及びそれら複数のPDEVに接続された第2の通信経路がある。各通信経路は、直列に接続された複数のエクスパンダを有する。通信経路がI/Oに使用されない時間を短くするために、(A)通信経路についてI/O抑止が設定されている時間長を短くする、又は、(B)I/Oの処理以外の処理(例えばディスカバープロセス)にかかる全体的な時間が短くされる。(A)では、I/O抑止の通信経路について、エクスパンダとエクスパンダ間の接続が切断されているか否かが判断され、その判断の結果が否定的であれば、その通信経路についてI/O抑止を解除してから、ディスカバープロセスが行われる。(B)では、エクスパンダが有するルーティング制御情報を更新するためのコマンドの発行数が減らされる。 (もっと読む)

PCIExpress通信システム、及びその通信方法

【課題】フォルトトレランスの向上を図るとともに、故障回復時間を短縮することが可能なPCI Express通信システム、及びその通信方法を提供することを目的とする。

【解決手段】TLPダイジェストには、トランザクション層の回路がエラーを検出し、送信データについてエラー情報を設定し、ルートコンプレックス1が送信したメモリリードリクエストを受信したエンドポイント3aは、要求されたTLPに対応する第1のデータの送信中にエラーを検出した場合にはエラー情報をTLPダイジェストにセットしてデータ付きコンプリーションを返信するステップと、ルートコンプレックス1は、エラー情報に基づいたメモリリードリクエストをエンドポイントに送信するステップと、エンドポイントは、要求された第2のデータを返信するステップと、ルートコンプレックスは保持していた第1のデータのエラー箇所に第2のデータを上書きして、この応答を完了させるステップとから成る。

(もっと読む)

計算機システム、管理方法及び管理サーバ

【課題】PCIスイッチにおける未割り当てスロットに必要なリソース量を削減する。

【解決手段】計算機とPCIスイッチに接続されたI/Oデバイスと計算機に接続される第1のポートとI/Oデバイスに接続される第2のポートとを備えたPCIスイッチとPCIスイッチの構成を管理するスイッチ管理部と電源制御部とを備えたシステムにおいて、スイッチ管理部は、起動する計算機が接続された第1のポートを判定し、PCIスイッチに通知し、第1のポートに接続された計算機の起動を電源制御部に指令し、計算機に対するI/Oデバイスの割り当てを管理し、計算機の起動後にI/Oデバイスの割り当てをPCIスイッチに通知し、PCIスイッチは、第1のポートの判定結果に基づいて、計算機から第1のポートへの構成認識を抑止し、スイッチ管理部からの通知に基づいて、第1のポートと第2のポートとを接続する仮想スイッチを生成する。

(もっと読む)

情報処理装置および方法、並びにプログラム

【課題】より迅速にデータを送信できるようにする。

【解決手段】CPU81はパケットのヘッダを生成してヘッダ用メモリ82に記録させる。また、CPU81は、送信するデータおよびヘッダが記録されている位置を示すディスクリプタを生成する。MAC84は、ディスクリプタにより指定されたヘッダをヘッダ用メモリ82から取得するとともに、ペイロードとしてのデータをデータ用メモリ85から取得し、取得したヘッダとペイロードとからパケットを生成する。このとき、データ用メモリ85とヘッダ用メモリ82とはブリッジ83により切り離されているので、CPU81は、MAC84によるペイロードの取得と並行して、次のパケットのヘッダを生成してヘッダ用メモリ82に記録させる。本発明は、情報処理装置に適用することができる。

(もっと読む)

データ処理装置およびデータ転送システム

【課題】処理の煩雑性の増加や、パフォーマンスの劣化を生じさせることなく、PCIバス上を流れるデータを効率的に暗号化することができ、かつ暗号化強度も保つ。

【解決手段】 PCIマスタデバイス1は、128ビット暗号データのライトアクセスを行う場合、ベースアドレス0の空間へアクセスする。また、PCIマスタデバイス1は、少量のデータをライトアクセスする場合、ベースアドレス1の空間へアクセスする。PCI I/F部5は、アクセスされたベースアドレスに応じたベースアドレス信号BASを出力する。セレクタ8は、ベースアドレス信号BASに従って、128ビット復号部6で復号されたデータをデータ処理部9へ出力するか、32ビット復号部7で復号されたデータをデータ処理部9へ出力する。

(もっと読む)

コンピュータ装置及びそのデータ転送方法

【課題】 リクエストが圧縮された演算器の数や圧縮のパターン数が多い場合でも圧縮情報のビット数を小さくすることが可能なデータ転送方法を提供する。

【解決手段】 番号が連続する複数の演算器からのメモリリクエストが一のメモリポートに競合する場合には、これら複数のメモリリクエストを1つに圧縮する。この際、演算器番号情報とメモリアドレス特定用情報とを含む圧縮情報を生成する。演算器番号情報は、圧縮される複数のメモリリクエストの発行元である複数の演算器のうち特定の演算器の番号を示す情報である。メモリアドレス特定用情報は、前記一のメモリポートに含まれるメモリアドレスのうち何れのメモリアドレスに対するリクエストを圧縮したのかを示す情報である。リプライが前記一のメモリポートから戻ってくると、該リプライを圧縮情報に基づいてリクエスト発行元の演算器に分配する。

(もっと読む)

メモリコントローラ

【課題】接続されるバスマスタの個数によらず回路規模を略一定に保つとともに、バスリクエストの待ち時間を格段に短縮するメモリコントローラを提供する。

【解決手段】バスマスタ3−1〜3−4からの各バスリクエストから1つを選択するセレクタ15−1,15−2,16と、各セレクタで選択されるバスリクエストが重複しないように切換制御するアービタ17と、セレクタ15−1,15−2に接続されて、バスマスタの個数分のアクセスデータ単位長の記憶容量をそれぞれ有するバッファメモリ14−1,14−2と、バッファメモリ14−1,14−2の各出力とセレクタ16の出力とから、1つの出力を選択するためのセレクタ12と、セレクタ16からセレクタ12に供給されるバスリクエストの出力優先順位を最も低くしてセレクタ12から1つの出力を選択するアービタ13とを具備した。

(もっと読む)

デバイスコントローラ

アドインボード上のPCIデバイスやカードデバイスを制御するために用いられるデバイスコントローラである。マスタデバイスを含む複数のデバイスをアドインボード上に搭載し、かつ、それらのデバイスの動作を円滑に制御することでマルチファンクションのPCIデバイスまたはカードデバイスを構築するために、デバイスコントローラ(1)に、デバイス(D1〜D8)からのバスマスタ要求に対応するバスアービタ回路(17)を設け、バスアービタ回路(17)およびターゲット検出回路(16)によりイニシエータおよびターゲットを検出させ、バスシーケンサ2に前記検出結果に基づいた適正な手順でバスマスタサイクル等における信号の発行を制御させるとともに、アドインボード(30)をホスト装置に単一のマルチファンクションデバイスとして認識させる。  (もっと読む)

(もっと読む)

1 - 11 / 11

[ Back to top ]