Fターム[5B061FF21]の内容

バス制御 (3,799) | バスアダプタ(バス結合装置) (397) | トライステートバッファ回路の制御方法 (34)

Fターム[5B061FF21]の下位に属するFターム

アービトレーションを行うことにより制御するもの (8)

双方向トライステートバッファ回路の方向制御 (3)

アドレスをデコードすることにより制御するもの (9)

バス上の電圧を検出することにより制御するもの (2)

切換え時にハイインピーダンス期間を設けるもの (2)

Fターム[5B061FF21]に分類される特許

1 - 10 / 10

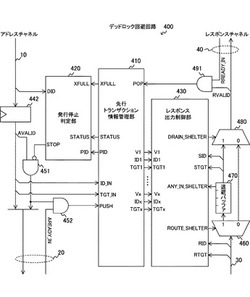

バスシステムおよびそのデッドロック回避回路

【課題】スプリットトランザクションにより複数のスレーブへの同時アクセスを許容したシステムにおいて、デッドロックの発生を防止する。

【解決手段】先行トランザクション情報管理部410は、対応するマスタから複数のスレーブの何れかに先に発行された先行トランザクション情報を管理する。発行停止判定部420は、先行トランザクション情報に基づいて、対応するマスタから新たに発行されたトランザクションがデッドロックの要因になるか否かを判定する。レスポンス出力制御部430は、先行トランザクション情報に基づいて、対応するマスタへ返送すべきレスポンスを制御する。退避バッファ470は、先行トランザクションに対する複数のスレーブからのレスポンスが予め期待された順序とは異なる順序で戻ってきた場合に、そのレスポンスを退避する。

(もっと読む)

共有バス制御装置及びその制御方法

【課題】 共有バスを使用した複数のデバイスの第1のデバイスがバスを使用しているときに第2のデバイスへのアクセス要求があった場合、その第1のデバイスの終了を待つか、そのアクセスを中断する必要があった。

【解決手段】 ホストコントローラ101と複数のデバイス102,103の各々の間の制御バスとデータバスのそれぞれに接続され、ホストコントローラからの制御信号に応じてバスを切断或は接続する複数のバススイッチ(104〜107)を有し、ホストコントローラからの制御信号により、未使用のバスに接続されたバススイッチの接続を別のデバイスとの接続に切り換えることにより、ホストコントローラと複数のデバイスとの間でのアクセスを可能にする。

(もっと読む)

伝送バスとモジュール間のポイント・ツー・ポイント通信の制御装置

【課題】接続されたモジュールの個数および位置にかかわらず、バックプレーンの伝送バスの容量、ひいては信号の質の高さを確保できる装置を提供する。

【解決手段】伝送バス22を持つプリント回路20と、モジュール10を伝送バス22に接続するための接続要素21とを備えた、モジュール10と伝送バス22間のポイント・ツー・ポイント通信の制御装置に関する。プリント回路20は、一方向通信の論理ゲート24E、24Rを備えた、伝送バス22と接続要素21間に配置された通信制御ユニット23、および前記論理ゲート24E、24Rの論理制御回路30を備える。本発明はプログラマブル制御装置に適用する。

(もっと読む)

バスシステム及びマイクロコンピュータ

【課題】バス渡り転送における周辺バスアクセス転送のレイテンシ性能を向上させる。

【解決手段】第1バス(100)と第2バス(200)とがバスブリッジを介して接続される。このとき、上記バスブリッジは、第1バスにアドレス信号が出力されたバスサイクルにおいて、上記アドレス信号が上記第2バスアクセスである場合に、同じバスサイクルで上記第1バスのアドレス信号を上記第2バスへ出力可能なアドレス伝達回路(101)を含んで構成される。第1バスにアドレス信号が出力されたバスサイクルと同じサイクルで、第2バスにアドレス信号を出力することが可能となるため、低速なバスサイクルで1サイクル分削減可能となり、低レイテンシ転送が実現できる。

(もっと読む)

システムバスのインタフェース

【課題】ディジーチェーン接続のシステムバスと機能モジュールとの間の接続不良を自動的に識別し、データバスにおける出力衝突回避さらに異常原因究明等を簡単にする。

【解決手段】ベース1上のデータバスのバイパス・バッファ11のイネーブル信号EN1をモジュールの内部回路14から出力すると共に他のコネクタピンから自モジュールに読み返し、この読み返し信号EN1Rを出力バッファ13のイネーブル条件にすることにより、モジュールとベースとが中途半端な接続状態にあるときにもデータバスにおける出力衝突を回避する。

イネーブル信号EN1と読み返し信号EN1Rの不一致で中途半端な接続状態を報知することにより異常原因究明等を簡単にする。

(もっと読む)

CPUバスアクセス補助回路

【課題】ASIC、FPGAなどの内部回路におけるCPUインターフェース部のリードアクセスを、バス衝突を発生することなく省略可能にして、回路規模を削減する。

【解決手段】CPUバスアクセス補助回路(103)は、CPU(101)からASIC及びFPGAデバイス(106)〜(107)へのデータ書き込み信号を受けた時、前記CPUから出力されたアドレスに該当する前記デバイスのアドレスに前記CPUから出力されたデータを書き込むための制御を行うとともに、該書き込まれたアドレスおよび書き込みデータを外部RAM(105)に記憶し、前記CPUから前記デバイスからのデータ読み出し信号を受けた時、前記デバイスにアクセスしないで、前記外部RAMの該当アドレスに記憶されているデータを読み出して前記CPUへ出力可能にする。

(もっと読む)

半導体集積回路装置

【課題】 低コストで、かつ簡単な回路構成により、半導体メモリへのデータ転送速度を大幅に向上させる。

【解決手段】 メモリカードに設けられたブリッジチップ4には、リードイネーブル信号/RE、およびリードデータを転送するパスゲート17,17a,18,18aが設けられている。メモリカードにおけるリード動作時には、パスゲート17,17aのいずれかを介してリードデータを半導体メモリに転送することにより、データの転送速度を大幅に向上させることができる。

(もっと読む)

ナノスケール相互接続インターフェース

本発明の一実施形態は、抵抗器のようなナノワイヤ接合部でもって、ナノワイヤクロスバー(3000)又はハイブリッドナノワイヤ/マイクロスケール信号線クロスバーとして実現されるデマルチプレクサを提供する。一実施形態のデマルチプレクサは、追加の内部アドレス線(3010、3012)を用いて、2k個のナノワイヤアドレスを、より大きな内部nビットアドレス空間にマッピングするために、k個のマイクロスケールアドレス線(3003、3004)上に入力される信号を2k個以下のナノワイヤ(3006〜3009)に逆多重化することを提供し、ここでn>kである。本発明のデマルチプレクサの第2の実施形態は、2k個の良好に分散したnビット外部アドレスを用いて、2k個のナノワイヤにアクセスするために、n個のマイクロスケールアドレス線上に入力される信号を2k個のナノワイヤに逆多重化することを提供する。本発明の更なる実施形態は、ナノワイヤアドレスの異なるサイズの内部アドレス空間への種々のマッピングを評価するための方法、又はナノワイヤの異なるサイズの外部アドレス空間へのマッピングを評価するための方法、アドレスマッピング及びデマルチプレクサ設計を評価するための測定基準、並びにデマルチプレクサ設計方法を含む。 (もっと読む)

アドレスバス出力制御用の装置及び方法

多様な装置及び方法が記載される。フロントサイドバスのデータバス部分からデータを受信するデータセンス増幅器を有するプロセッサにより実行される第1の方法によると、アドレスストローブがアサートされることに応じて、データセンス増幅器はイネーブルになる。少なくともキューが空になることに応じて、データセンス増幅器はディセーブルになる。フロントサイドバスのデータバス部分からデータを受信するデータセンス増幅器と、フロントサイドバスのアドレスバス部分からアドレスを受信するアドレスセンス増幅器とを有するプロセッサにより実行される第2の方法によると、要求指示がアサートされることに応じて、アドレスセンス増幅器がイネーブルになる。アドレスストローブがアサートされることに応じて、データセンス増幅器がイネーブルになる。要求指示がアサート停止されることに応じて、アドレスセンス増幅器がディセーブルになる。少なくともキューが空になることに応じて、アドレスセンス増幅器がディセーブルになる。キューはこれからデータバスで実行されるトランザクションを追跡する。  (もっと読む)

(もっと読む)

データバス出力制御用の装置及び方法

データバス出力制御用の手法である。要求エージェントのデータ入力センス増幅器は、データバス出力制御信号によるトランザクションのデータフェーズの前にイネーブルになる。イネーブルになると、データ入力センス増幅器は、読み取りトランザクションのデータフェーズの間に提供されるデータを取得することができる。従って、要求エージェントのデータ入力センス増幅器は、読み取りトランザクションのデータフェーズが終了したときに、出力制御信号に従ってディセーブルになる。  (もっと読む)

(もっと読む)

1 - 10 / 10

[ Back to top ]