Fターム[5B061GG02]の内容

バス制御 (3,799) | システム構成 (311) | データバスを複数個有するもの (178) | 階層バス (49)

Fターム[5B061GG02]の下位に属するFターム

レジデントバスを有するもの (7)

Fターム[5B061GG02]に分類される特許

1 - 20 / 42

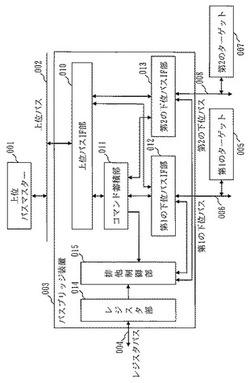

バスブリッジ装置及びデータ処理システム

【課題】スプリットトランザクション方式のバスブリッジ装置において、複数の下位バス間の排他制御を実現する。

【解決手段】排他制御部015は、下位バスIF部による下位バスへのアクセス状況を監視し、下位バスIF部による下位バスへのアクセス状況が所定の排他条件に合致している間は、次の実行対象のコマンドに基づいて下位バスへのアクセスを行う下位バスIF部に下位バスへのアクセスを保留させ、アクセス状況が排他条件に合致しなくなった際に、アクセスを保留させていた下位バスIF部による下位バスへのアクセスを開始させることで、複数の下位バス間の排他制御を実現する。

(もっと読む)

デバイスシステムおよび中継器

【課題】識別情報を効率よく用いて適切に通信制御を行なう。

【解決手段】ルーター#Anは、自身に接続されたデバイス52からのリクエストを受け付けたときには自身に割り当てられたTIDの1つをリクエストに格納してメモリーコントローラー37側に送信すると共に格納したTIDをリクエスト元のデバイス52に対応付けて記憶し(S100〜S140)、後段側のルーター#Anからのリクエストを受け付けたときにはメモリーコントローラー37側に転送し(S150)、メモリーコントローラー37側からのレスポンスを受け付けたときには該レスポンスに含まれるTIDを自身に割り当てられたTIDと照合しTIDが一致しないレスポンスは後段側のルーター#Anに転送し(S220,230)、TIDが一致するレスポンスは記憶した対応付けに基づいてリクエスト元のデバイス52に送信する(S240〜260)。

(もっと読む)

バスシステムおよびアクセス制御方法

【課題】各バスマスタからバススレーブへ複数のバスを経由してアクセスする場合であってもバスの使用効率の低下を抑制することができるバスシステムを提供することである。

【解決手段】本発明にかかるバスシステムは、複数のバスマスタ1_1〜1_4から少なくとも一つのバススレーブ5への、複数のバス2_1〜2_3を経由したアクセスを制御するバスシステムである。バス2_1〜2_3は各々、前段から入力される複数のアクセス要求16、17を調停し、当該調停により選択されたアクセス要求を次段へ出力する調停部8を備える。調停部8は、アクセス要求16、17がバスで待機した時間を差し引くことで次段へ出力されるアクセス要求29に含まれる許容待ち時間情報を更新する。

(もっと読む)

通信機器および通信システム

【課題】使い勝手の悪化を招くことなく適切なホスト間通信を実現することができる通信機器および通信システムを提供する。

【解決手段】第1の機器Cに設けた第1のPCI Expressスイッチ20のNTポート23と、第2の機器Dに設けた第2のPCI Expressスイッチ30のNTポート33と通信可能に接続する。第1の機器Cと第2の機器Dとの間で通信を行う際、第1のPCI Expressスイッチ20は、第1の機器Cが使用するアドレスとNTポート23が使用するアドレスとの間のアドレス変換を行い、第2のPCI Expressスイッチ30は、第2の機器Dが使用するアドレスとNTポート33が使用するアドレスとの間のアドレス変換を行う。

(もっと読む)

通信制御装置、ネットワーク、及びネットワークシステム

【課題】ネットワーク内の下位デバイスを、ノン・トランスペアレント接続された他のネットワークの上位デバイスから制御する。

【解決手段】複数の下位デバイスのうちの第1の下位デバイスからメモリアクセス要求を受け取り、メモリアクセス要求のアドレスが所定範囲のアドレスである場合は、メモリアクセス要求を、複数の下位デバイスのうちの、メモリアクセス要求のアドレスに応じた第2の下位デバイスに対する上位デバイスからの設定要求に変換する。

(もっと読む)

中継装置およびプロセッサーシステム

【課題】処理の順序が定められたリクエストを効率よく中継する。

【解決手段】マスターデバイス(M1)とスレーブデバイス(S1,2)とをツリー型に接続してなるプロセッサーシステムにおいて、通信経路の分岐点に配置される中継器(TB3)は、処理の順序が定められたインオーダーリクエスト1,2,3が順に入力される際には、リクエスト1を下位側に転送して転送済みリクエスト1と分岐先が同じリクエスト2を下位側に転送し(T5〜T7)、転送済みリクエスト1,2と分岐先が異なるリクエスト3を待機させて転送待ちとし(T7〜T13)、転送済みリクエスト1,2に対するレスポンス1,2が返ってきてから待機させたリクエスト3を下位側に転送するから(T14)、処理の順序が定められたリクエストを効率よく中継することができる。

(もっと読む)

データ分配装置

【課題】大量のデータを各部に適切に分配し、データ転送の高速化を図ることができる

ようにする。

【解決手段】PCI Express規格のスイッチ及びバスを介してデータの転送を受けるPCI Express規格のエンドポイント21を備える。バッファ22は、上位のスイッチ及びバスを介して転送されたデータをバッファリングする。分配制御回路23は、この転送されたデータを下位の複数の出力先である出力部に分配して転送する制御を行う。PCI Express規格のルートコンプレックス24及びスイッチ25は、分配制御回路23の制御によりデータの転送を行なう。

(もっと読む)

情報処理装置

【課題】周辺機能部が、複数のローカルメモリに対してアクセスするのか、一部のローカルメモリに対してアクセスするのかを制御可能にする。

【解決手段】情報処理装置のアドレス空間における第1ローカルメモリ及び第2ローカルメモリについての定義情報と、CPUの動作モードとに基づいて、周辺機能部からの通信要求に対応する、システムバスから第1ローカルバス及び第2ローカルバスへのルーティングを制御可能なシステムバスコントローラ(33)を設ける。また上記定義情報に基づいて、周辺機能部からの通信要求に対応する、第1ローカルメモリへのルーティングを制御可能な第1ローカルバスコントローラ(13)と、上記定義情報に基づいて、周辺機能部からの通信要求に対応する、第2ローカルメモリへのルーティングを制御可能な第2ローカルバスコントローラ(23)とを設ける。これによりローカルメモリへのアクセスの適正化を図る。

(もっと読む)

情報処理装置

【課題】オンチップバスにおけるメモリへのアクセス回数を少なくする。

【解決手段】情報処理装置(100)は、複数の転送元バス制御装置(1〜3)毎に設置された情報保持回路(7〜9)と、複数の情報保持回路(7〜9)を相互に接続可能な専用バス(10)と、複数の転送元バス制御装置(1〜3)毎に設置され、各転送元バス制御装置(1〜3)の接続先として専用バス(10)および階層バス(11)のいずれかを選択するバス選択回路(12〜14)と、を備えている。

(もっと読む)

リンクブリッジ

【課題】複数のバス間での情報転送のために改善されたシステムを提供する。

【解決手段】ホストプロセッサによりアクセスできるブリッジであって、第一バスと第二バスのインターフェース手段とともにリンクを持つ。第一インターフェースと第二インターフェースは、(a)第一バスと第二バスフォーマットと異なるフォーマットのリンクを介して情報をシリアルに出力する、(b)ブリッジを交差する宛先を表す特徴を持つペンディングのトランザクションに応答して第一バスと第二バスで初期交換を認めること、(c)該第一バスを介して通信するホストプロセッサは、(i)該第二バスの装置にアクセスするのに使用されるのと実質的に同じアドレスタイプを該第一バス上で使用するものであり、(ii)第一バスは、第二バスを使用することなく、該第二バス上のバスコンパティブルな装置の一つを調停する。

(もっと読む)

情報処理装置

【課題】 複数のバスにおいてバスマスタとは異なるバスに接続されているバススレーブが、データをデータリードごとに変更するデバイスについてのデバイスコントローラである場合であっても、デバイスからのデータを正確に読み出しつつ、バスマスタ側で、データライト要求に対するデータライトの完了を確実に検出する。

【解決手段】 バスマスタ12がバス1側に設けられ、IOデバイス23に対してデータライトおよびデータリードを実行するIOデバイスコントローラ22が第2バス側に設けられ、ブリッジ11,21がバス1とバス2とを接続している。そして、書き込み完了通知器13は、バス1側に設けられ、IOデバイスコントローラ22へのデータライト要求の後に、意図的にエラー発生させるための不良データリード要求をIOデバイスコントローラ22へ発行する。

(もっと読む)

スレーブカードをバスシステムに接続する方法

スレーブカード(20)を第1のバスシステム(30)に接続する方法と、当該方法を実施するための構成(18)が提案される。本方法では、信号がスレーブカード(20)から第1のバスシステム(30)を介してCPU(28)へと転送され、各スレーブカード(20)にはマスタ(22)が割り当てられ、信号の伝送は、各スレーブカード(20)から、割り当てられたマスタ(22)を介して行われる。 (もっと読む)

複合型計算機システムの管理方法及び複合型計算機システム

【課題】計算機に電源を投入する際に、計算機に割当てるPCIツリーの構成が完了していることを保証する。

【解決手段】複数の計算機をPCIインターフェースで接続するPCIスイッチと、PCIスイッチに接続する複数のPCIデバイスと、計算機の制御を行う装置制御部と、PCIデバイスと前記計算機の割り当てを制御するPCIマネージャと、を備えて、装置制御部が、計算機に電源を投入してOSを起動するステップと、装置制御部が計算機に割当てられたPCIツリーの識別子と、PCIツリーの状態を示すPCIツリー管理情報とを前記PCIマネージャから取得するステップと、取得したPCIツリー管理情報が初期化未了を示す場合には、装置制御部が前記計算機の電源投入を再実行または電源投入を中止するステップと、PCI管理情報がPCIツリーの初期化完了を示す場合には、措置制御部が計算機への電源投入を実施するステップとを含む。

(もっと読む)

バス装置

【課題】複数のバスマスタから複数のバススレーブに同時に効率よくアクセスすることが可能なバス装置を得る。

【解決手段】スレーブ分配部4−1〜4−nは、複数のバスマスタ2−1〜2−nからの転送データをバススレーブ3−1〜3−m毎に分配する。サブバス5−1〜5−mは、分配されたデータをバススレーブ3−1〜3−m毎に複数保持し、その中からバススレーブ3−1〜3−m毎に最も優先度の高いデータを抽出して転送する。読み出しデータ選択部6は、複数のバススレーブ3−1〜3−mからの転送データをバスマスタ2−1〜2−n毎に分配する。読み出しデータ格納部7−1〜7−nは、読み出しデータ選択部6で分配されたバスマスタ2−1〜2−n宛のデータを保持する。

(もっと読む)

I/Oデバイス、ホストコントローラおよびコンピュータシステム

【課題】ホストコントローラの端子数を増やさずに複数のI/Oデバイスを接続できるコンピュータシステムを提供する。

【解決手段】I/Oデバイスは、第1のバスと第2のバスと、モード設定手段と、デバイス番号設定手段を備え、動作モードがマスタモードに設定されたI/Oデバイスはコマンド応答や割り込みの調停を行う。これによりブロードキャストコマンドに対する応答の衝突やデータ転送と割り込みの衝突を起こさずに、ホストコントローラと複数のI/Oデバイスを含むコンピュータシステムを構成することができる。

(もっと読む)

データ転送システム

【課題】データ端子が1つのマスタコントローラを用いた転送システムでも、同一アドレスなどを有するスレーブデバイスとの間でアドレスを衝突させることなくデータ転送が可能なデータ転送システムを提供すること。

【解決手段】本発明一例のデータ転送システムは、スレーブデバイスが接続されるクロック線とデータ線を有する複数のIICバスと、これら複数のIICバスが並列に接続されたIICバススイッチと、中央制御ユニットからのクロック信号を前記IICバススイッチに送り、前記スレーブデバイスからのデータ信号を受けるマスタコントローラと、前記IICバススイッチに接続された複数のIICバスの1つを選択するチャンネル選択信号を前記IICバススイッチに供給する入出力コントローラと、を有する。

(もっと読む)

バス結合装置、ならびに割り込み制御ための方法およびプログラム

【課題】本発明により、演算処理装置の負荷軽減およびシステム全体の性能向上が可能とする。

【解決手段】第1のバスを介して結合された複数の入出力装置から、演算処理を行う演算処理装置に対して発行される割り込み処理要求を受信し、前記割り込み処理要求を行った前記入出力装置にアクセスして前記割り込み処理要求の要因を表す割り込み要因情報を取得し、第2のバスを介して結合された前記演算処理装置に対する割り込みを許可するか否かを、各前記入出力装置に対して各々の割り込み要因ごとに定めた割り込みマスク情報を保持し、前記割り込み処理要求を行った入出力装置と、取得された割り込み要因との組に対する割り込みが許可されているとき、前記割り込み処理要求を行った入出力装置が前記取得された割り込み要因に基づき前記割り込み処理要求を行っていることを表す割り込み情報を前記演算処理装置に対して通知する。

(もっと読む)

ディスクの搭載システム

【課題】本発明はディスクの搭載システムに関し、SATAディスクを用いた場合であっても、それぞれのエクスパンダから双方のSATAディスクにアクセスすることができるディスクの搭載システムを提供することを目的としている。

【解決手段】ディスクへのデータの書き込みと読み出しを制御する一対のコントローラであって、お互いが信号線で接続されたもの30と、前記対応するコントローラ30と接続され、2つの入出力ポートを持つ一対のエクスパンダであって、お互いが信号線で接続されたもの15と、前記エクスパンダ15とその一方の対応する入出力ポートが接続されると共に、他方の入出力ポートはそれぞれ第1及び第2のエクスパンダとたすきがけで接続された一対のマルチプレクサ35と、これらマルチプレクサ35を介して接続されたSATAディスク25より構成される。

(もっと読む)

バスインタフェースアダプタ、データ転送方法、データ転送システム及び情報処理装置

【課題】 プロセッサバスの負荷を軽減するとともに、データの高速転送を可能とする。

【解決手段】 バスインタフェースアダプタ10が、プロセッサ20からのリクエストの受信やプロセッサ20へレスポンスの送信を行なうプロセッサバスインタフェース制御部11と、各プロセッサ20のキャッシュラインの物理アドレス及び/又はキャッシュステータスを有する履歴テーブルを記憶する履歴テーブル記憶部14と、履歴テーブルを参照する履歴テーブル制御部15と、プロセッサバスインタフェース制御部11で受信されたリクエストの内容及び/又は履歴テーブル制御部15での参照の結果にもとづき、プロセッサ20とシステムメモリ40との間でデータの転送を行なうリクエスト監視部16とを備えた。

(もっと読む)

データ転送装置および方法

【課題】 システムバスとローカルバスの間で高速にデータを転送するデータ転送装置を提供する。

【解決手段】 バスブリッジ101がシステムバス132とローカルバス137との間に接続され、システムバス132上で、CPU133とI/O機器136と主記憶装置135との間で転送されるデータを連想メモリ制御部105を介して連想メモリ106に保持し、ローカルバス137上のI/O機器138からこのデータへのアクセスが生じた場合、連想メモリ106からI/O機器138にデータを転送する。従って、I/O機器138から主記憶装置135へのデータ転送要求が生じたとき、このデータが連想メモリ106に保持されていればシステムバス132上でバスサイクルが発生しないので、高速にデータを転送することができる。

(もっと読む)

1 - 20 / 42

[ Back to top ]