Fターム[5B065CS05]の内容

外部記憶装置との入出力 (22,430) | 入出力制御−データ操作 (234) | 直並列変換 (5)

Fターム[5B065CS05]に分類される特許

1 - 5 / 5

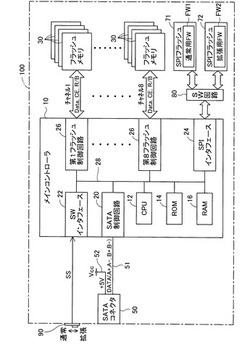

記憶装置

【課題】記憶部用のソフトウェアが破損されて、データの読み書きが不可能となることを防止する。

【解決手段】記憶装置は、データを不揮発的に記憶可能なフラッシュメモリ30と、フラッシュメモリ30へのデータの読み書きを制御するためのメインコントローラ10と、通常用ファームウェアFW1と拡張用ファームウェアFW2とを個別に格納するSPIフラッシュ71,72と、メインコントローラ10によりアクセスし得るSPIフラッシュ71,72を切り替えるSW回路80とを備える。

(もっと読む)

同時データ操作が可能なDMAエンジン

【課題】DMAコントローラ/エンジンによって管理される直接メモリアクセス(DMA)・チャネルを介して転送されるデータ上で、複数のデータ操作オペレーションを同時に実行するための方法およびデバイスを提供する。

【解決手段】DMAコントローラ内部で動作する制御データブロック(CDB)プロセッサは、CDBを読み出し、CDBの内容に従ってデータの読み出し、データ操作オペレーションおよびデータの書き込みを設定してもよい。データがDMAコントローラを通して導かれる間に、例えばハッシング、HMAC、フィルパターン、LFSR、EEDP検査、EEDP生成などの複数のデータ操作オペレーションをデータ上で同時に実行してもよい。データ操作オペレーションを実行するデータ変更エンジンは、データ操作オペレーションの間に外部メモリへのアクセスを回避するために局所RAMを使用する、DMAコントローラ上で実施されてもよい。

(もっと読む)

フラッシュメモリシステム及び同システムに組み込まれるフラッシュメモリモジュール

【課題】多数のフラッシュメモリに並列にアクセスできるフラッシュメモリシステムを簡単に設計する。

【解決手段】ホストシステムと通信するフラッシュメモリコントローラ12に、1個以上のフラッシュメモリモジュール14、14、…が、たった3本の信号線をもつシリアルインタフェース16を介して接続される。各フラッシュメモリモジュール14は、パラレルインタフェース34をもつ複数個のフラッシュメモリ32、32、…と、シリアルインタフェース16とパラレルインタフェース34との間の信号形式変換を行うシリアル・パラレル変換回路30とを備え、フラッシュメモリ32、32、…の個数が固定された1個のモジュール又は1個のパッケージとして構成される。必要な記憶容量に応じて、フラッシュメモリコントローラ12に接続されるフラッシュメモリモジュール14、14、…の個数を選択できる。

(もっと読む)

データ変換装置とデータ変換方法と電子装置

【課題】 異なるデータ転送方式の2つの装置間で両装置とのデータ送受信の転送方式を変換して両装置間のデータ送受信を可能にし、一方の装置とのデータ送受信時に通信エラーが発生しても再送できるようにする。

【解決手段】 ホスト装置2とパラレルでデータ送受信するパラレルインタフェース制御部14と、HDD3とシリアルでデータ送受信するシリアルインタフェース制御部16と、パラレルインタフェース制御部14又はシリアルインタフェース制御部16で受信したデータを保持する第1バッファメモリ12と第2バッファメモリ13と、その保持されているホスト装置2から受信したデータをシリアルインタフェース制御部16によってHDD3へ送信させ、上記保持されているHDD3から受信したデータをパラレルインタフェース制御部14によってホスト装置2へ送信させる主制御部10を有する。

(もっと読む)

ホストコントローラで独立および同時データ転送を行う方法および装置

アクセス検出器が、シリアルストレージデバイスとインタフェースする複数のシリアルポートのうちの1つへのアクセスのアクセスタイプを検出する。このアクセスは、パラレルチャネルのタスクファイルレジスタを介してパラレルストレージデバイスとインタフェースする複数のパラレルチャネルのうちの1つを目的とする。マッピング回路が、シリアルポートをパラレルチャネルにマッピングする。ステートマシーンは、アクセスタイプとマッピングされたシリアルポートに基づいてパラレルチャネルのうちの1つからの応答をエミュレートする。 (もっと読む)

1 - 5 / 5

[ Back to top ]