Fターム[5B125EH00]の内容

リードオンリーメモリ (43,397) | 検出構成 (453)

Fターム[5B125EH00]の下位に属するFターム

電源電圧検出 (76)

高電圧発生回路の電圧検出 (91)

負電圧発生回路の電圧検出 (10)

1メモリセルのしきい値検出 (125)

ワード線の電圧、電流検出 (15)

ビット線のセンスアンプ以外の電圧電流検出 (29)

ソース線の電圧、電流検出 (22)

温度検出 (52)

アドレス遷移検出 (17)

入力データ遷移検出 (2)

Fターム[5B125EH00]に分類される特許

1 - 14 / 14

不揮発性半導体記憶装置

【課題】書き込み動作におけるフェイルビットの許容数を増加し、かつ書き込み動作の高速化を図る。

【解決手段】不揮発性半導体記憶装置は、複数のメモリセルが配置されたメモリセルアレイ5と、メモリセルアレイに対し、ページ毎にプログラムおよびベリファイを実行する書き込み制御回路16と、ベリファイ結果のデータを保持するラッチ回路10,12と、ページを複数の領域に分割し、各領域のアドレスを順に選択するアドレス制御回路15と、アドレス制御回路により選択される領域毎に、ラッチ回路に保持されたデータに従ってフェイルビット数をカウントし、フェイルビット数が許容ビット数以下であるか否かを判定するスキャンを実行するスキャン制御回路14と、複数の領域のうちフェイルビット数が0であるノーフェイル領域のアドレスを保持するアドレスラッチ回路20と、を具備する。

(もっと読む)

電磁波照射検出回路、半導体装置、ICカード

【課題】 利便性を低下させることなく高セキュリティ性の実現が可能な半導体装置を提供する。

【解決手段】 一端に電源電圧VCC、他端に接地電圧が印加された2つの直列回路SC1及びSC2を有する。各直列回路は、抵抗とフラッシュメモリトランジスタとで構成される。コンパレータ71の反転入力端子72imには第1対象電圧VOUT1が、反転入力端子72ipには第1対象電圧VOUT2が夫々入力され、両者の大小関係に基づいて検出信号ERRが出力される。電磁波が照射されていない状態の下での検出信号ERRの電圧レベルと、電磁波が照射された状態下での検出信号ERRの電圧レベルとが変化するように、両抵抗R1及びR2の抵抗値、及び両フラッシュメモリトランジスタ71a及び71bの閾値電圧を所定の条件下に調整する。

(もっと読む)

負電位モニターパッド制御回路及びそれを備えた不揮発性メモリ

【課題】複数の負電位をモニターするパッドを共有化し、チップ面積の増大を防ぎ、且つ、同測テストにおける同測チップ数の減少を最小限に抑える負電位モニターパッド制御回路及びそれを備えた不揮発性メモリを提供することを目的とする。

【解決手段】第1の負電位発生手段100と、第1のモニタースイッチ手段105と、第2の負電位発生手段110と、第2のモニタースイッチ手段115と、負電位モニターパッド30とを有し、第1及び第2のモニタースイッチイネーブル信号により第1及び第2のモニタースイッチ手段105、115のオン・オフ制御を行うことで、第1及び第2の負電位発生手段と負電位モニターパッドとの接続を制御する。

(もっと読む)

NAND型フラッシュメモリ装置及びメモリデバイス

【課題】データの書き込み時又は読み出し時にビット線の充電のための電流を低減させ、かつ、ビット線の充電のためのピーク電流が一定の条件の下では動作を高速とすること。

【解決手段】本発明のNAND型フラッシュメモリ装置100は、同時書き込みデータ単位内の前記複数のメモリセルにデータを転送する時に前記データの“1”データ及び“0“データの数に基づいて前記“1”データ又は前記“0“データの極性を反転させるか否かを判断し、前記データを反転して前記メモリセルアレイ101に転送する場合に前記極性を反転したことを示す反転フラグビットを前記データに追加するデータ反転制御部108を具備する。

(もっと読む)

メモリ制御回路

【課題】電圧の印加を検出し、不揮発性メモリに対して当該電圧のレベルに応じた処理を行うことが可能なメモリ制御回路を提供することを目的とする。

【解決手段】不揮発性メモリを書き込みモードに設定するための書き込みモード電圧(>電源電圧)の印加の有無を検出する検出回路と、検出回路が書き込みモード電圧の印加を検出した場合、不揮発性メモリに対し、不揮発性メモリの書き込み動作を許可するための書き込み許可電圧と、書き込みモード電圧を基に得られる不揮発性メモリを構成するメモリセルに印加するべき書き込み電圧と、を出力する出力回路と、を備えたことを特徴とする。

(もっと読む)

電流消耗を減少させる内部電源電圧発生回路を有するマルチチップ半導体メモリ装置

【課題】不要なアクティブ内部電源電圧発生回路の電流消耗を減少させることができるマルチチップ半導体メモリ装置を提供する。

【解決手段】電流消耗を減少させる内部電源電圧発生回路を有するマルチチップ半導体メモリ装置であって、それぞれが独立的に外部電源電圧を内部電源電圧に変換するアクティブ内部電源電圧発生回路を含み、所定のチップイネーブル信号を共有する複数のメモリチップを備える。前記複数のメモリチップのいずれか一つのメモリチップが所定のアクティブ区間にある間、他のメモリチップの前記アクティブ電圧変換回路はディスエーブルされる。本発明のマルチチップ半導体メモリ装置によれば、内蔵される全てのメモリチップのアクティブ内部電源電圧発生回路がイネーブルされる従来技術に比べ、消耗電力がめっきり減少する。

(もっと読む)

メモリ制御装置

【課題】 EEPROM等の不揮発性メモリへのデータの書込回数を効率的に減少させ、寿命を延長させる。

【解決手段】 メモリ制御装置1の制御部11は、不揮発性メモリ2に書き込むべきデータを揮発性メモリ12のデータ領域に一旦書き込む。このとき制御部11は、書き込んだデータを示すIDを揮発性メモリ12のID領域に書き込む。不揮発性メモリ2にデータを書き込むとき、制御部11は、ID領域に登録されたIDに基づいて、データ領域に書き込まれたデータから同一のブロックに書き込まれるデータを特定し、このとき特定されたデータを不揮発性メモリ2に一括して書き込む。

(もっと読む)

半導体集積回路装置

【課題】動作信頼性を向上出来る半導体集積回路装置を提供すること。

【解決手段】第1電源V1と、前記第1電源V1と異なる電圧の第2電源V2とを用いて動作する半導体集積回路装置1であって、前記第1電源V1が所定の電圧を超えたことを検知する第1検知回路10と、前記第2電源V2が所定の電圧を超えたことを検知する第2検知回路11と、前記第1電源V1を用いてアナログ動作するアナログ回路30の動作状況をチェックし、正常に動作しているか否かを示す制御信号CHECKを出力するチェック回路20とを具備し、前記第1検知回路10の検知レベルは前記制御信号CHECKに基づいて決定され、前記第1、第2検知回路10、11における検知結果に応じてパワーオンリセット信号POR1が出力される

(もっと読む)

半導体装置

【課題】 エージングデバイスを用いてμバッテリーの寿命を延長する。

【解決手段】 ソースが入力端に接続され、第1の寿命τ1でオンし、第2の寿命τ2(>τ1)でオフする第1のエージングデバイス31aと、ソースが入力端に接続され、ゲートがエージングデバイス31aのドレインに接続され、ドレインがエージングデバイス31aのゲートに接続され、第3の寿命τ3でオンし、第4の寿命τ4(>τ3)でオフする第2のエージングデバイス31bと、エージングデバイス31aのドレインと出力端との間に挿入され、エージングデバイス31aがオンの時にオンし、エージングデバイス31bがオンの時にオフする第1のスイッチ素子33aと、エージングデバイス31bのドレインと出力端との間に挿入され、エージングデバイス31bがオンの時にオンし、エージングデバイス31aがオンの時にオフする第2のスイッチ素子33bとを備えた。

(もっと読む)

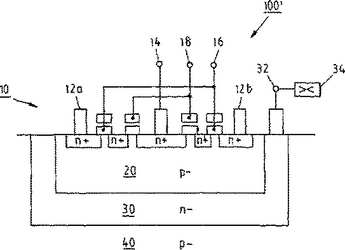

光照射から保護される電子メモリ構成要素

いわゆる光照射の形態をとる光入射が直接検出されるか、または不感時間なしに直ちに感知される(=チップ発展への寄与)ように、少なくとも1つのドープ受容基板(20)中に埋め込まれおよび/または填め込まれる少なくとも1つのメモリ・セル・マトリックス(10)を備える、電子メモリ構成要素(100または100’)を発展させるために、受容基板(20)は、メモリ・セル・マトリックス(10)から離れたその表面の少なくとも1つが、少なくとも部分的におよび/または受容基板(20)とは反対のドープ型の少なくとも1つの上部/保護基板(30)によって覆われおよび/または囲まれること、および基板(20または30)の少なくとも1つ、たとえば受容基板(20)および/または特に上部/保護基板(30)が、光入射時に生成される電荷キャリアによって生じる電圧または電流の検出のために少なくとも1つの回路構成(それぞれ24または34)に接触(12aまたは12b)または接続(32)することが提案される。  (もっと読む)

(もっと読む)

データ記憶及び再生装置

データ記憶及び再生装置は、記憶媒体(通常はフラッシュメモリ回路)の性能の進化の測定値を使用して、記憶媒体のある領域からの取り出しの誤り率を予測する。予測は、データの格納に先立ちデータを符号化するECCを動的に選択するための基礎として使用される。前記情報が与えられると、所定の復号後誤り率しか生成しないと予測される最速の符号化可能なECCが選択されるように、使用可能な複数のECCからそのECCが選択される。このように、データを装置に送信する速度が最大にされ得ると同時に、復号後の予測される将来に、許容レベルを下回る誤り率を保持することができる。復号時、通常は音声データまたはビデオデータであるデータは、所定の速度で復号され、再生される。別の実施形態では、データは、複数のECCを使用して一緒に格納され、ECCは、出力データ転送速度が最大にされ、または再生時の消費電力が最低限に抑えられ得るように、復号用に動的に選択される。  (もっと読む)

(もっと読む)

半導体記憶装置および半導体記憶装置の制御方法

【課題】 レプリカビット線の動作でリード動作タイミングを決める単一ビット線方式の半導体記憶装置において、トランジスタ特性にばらつきが発生した場合であっても、アクセス時間の増大や回路サイズの増大を防止しつつ、データ読み出しエラーの発生確率を減少させることが可能な半導体記憶装置および半導体記憶装置の制御方法を提供することである。

【解決手段】 レプリカメモリセルトランジスタのゲート長が、メモリセルトランジスタのゲート長に比して長い値に設定されることで、レプリカメモリセルトランジスタRM1乃至RMnの電流駆動能力分布DRの分布中心mRが、メモリセルトランジスタBM1乃至BMnの電流駆動能力分布DNの分布中心mNに対して低くなるように設定される。ラッチ制御信号LCSの発信タイミングに比して通常データ線DLの下降開始時間に遅れが発生する確率を低くすることができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】 データ保持回路が保持するデータ状態をコマンド入力により外部に出力可能とした不揮発性半導体記憶装置を提供する。

【解決手段】 不揮発性半導体記憶装置は、電気的書き換え可能な不揮発性メモリセルが配列されたメモリセルアレイと、前記メモリセルアレイの読み出し又は書き込みデータを保持するデータ保持回路と、前記データ保持回路に接続されてデータ保持回路が保持するデータの“0”又は“1”のビット数を検出するデータビット検出回路と、データ書き込み、消去及び読み出しの制御を行うと共に、前記データビット検出回路により検出されたビット数データが転送保持されるデータビットレジスタを備えて、コマンド入力により前記データビットレジスタが保持するビット数データを入出力端子に出力する内部コントローラと、を有する。

(もっと読む)

コピー防止機能付半導体集積回路装置

【課題】 従来、コピー防止機能付半導体集積回路装置における暗号記憶・一致検出回路は、構成が簡単で回路素子数が少ないものとすることが難しかった。

【解決手段】 記憶手段104と、入力手段101,102と、出力手段105と、入力情報を所定の暗号情報と比較しその比較結果に基づく一致/不一致検出信号を該出力手段に供給する暗号記憶・一致検出回路103とを具備し、該暗号記憶・一致検出回路は、一端から一致検出信号が出力され他端が第1の電源供給線に接続され、複数の基本回路が直列接続されたビット直列回路と、該ビット直列回路の一端と第2の電源供給線との間に接続され該ビット直列回路がオンの時の端子間電圧がオフの時の端子間電圧よりも高くなる負荷手段とを有し、該複数の基本回路はそれぞれ、その両端間が、制御入力端に供給される入力情報の信号が第1の論理値の時にオンになり該第1の論理値を反転した値の時に不揮発的にオフ又はオンの一方になる。

(もっと読む)

1 - 14 / 14

[ Back to top ]