Fターム[5F038BB10]の内容

Fターム[5F038BB10]に分類される特許

1 - 6 / 6

基準電圧発生回路装置

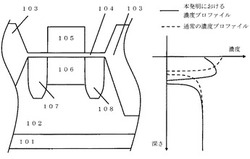

【課題】デプレッション型MOSトランジスタとエンハンス型MOSトランジスタによって形成される基準電圧発生回路装置の面積を大きくすることなく基準電圧の温度特性を向上させる。

【解決手段】デプレッション型MOSトランジスタの濃度プロファイルを、第一導電型チャネル領域の基板表面側の不純物濃度が薄く、かつ前記第一導電型チャネル領域と第二導電型の基板領域もしくはウェル領域にて形成されるPN接合付近の前記第一導電型チャネル領域の不純物濃度が濃くなるように制御することで基準電圧の温度特性を向上させる。

(もっと読む)

ドライバIC、電気光学装置及び電子機器

【課題】パネルへの接続のための信号線引き回しが少なく、かつチップサイズの縮小を図ったドライバIC等を提供する。

【解決手段】ドライバIC100の長手方向にて三分割し、中央の第1領域100Aにはデータ線ドライバ130を、第2領域100Bには第1走査線ドライバ142Aを、第3領域100Cには第2走査線ドライバ142Bを、それぞれドライバICの長辺100Dに沿って配置し、他の長辺100Eに沿ってインターフェース領域102を配置する。第1領域には、昇圧回路140AとRAM110とを配置する。第2領域には、第1電源回路140Bを配置する。第3領域には、第2電源回路140Cを配置する。第1領域に配置した第1電源回路からの内部基準電位Vrefを、第2領域を経由して、第3領域に配置した第2電源回路内の内部電源電位生成回路140Fに伝送する。内部基準電位は、ボルテージフォロアを介して電源配線層に供給する。

(もっと読む)

半導体集積回路装置

【課題】安定した内部電源電圧を発生できるように、負荷電流の変動に対して高速応答するとともに、十分な駆動電流を供給できるレギュレータ回路を提供する。

【解決手段】レギュレータ回路30aは、基準電圧VREFと内部電源電圧VINTとの差を検知増幅するプリアンプ回路32aと、プリアンプ回路32aの出力の振幅を制限するクランプ回路34aと、振幅制限されたプリアンプ回路32aの出力を増幅するメインアンプ回路36aと、メインアンプ回路36aの出力に応じて、内部電源電圧VINTを出力するドライバ回路38とを含む。内部電源電圧VINTが急激に変動しても、クランプ回路34aの効果によって、レギュレータ回路30aが発振することはない。

(もっと読む)

半導体集積回路装置、半導体集積回路装置のテスト方法、バーインストレス&D/Sに用いられるプローブカード

【課題】最適なバーインストレスをサンプルに印加する。

【解決手段】半導体集積回路装置50には、バーインカウンタ1、制御部2、及び被テスト回路3が設けられる。バーインカウンタ1は、半導体記憶装置としての被テスト回路部3に印加されるバーインストレスを把握するために設けられたものである。バーインカウンタ1は、被テスト回路3に印加されるバーインストレス(印加温度及び印加電圧)を把握し、バーインストレスをカウントアップ(モニター)して、印加温度、印加電圧、及びバーインストレス時間に対応したバーインストレス情報を外部に出力する。

(もっと読む)

半導体集積回路

【課題】小型化および消費電力の低減を図ることができる。

【解決手段】半導体集積回路1は、半導体集積回路1の各種機能を構成する複数のアナログ回路(補正対象回路)2、2、・・・と、各アナログ回路2が備える素子(本実施の形態ではトランジスタ、抵抗、キャパシタ)の製造ばらつき温度変化等による現在の素子特性の情報を持たせるためのモニタデータを供給する1つの制御部3とを有している。制御部3は、半導体集積回路1の素子の製造ばらつきと温度のモニタリングを一手に引き受ける。

(もっと読む)

CMOSデバイスの過度の漏れ電流の検出

相補型MOS(CMOS)環境内部の金属酸化膜半導体(MOS)トランジスタ(36,46)のドレイン/ソース間の過度の漏れ電流を検出するためのシステム(10,90)と、装置(12,30,40,50,60,70)と、方法(100)とを開示する。前記MOSトランジスタの補完として負荷制御(32,42)を配置する。比較器(34,44)は、前記負荷制御及び前記MOSトランジスタに電気的に接続されるとともに、しきい値を超える漏れ電流の検出を表す出力信号を生成する。過度の漏れ電流を示す受信された出力信号に応答して、前記CMOS環境へのダメージを阻止するためにシステム電圧/周波数を調整する。  (もっと読む)

(もっと読む)

1 - 6 / 6

[ Back to top ]