Fターム[5F064EE28]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 多層配線 (2,699) | 両面パターン (4)

Fターム[5F064EE28]に分類される特許

1 - 4 / 4

半導体電力増幅器

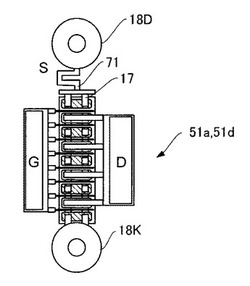

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

無線集積回路装置の製造方法、無線集積回路装置及び電子機器

【課題】効率的な動作試験ができる無線集積回路装置の製造方法、無線集積回路装置及び電子機器等を提供すること。

【解決手段】無線集積回路装置の製造方法は、ウェハー上に複数の無線集積回路装置100を形成し、複数の無線集積回路装置100のうちの少なくとも1つの無線集積回路装置を送信モード無線集積回路装置100aに設定し、複数の無線集積回路装置100のうちの送信モード無線集積回路装置100aを除く少なくとも1つの無線集積回路装置を受信モード無線集積回路装置100bに設定する。送信モード無線集積回路装置100aの送信回路により動作試験用の送信データを送信し、受信モード無線集積回路装置100bの受信回路により動作試験用の送信データを受信して動作試験を実行する。動作試験の完了後に複数の無線集積回路装置100をダイシングする。

(もっと読む)

回路、回路設計方法、および回路構成素子

【課題】 この発明は、半導体LSIチップ上およびプリント回路基板上で、半導体LSIチップ上のインバータのスイッチング速度に匹敵する電気による超高速での情報処理や信号伝送を可能とするとともに、不要電磁波の発生と漏洩を抑止する。

【解決手段】 回路システムを構成するスイッチング回路の機能を孤立電磁波の励起作用とし、前記スイッチング回路に接続される電源分配回路に、特性インピーダンスが信号伝送用線路に比べて充分低く、線路を構成する絶縁材料の誘電体損失が比較的大きい低インピーダンス損失線路を使用する。前記低インピーダンス損失線路と前記スイッチング回路の間に低インピーダンス損失線路はない線路が接続される場合は、該線路の長さが前記孤立電磁波の波長の20倍以下であって、前記孤立電磁波が該線路中を往復する時間内は前記スイッチング回路の状態を変化させないように回路が形成される。

(もっと読む)

半導体記憶装置

【課題】本発明は、抵抗変化型メモリ素子をセルに用いたマルチチップパッケージにおいて、高抵抗素子を利用することにより、工程数の増加を必要とすることなく、積層された複数のメモリチップを識別できるようにする。

【解決手段】たとえば、同一パッケージ内に積層された複数のメモリチップは、それぞれ、チップアドレス識別回路150を備える。各チップは、相互に接続される第1のメモリ位置検知用パッドのテストパッドTT,TB間に、それぞれ、メモリセルと共通のプロセスにより同時に形成される可変抵抗素子CCを有する。チップアドレス識別回路150は、各チップの可変抵抗素子CCを高抵抗化することにより、チップの積層順に応じて、テストパッドTTにそれぞれ現れる電圧を、比較器154にて、メモリ位置検知回路156からの既知の比較信号と比較することで、各層のメモリチップの位置を検知する。

(もっと読む)

1 - 4 / 4

[ Back to top ]