Fターム[5F083JA47]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 酸化物導電体 (2,345) | ドープにより導電性を有するもの (18)

Fターム[5F083JA47]に分類される特許

1 - 18 / 18

メタルブリッジ型記憶装置

不揮発性半導体記憶装置及びその製造方法

【課題】 書き込み動作及び消去動作の両方の特性向上を図る。

【解決手段】 実施形態による不揮発性半導体記憶装置は、半導体基板11と、半導体基板上に形成されたゲート絶縁膜12と、ゲート絶縁膜上に形成され、13族元素であるP型不純物を含有するポリシリコンからなり、下部膜13aと下部膜上に積層された上部膜13bとを有するフローティングゲート電極13と、フローティングゲート電極上に形成された電極間絶縁膜16と、電極間絶縁膜上に形成されたコントロールゲート電極17と、を具備し、上部膜におけるP型不純物の濃度又は活性化濃度は、下部膜におけるP型不純物の濃度又は活性化濃度より高い。

(もっと読む)

半導体装置及びその製造方法

【課題】容量絶縁膜の絶縁性の劣化が生じにくく、かつ容量プレート電極の厚みが薄い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、互いに異なる平面面積を持つメモリセル部と補償容量部とを単一の基板上に備える。メモリセル部と補償容量部とは、同一構成の容量プレート電極を含む。容量プレート電極は、ボロンドープシリコンゲルマニウム膜と金属膜とを含む積層構造を有している。

(もっと読む)

可変抵抗素子、及び、不揮発性半導体記憶装置

【課題】 電極材料に対する制約が緩和され、製造プロセス上容易な可変抵抗素子、及び、当該可変抵抗素子を備えた不揮発性半導体記憶装置を提供する。

【解決手段】

可変抵抗素子2は、第1電極12aと第2電極14の間に抵抗変化層13、及び、第2電極と接する低抵抗層14を挟持して構成される。低抵抗層14は、抵抗変化層13を構成する金属酸化膜と同一の金属元素の酸化膜であり、且つその抵抗値が前記抵抗変化層よりも低くなるように低抵抗化する処理がされている。低抵抗層14は、例えば、金属酸化膜に不純物をドーピングし、キャリア濃度を増加させることにより形成される。或いは、低抵抗層14は、n型の金属酸化物の場合、金属酸化膜の酸素欠損濃度を抵抗変化層13よりも高濃度にすることにより形成される。

(もっと読む)

強誘電体材料層の製造方法、薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】強誘電体材料層の電気特性(例えば、高残留分極特性、低リーク電流特性など。)をより一層向上させることが可能な強誘電体材料層の製造方法を提供する。

【解決手段】熱処理することにより強誘電体材料となるゾルゲル溶液を準備する第1工程と、基材上に前記ゾルゲル溶液を塗布することにより、前記強誘電体材料の前駆体組成物層を形成する第2工程と、前記前駆体組成物層を120℃〜250℃の範囲内にある第1温度で乾燥させる第3工程と、前記前駆体組成物層を前記第1温度よりも高く、かつ、150℃〜300℃の範囲内にある第2温度に加熱した状態で前記前駆体組成物層に対して型押し加工を施す第4工程と、前記前駆体組成物層を前記第2温度よりも高い第3温度で熱処理することにより、前記前駆体組成物層から強誘電体材料層を形成する第5工程とをこの順序で含む強誘電体材料層の製造方法。

(もっと読む)

キャパシタ素子とキャパシタ素子の製造方法および半導体装置

【課題】リーク電流の低減と静電容量の増加の両立を実現するキャパシタ素子とキャパシタ素子の製造方法および半導体装置を提供する。

【解決手段】本発明のキャパシタ素子は、少なくとも上面が第一の窒化金属からなる第一電極と、酸化ジルコニウム膜からなる容量絶縁膜と、ボロン、アルミニウム、ガリウムのいずれかが不純物としてドープされた酸化亜鉛膜からなる第一のバリア膜と、少なくとも下面が第二の窒化金属からなる第二電極と、がこの順で積層されてなることを特徴とする。

(もっと読む)

金属酸化物抵抗率スイッチング層と共に使用する下部電極

金属酸化物抵抗率スイッチング層と共に使用する下部電極

専用のセレクタトランジスタが不要な自己選択式PCMデバイス

【課題】専用のセレクタトランジスタが不要な自己選択式PCMデバイスを提供する。

【解決手段】原子層堆積法(ALD)を使用して、亜鉛酸化物(ZnO)を層変化材料の上に堆積させることで、自己選択型記憶デバイスが形成される。ZnO/GST界面に形成されるダイオードは、PCMアーキテクチャ内で、整流能力と記憶能力の両方を示す。

(もっと読む)

抵抗変化メモリ

【課題】抵抗変化メモリに用いられる素子特性の劣化を抑制できる。

【解決手段】本発明の例に関わる抵抗変化メモリは、n型伝導性の第1のシリコン層と第1のシリコン層と接触する導電層36とを有する非オーミック素子30と、導電層36を介して非オーミック素子30に接続され、抵抗状態の可逆的な変化に応じてデータを記憶するメモリ素子と、を含み、配線L2(i)と配線L3(j)との間に設けられるセルユニットと、を具備し、シリコン層33は、ドナー不純物として、第1の元素41と第2の元素42とを含む。

(もっと読む)

抵抗変化メモリ

【課題】抵抗変化メモリに用いられる素子特性の劣化を抑制できる。

【解決手段】本発明の例に関わる抵抗変化メモリは、2つの配線L2(i),L3(j)と、少なくとも一方の端部に設けられる導電層36と2つの端部間に設けられるシリコン部とを有する非オーミック素子30と、導電層36を介して非オーミック素子30に接続され、抵抗状態の可逆的な変化に応じてデータを記憶するメモリ素子20とを含み、2つの配線L2(i),L3(j)間に設けられるセルユニットCUと、を具備し、非オーミック素子30は、シリコン部37内に、シリコンゲルマニウム領域39を有している。

(もっと読む)

不揮発性半導体記憶装置

【課題】周辺回路の占有面積の増大を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、ワード線WLと、ビット線BLと、ワード線WLとビット線BLとの各交差部に配置され可変抵抗素子R及び双方向ダイオードDにて構成されたメモリセルMと、一つのワード線WLを選択する第1デコーダ回路13と、一つのビット線BLを選択する第2デコーダ回路14と、選択されたワード線、非選択のワード線WL、選択されたビット線BL、及び非選択のビット線BLの電圧を各々制御する電圧制御回路15とを備える。可変抵抗素子Rは、印加される電圧の極性により抵抗値を変化させるように構成されている。電圧制御回路15は、選択されたワード線WLに電圧パルスを印加し且つ選択されたビット線BLの一端に所定容量のキャパシタ153を接続するように構成されている。

(もっと読む)

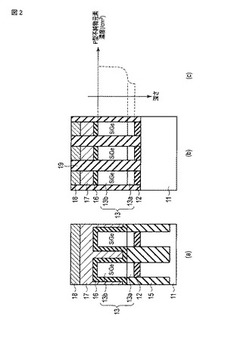

抵抗変化メモリ

【課題】p-i-nダイオードをその特性の劣化なしに薄くする。

【解決手段】本発明の例に係わる抵抗変化メモリは、第一方向に延びる第一導電線L2(i)と、第一方向に交差する第二方向に延びる第二導電線L3(j)と、第一導電線と第二導電線との間に直列接続されるメモリ素子17及び整流素子13,14,15から構成されるセルユニットCU2とを備える。メモリ素子の抵抗値は、メモリ素子に印加される電圧を制御することにより、少なくとも第一値と第二値との間で可逆変化させる。整流素子は、p型半導体層、n型半導体層及びこれらの間の真性半導体層から構成されるp-i-nダイオードである。p-i-nダイオードは、少なくともp型半導体層の真性半導体層側の端部及びn型半導体層の真性半導体層側の端部に拡散防止領域を有する。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】セット動作時において誤セット動作が生じることを効果的に抑制しつつ消費電力を抑制し、信頼性の高い不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】整流素子層21は、半導体層24と、半導体層24の一端側に設けられた電極層23と、半導体層24の他端側に設けられた電極層26と、電極層26と半導体層24の間に設けられた電極層25とを備える。半導体層24は、p+型半導体層24cと、n+型半導体層24aとを備える。電極層25は、半導体層24との間で格子整合のとれた材料にて構成されている。半導体層24は、電極層25を結晶核として結晶成長した構成を有する。

(もっと読む)

半導体記憶装置

【課題】外乱の影響を受け難く、微小なセル電流を効率よく検出することができるとともに低コストを実現する半導体記憶装置を提供することを目的とする。

【解決手段】平行に配置された複数の第1の行線と、前記第1の行線に交差する複数の列線と、前記第1の行線と前記列線との各交差部に配置された複数の記憶素子と、前記列線を介して前記第1の行線と対向する位置から前記列線の所定部まで前記第1の行線と平行に配置され前記列線と容量結合された複数の第2の行線と、前記列線の所定部を下層制御電極、この列線の所定部に上層で容量結合された前記第2の行線を上層制御電極とする電界効果トランジスタからなるセンスアンプとを備えたことを特徴とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】 電圧印加により電気抵抗が変化し、内蔵する整流性接合により、一方電極を基準電極として他方電極に正電圧を印加した時に流れる正バイアス電流が、他方電極に負電圧を印加した時に流れる負バイアス電流より大きい電流電圧特性を有する可変抵抗素子を備えてなるメモリセルを有する不揮発性半導体記憶装置において、メモリセルの読み出しディスターブを抑制する。

【解決手段】 メモリセルアレイ25の中からメモリセルを選択するメモリセル選択回路16,17と、読み出し動作において、選択メモリセルの可変抵抗素子に、他方電極に読み出し動作に応じた所定の正電圧が印加するように、メモリセル選択回路を介してメモリセルに電圧供給する電圧供給回路22と、他方電極から基準電極に流れる正バイアス電流の大小を検知して、選択メモリセルの記憶情報の読み出しを行う読み出し回路23と、を備える。

(もっと読む)

有機強誘電体キャパシタの製造方法、有機強誘電体キャパシタ、有機強誘電体メモリ、および電子機器

【課題】有機強誘電体材料を用い、低電圧駆動化を図ることができる有機強誘電体キャパシタの製造方法、有機強誘電体キャパシタ、および有機強誘電体メモリを提供すること。

【解決手段】下部電極3を形成する工程と、下部電極3上に、結晶性を有する有機強誘電体材料を含む液状材料4Aを塗布・乾燥して、記録層4の結晶化度よりも低い結晶化度で、非晶質状態の有機強誘電体材料を主材料として構成された低結晶化度膜4Bを形成する工程と、低結晶化度膜4Bの下部電極3と反対側の面上に、上部電極5を形成する工程と、低結晶化度膜4B中の有機強誘電体材料を結晶化して、記録層4を形成する工程とを有する。

(もっと読む)

導電性フィーチャへの接点を作る際の誘電体オーバーエッチングを低減するための方法

本発明の第1の好ましい実施形態において、導電性フィーチャが第1の誘電体エッチング停止層上に形成され、第2の誘電材料が導電性フィーチャ上およびその間に堆積される。第1の誘電体と第2の誘電体との間で選択的な導電性フィーチャへのバイアエッチングは、誘電体エッチング停止層上で停止し、オーバーエッチングを制限する。第2の実施形態において、複数の導電性フィーチャが減法的なパターン形成およびエッチングプロセスで形成され、誘電性充填材で満たされ、次に形成された表面が導電性フィーチャおよび誘電性充填材を同時露出する。誘電体エッチング停止層が表面に堆積させられ、次に第3の誘電体が誘電体エッチング停止層を覆う。第3の誘電体を貫通して接点がエッチングされると、この選択的エッチングは、誘電体エッチング停止層上で停止する。第2のエッチングが導電性フィーチャへの接点を作る。  (もっと読む)

(もっと読む)

1 - 18 / 18

[ Back to top ]